数字逻辑电路设计课程设计之数字电子钟

课程名称:数字电路逻辑设计课程设计

设计项目:数字电子钟

学生姓名:

同组人: 高爽

一 .设计目的

1.掌握组合逻辑电路、时序逻辑电路及数字逻辑电路系统的设计、安装、测试方法;

2.进一步巩固所学的理论知识,提高运用所学知识分析和解决实际问题的能力;

3.提高电路布局﹑布线及检查和排除故障的能力;

4.培养书写综合实验报告的能力。

二 . 设计要求

1.设计一个具有时、分、秒显示的电子钟(23小时59分59秒);

2.应该具有手动校时校分的功能;

3.应该具有整点报时功能:从59分51秒起(含59分51秒),每隔2秒发出一次蜂鸣,连续5次;

4.使用中小规模集成电路组成电子钟,并在实验箱上进行组装、调试;

5.画出框图和逻辑电路图,写出设计、实验总结报告。

三 . 设计原理

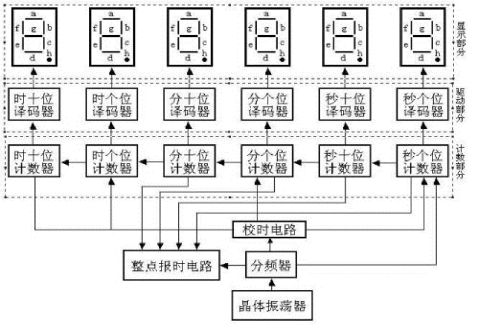

1.数字电子钟基本原理

数字电子钟的逻辑框图如下图所示。它由555集成芯片构成的振荡电路、分频器、计数器、显示器和校时电路组成。555集成芯片构成的振荡电路产生的信号经过分频器作为秒脉冲,秒脉冲送入计数器,计数结果通过“时”、“分”、“秒”译码器显示时间。

2.数字电子钟单元电路设计

时钟脉冲已经由实验箱提供,实验箱提供的是秒脉冲;

显示电路已经由实验箱提供。

(1)计数器电路

A.秒个位计数器,分个位计数器,时个位计数器均是十进制计数器;

B.秒十位计数器,分十位计数器均是六进制计数器;

C.时十位计数器为二进制计数器

因此,选择74LS90可以实现二-五-十进制异步计数器芯片实现上述计数功能。

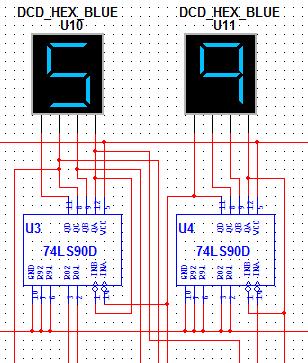

时位计数器

分位计数器

秒位计数器

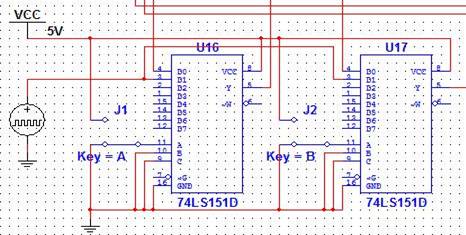

(2)手动校时电路

当数字钟走时出现误差时,需要校正时间。校时电路实现对“时”“分”“秒”的校准。在电路中设有正常计时和校对位置。本实验实现“时”“分”的校对。对校时的要求是:在小时校正时不影响分和秒的正常计数;在分钟校正时不影响秒和小时的正常计数。

手动校时电路图

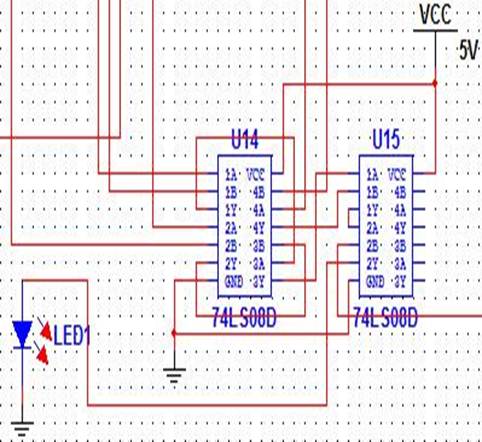

(3)整点报时电路

整点报时功能:即从59分51秒起(含59分51秒),每隔2秒发出一次蜂鸣,连续5次。

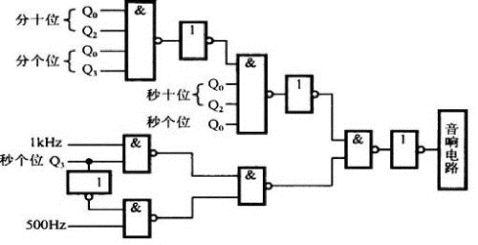

整点报时电路图

3.器件清单

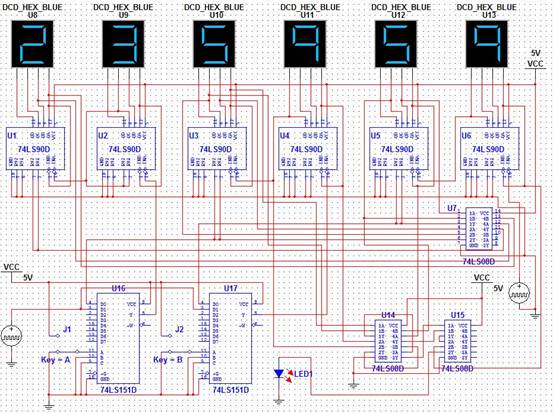

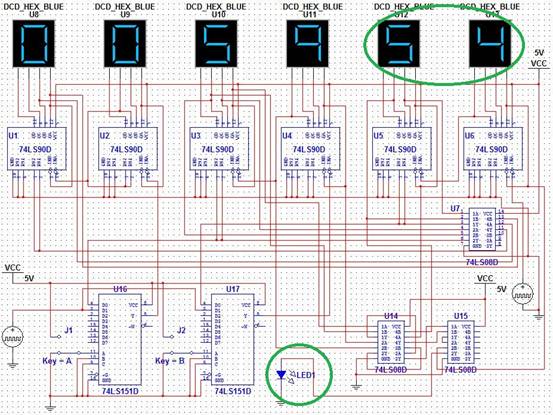

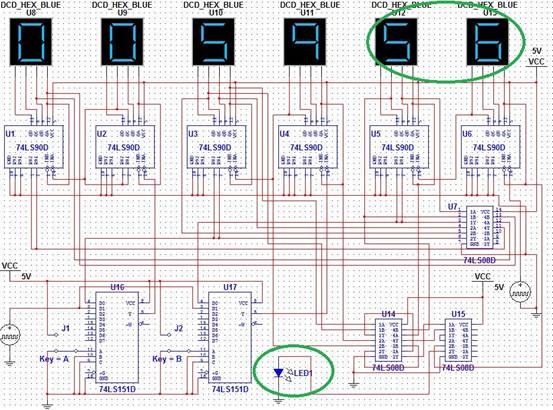

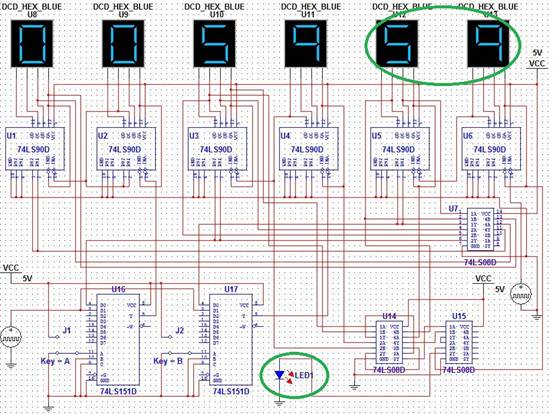

四 . EDA仿真模拟

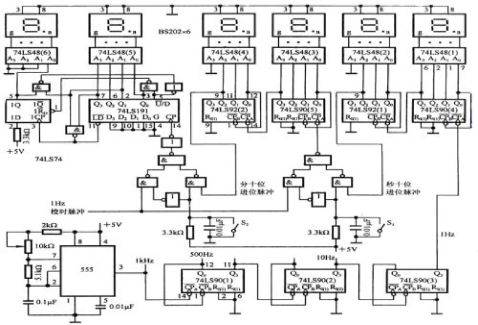

数字电子钟仿真电路图:

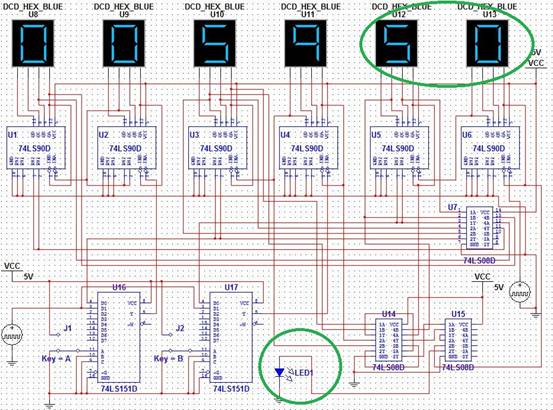

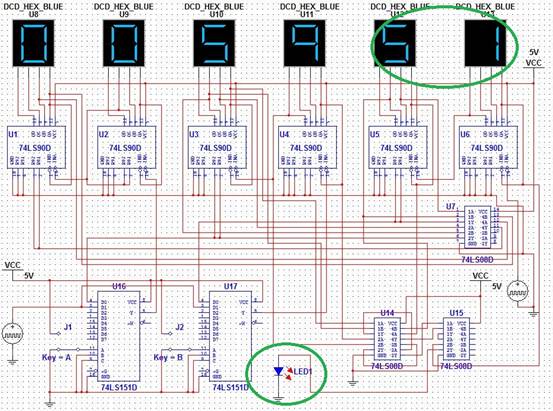

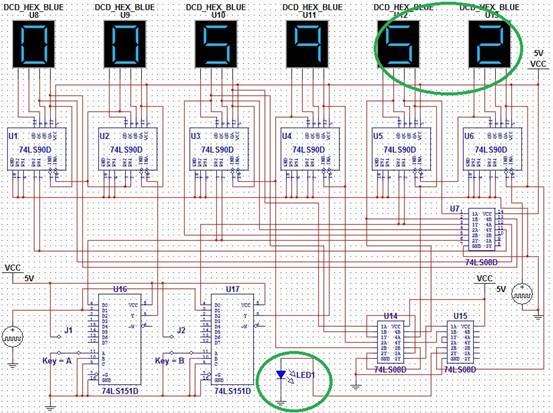

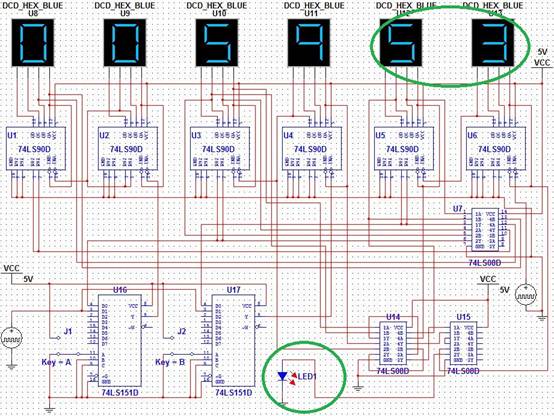

整点报时仿真结果(蜂鸣器由红色发光二级管代替):

59分50秒

59分50秒

59分51秒 59分52秒

59分52秒 59分53秒

59分53秒 59分54秒

59分54秒 59分55秒

59分55秒 59分56秒

59分56秒 59分57秒

59分57秒 59分58秒

59分58秒 59分59秒

59分59秒

五 .数字电子钟的组装与调试

由图中所示的数字中系统组成框图按照信号的流向分级安装,逐级级联。这里的每一级是指组成数字中的各个功能电路。

级联时如果出现时序配合不同步,或剑锋脉冲干扰,引起的逻辑混乱,可以增加多级逻辑门来延时。如果显示字符变化很快,模糊不清,可能是由于电源电流的跳变引起的,可在集成电路器件的电源端Vcc加退藕滤波电容。通常用几十微法的大电容与0.01μF的小电容相并联。

六 .实验结论

通过运用数字集成电路设计的24小时制的数字电子时钟,经过试验,成功实现了以下基本功能:

1.能准确计时,以数字形式显示时、分、秒的时间;

2.能实现整点报时的功能,并分别在51秒、53秒、55秒、57秒、59秒实现了蜂鸣的报时效果;

3.能定时控制,且能进行校正时间(通过开关调时、分)。

七 .实验心得

通过数字电子钟的实际设计,使我更进一步的熟悉了芯片的结构,掌握了相关个芯片的工作原理和其具体的使用方法,也锻炼了自己独立思考问题的能力;对于芯片的使用,我们应该在了解它的各项功能的前提条件下,灵活巧妙的运用。

在课程设计的过程中,我们应该带着不仅要知其然,而且要知道其所以然的态度对待任何事物,也要有钻研的信念和执着追求的意志力。

在实际电路搭建的过程中,出现了很多问题,例如,在校正时间过程中,切换校正时间脉冲和进位脉冲的过程中,跳变很严重,经历很多次改进,问题依旧很严重,但是我们没有放弃,耐心的查找问题,咨询老师,最终成功实现设计目标!

八 .参考文献

1.《数字电路逻辑设计》(第二版) 主编:王毓银

2.《数字电路硬件设计实践》 主编:贾秀美

第二篇:数字电子钟课程设计

数字电子钟设计报告

1.课程设计目的

※让学生掌握组合逻辑电路、时序逻辑电路及数字逻辑电路系统的设计、安装、测试方法;

※进一步巩固所学的理论知识,提高运用所学知识分析和解决实际问题的能力; ※提高电路布局﹑布线及检查和排除故障的能力;

※培养书写综合实验报告的能力。

2.课程设计题目描述和要求

(1)设计一个有“时”、“分”、“秒”(12小时59分59秒)显示,且有校时功能的电子钟;

(2)用中小规模集成电路组成电子钟,并在实验箱上进行组装、调试;

(3)画出框图和逻辑电路图,写出设计、实验总结报告;

(4)选做:整点报时。在59分51秒、53秒、55秒、57秒输出500Hz音频信号,在59分59秒时输出1000Hz信号,音频持续1s,在1000Hz荧屏结束时刻为整点。

3.课程设计报告内容

3.1实验名称

数字电子钟

3.2实验目的

掌握数字电子钟的设计、组装与调试方法;

熟悉集成电路的使用方法。

3.3实验器材及主要器件

(1)74LS48( 6片)

(2)74LS90(5片)

(3)74LS191(1片)

(4)74LS00(5片)

(5)74LS04(3片)

1(6)74LS74(1片) (7)74LS2O(2片) (8)555集成芯片(1片) (9)共阴七段显示器(6片) (10)电阻、电容、导线等(若干)

数字电子钟设计报告

3.4数字电子钟基本原理

数字电子钟的逻辑框图如图3-4所示。它由555集成芯片构成的振荡电路、分频器、计数器、显示器和校时电路组成。555集成芯片构成的振荡电路产生的信号经过分频器作为秒脉冲,秒脉冲送入计数器,计数结果通过“时”、“分”、

“秒”译码器显示时间。

图3-4

3.5数字电子钟单元电路设计、参数计算和器件选择

1.振荡器

石英晶体振荡器的特点是振荡频率准确、电路结构简单、频率易调整。它还具有压电效应,在晶体某一方向加一电场,则在与此垂直的方向产生机械振动,有了机械振动,就会在相应的垂直面上产生电场,从而机械振动和电场互为因果,这种循环过程一直持续到晶体的机械强度限止时,才达到最后稳定。这用压电谐振的频率即为晶体振荡器的固有频率。

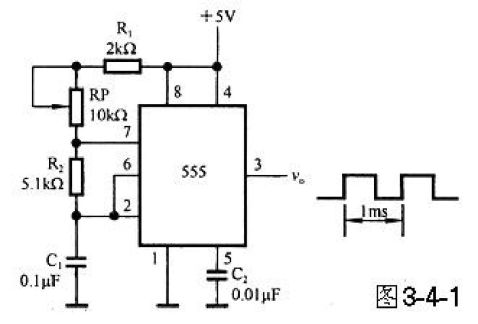

一般来说,振荡器的频率越高,计时精度越高,但耗电量将增大。如果精度要求不高也可以采用由集成电路定时器555与RC组成的多谐振荡器。如图3-4-1所示。设振荡频率f=1KHz,R为可调电阻,微调R1可以调出1KHz输出。 2

数字电子钟设计报告

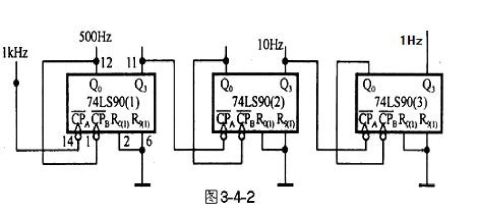

2.分频器

由于振荡器产生的频率很高,要得到秒脉冲,需要分屏电路。本实验由集成电路定时器555与RC组成的多谐振荡器,产生1KHz的脉冲信号。故采用3片中规模集成电路计数器74LS90来实现,得到需要的秒脉冲信号。如图3-4-2所示。

3.计数器

秒脉冲信号经过6级计数器,分别得到“秒”个位、十位、“分”个位、十位以及“时”个位、十位的计时。“秒”“分”计数器为六十进制,小时为十二进制。

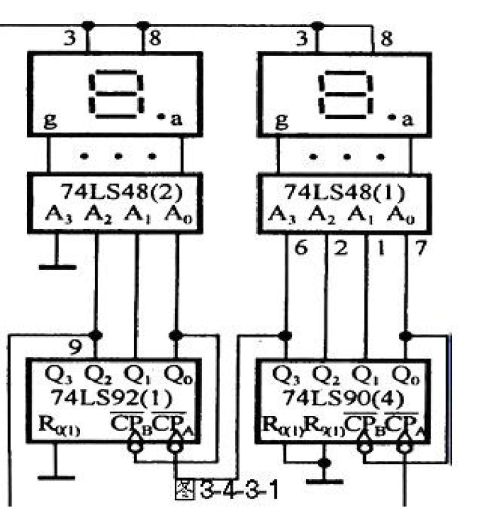

(1)六十进制计数

由分频器来的秒脉冲信号,首先送到“秒”计数器进行累加计数,秒计数器应完成一分钟之内秒数目的累加,并达到60秒时产生一个进位信号,所以,选用一片74LS90和一片74LS92组成六十进制计数器,采用反馈归零的方法来实现

3

数字电子钟设计报告

六十进制计数。其中,“秒”十位是六进制,“秒”个位是十进制。如图3-4-3-1

所示。

(2)十二四进制计数

“12翻1”小时计数器是按照“01——02——03——……——11——12——01——02——……”规律计数的,这与日常生活中的计时规律相同。在此实验中,小时的个位计数器由4位二进制同步可逆计数器74LS191构成,十位计数器由D触发器74LS74构成,将它们级连组成“12翻1”小时计数器。

计数器的状态要发生两次跳跃:一是计数器计到9,即个位计数器的状态为Q03Q02Q01Q00=1001,在下一脉冲作用下计数器进入暂态1010,利用暂态的两个1即Q03Q01使个位异步置0,同时向十位计数器进位使Q10=1;二是计数器计到12后,在第13个脉冲作用下个位计数器的状态应为Q03Q02Q01Q00=0001,十位计数器的Q10=0。第二次跳跃的十位清0和个位置1信号可由暂态为1的输出端Q10,Q01,Q00来产生。

4.译码器

译码是指把给定的代码进行翻译的过程。计数器采用的码制不同,译码电路 4

数字电子钟设计报告

也不同。74LS48驱动器是与8421BCD编码计数器配合用的七段译码驱动器。74LS48配有灯测试LT、动态灭灯输入RBI,灭灯输入/动态灭灯输出BI/RBO,当LT=0时,74LS48出去全1。

5.显示器

本系统用七段发光二极管来显示译码器输出的数字,显示器有两种:共阳极显示器或共阴极显示器。74LS48译码器对应的显示器是共阴极显示器。

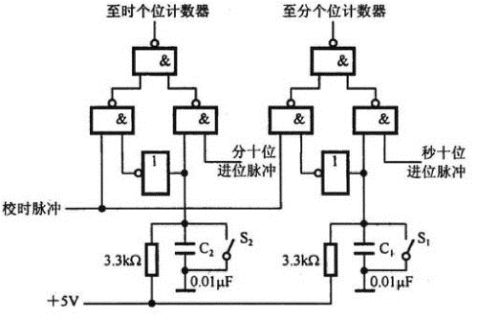

6.校时电路

当数字钟走时出现误差时,需要校正时间。校时电路实现对“时”“分”“秒”的校准。在电路中设有正常计时和校对位置。本实验实现“时”“分”的校对。对校时的要求是,在小时校正时不影响分和秒的正常计数;在分校正时不影响秒和小时的正常计数。需要注意的时,校时电路是由与非门构成的组合逻辑电路,开关S1或S2为“0”或“1”时,可能会产生抖动,为防止这一情况的发生我们接入一个由RS触发器组成的防抖动电路来控制。

图3-4-6-1 校时开关的功能表

S1

1

1

S2 1 1 0 功能 计数 校分 校时

5

数字电子钟设计报告

图3-4-6-2 校时电路

7.功能扩展电路----仿广播电台整点报时电路

仿广播电台整点报时电路的功能要求是,每当数字钟计时快要到整点时发出声响,通常按照4低音1高音的顺序发出间断声响,以最后一声高音结束的时刻为整点时刻。

设4声低音(约500Hz)分别发生在59分51秒、53秒、55秒及57秒,最后一声高音(约1KHz)发生在59分59秒,它们的持续时间均为1秒。

如表3-6-2所示

CP(秒) 50 51 52 53 54 55 56 57

Q3s1 0 0 0 0 0 0 0 0

Q2s1 0 0 0 0 1 1 1 1

Q1s1 0 0 1 1 0 0 1 1

Q0s1 0 1 0 1 0 1 0 1

功能 鸣低音 停 鸣低音 停 鸣低音 停 鸣低音

6

数字电子钟设计报告

58

59

00

1 1 0 0 0 0 0 0 0 0 1 0 停 鸣低音 停

图3-6-2 放电台报时电路

7

数字电子钟设计报告

3.6

数字电子钟电路图

3.7数字电子钟的组装与调试

由图3-4所示的数字中系统组成框图按照信号的流向分级安装,逐级级联。这里的每一级是指组成数字中的各个功能电路。

级联时如果出现时序配合不同步,或剑锋脉冲干扰,引起的逻辑混乱,可以

增加多级逻辑门来延时。如果显示字符变化很快,模糊不清,可能是由于电源电流的跳变引起的,可在集成电路器件的电源端Vcc加退藕滤波电容。通常用几十微法的大电容与0.01μF的小电容相并联。

4.收获与体会

伴随着几声清脆的滴答声,我们小组终于完成了长达两个星期的课程设计。俗话说“功夫不负有心人,铁杵也能磨成绣花针”,通过自己的努力,我们的数字电子钟设计也在今天完成了,看着老师仔细的验收,并成功的完成任务,有种如释重负的感觉,同时,看到成功闹钟的数字电子时钟,心中更多的是一种成就感。

当然,通过这次实践我也受益匪浅,从中学到了不少在书本中没有的东西,明白了实践与理论的结合是极其重要的,以及同学之间互相帮助的重要性,更重要的是对 8

数字电子钟设计报告

整个电路还有各个元器件有了充分的认识,还有在遇到困难时运用学过的相关知识和恰当的方法尽力去解决各个难题,通过自己不懈的努力与搭档的配合来完成这项团队任务。

当然,在整个课程设计中,我们也遇到了许多的难题。例如显示器无法正常显示数字,刚开始我们还以为是线路接法存在问题,经过仔细检查还是未得到解决,后来猜想是不是显示器本身存在问题,拿来万用表,经过检查,果然,猜想正确,个别接线柱有问题,但至于导致显示器无法正常显示的原因,后来想起是因为没有串联电阻导致电流过大而引起的,发现问题后,重新接上电阻问题得到了解决,也松了一口气,但是问题一个接一个,显示数字倒是没有问题了,但是数字无法进位,仔细调试了半天还是不能解决,最后反复检查电路,才弄明白原来是校时电路的接法存在一点问题,改正之后问题也再次得到了解决。就这样,经过我们不懈的努力,解决了一个又一个的问题,最后,终于完成了数字时钟的设计。

过程是艰辛的,但结果是令人兴奋的,看着自己设计的东西一分一秒的走着,心理觉得非常有成就感,这两个星期的努力并没有付诸东流。虽然实验已经告一段落,但是我们学习的道路还很长。此次实验让我明白不论是在做实验还是在今后的学习中,都应该有一种坚定不移不达目的不罢休的信念,只有这样才能达到自己的最终目标!

9

数字电子钟设计报告

参考文献

1. 绳广基编著.数字逻辑电路设计与实验【M】.上海:上海交通大学出版社,1988.

2. 阎石主编.数字电子技术基础【M】.第五版.北京:高等教育出版社,2006.

3. 《中国集成电路大全》编写委员会编.中国集成电路大全TTL集成电路【M】.北京:国防工业出版社,1985.

4. 梁宗善主编.电子技术基础课程设计.武汉:华中科技大学出版社,2009.

5. 朱定华主编.电子电路测试与实验.北京:清华大学出版社,2004.

10

数字电子钟设计报告

课程设计成绩: 业务考核成绩(70%平时成绩(30%(百分制记分) (百分制记分) 项 目

数字电子钟 综合总成绩 (百分制记分)

注:教师按学生实际成绩(平时成绩和业务考核成绩)登记并录入教务MIS系统,由系统自动转化为“优秀(90~100分)、良好(80~89分)、中等(70~79分)、及格(60~69分)和不及格(60分以下)”五等。

指导教师评语:

指导教师(签名):

11

数字电子钟设计报告

20 年 月 日

12

-

数字电子钟课程设计报告

华南农业大学电子技术课程设计数字电子钟电路摘要在生活中的各种场合经常要用到电子钟,现代电子技术的飞跃发展,各类智能化产品相应而出,…

-

数字电子钟课程设计报告-数电

华东交通大学理工学院课程设计报告书所属课程名称数字电子技术课程设计题目数字电子钟课程设计分院电信分院专业班级10电信2班学号20x…

-

数字电子时钟课程设计报告

数字电子钟课程设计报告题目数字电子钟的设计与仿真专业机械工程前言加入世贸组织以后中国会面临激烈的竞争这种竞争将是一场科技实力管理水…

-

数字电子时钟课程设计报告-4

数字电子钟课程设计报告题目数字电子钟的设计与仿真专业通信工程前言加入世贸组织以后中国会面临激烈的竞争这种竞争将是一场科技实力管理水…

-

数字电子时钟课程设计报告

华北科技学院课程设计数字时钟课程设计报告目录一设计的目的任务和要求2二设计的方案的选择与论证4三电路的设计5a设计内容5b数字时钟…

-

女生节活动总结

合肥师范学院中文系学生会活动总结表第一届“花样女生缤纷合师”女生节活动总结为了能够更好地弘扬女性文化,展现当代女大学生的风貌,增强…

-

神经病学重点总结

一中枢神经:中枢神经系统CNS包括脑和脊髓,脑分大脑、间脑、脑干和小脑等部分,脊髓由含有神经细胞的灰质和含上、下行传导束的白质组成…

-

初二小班教案--20xx八年级上册unit9知识点总结

Unit9Canyoucometomyparty?本单元重要词组及短语:在周六下午__________为……做准备________…

-

软环境工作总结

**局**年软环境工作总结**年,***在区委、区政府的正确领导下,按照全区软环境工作要求,结合系统实际,坚持做到了规范机关工作、…

-

结核宣传工作总结

肺结核宣传工作总结肺结核是威胁人类健康的传染病。为了广泛深入、科学的宣传国家结核病防治政策和结核病的防治知识,动员全社会参与和关注…