数电实验 计数器及其应用

实验四 计数器及其应用

一、实验目的

1、掌握中规模集成计数器的使用及功能测试方法

2、运用集成计数计构成1/N分频器

二、实验原理

计数器是一个用以实现计数功能的时序部件,它不仅可用来计脉冲数,还常用作数字系统的定时、分频和执行数字运算以及其它特定的逻辑功能。

1、中规模十进制计数器

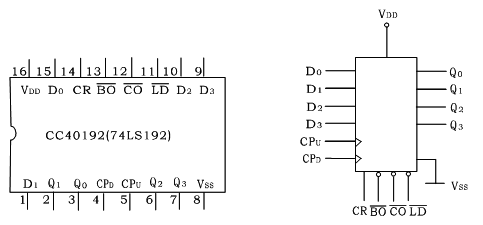

CC40192(74LS192)是同步十进制可逆计数器,具有双时钟输入,并具有清除和置数等功能,其引脚排列及逻辑符号如图9-2所示。

图9-2 CC40192引脚排列及逻辑符号

图中  —置数端 CPU—加计数端 CPD —减计数端

—置数端 CPU—加计数端 CPD —减计数端

—非同步进位输出端

—非同步进位输出端  —非同步借位输出端

—非同步借位输出端

D0、D1、D2、D3 —计数器输入端

Q0、Q1、Q2、Q3 —数据输出端 CR—清除端

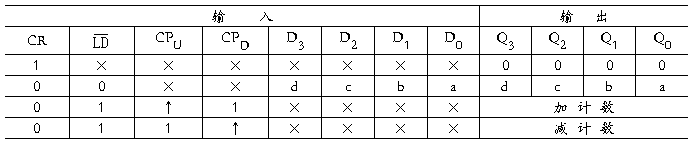

CC40192(同74LS192,二者可互换使用)的功能如表9-1,说明如下:

表9-1

当清除端CR为高电平“1”时,计数器直接清零;CR置低电平则执行其它功能。

当CR为低电平,置数端 也为低电平时,数据直接从置数端D0、D1、D2、D3 置入计数器。

也为低电平时,数据直接从置数端D0、D1、D2、D3 置入计数器。

当CR为低电平, 为高电平时,执行计数功能。执行加计数时,减计数端CPD 接高电平,计数脉冲由CPU 输入;在计数脉冲上升沿进行 8421 码十进制加法计数。执行减计数时,加计数端CPU接高电平,计数脉冲由减计数端CPD 输入,表9-2为8421码十进制加、减计数器的状态转换表。

为高电平时,执行计数功能。执行加计数时,减计数端CPD 接高电平,计数脉冲由CPU 输入;在计数脉冲上升沿进行 8421 码十进制加法计数。执行减计数时,加计数端CPU接高电平,计数脉冲由减计数端CPD 输入,表9-2为8421码十进制加、减计数器的状态转换表。

表9-2 加法计数

表9-2 加法计数

减计数

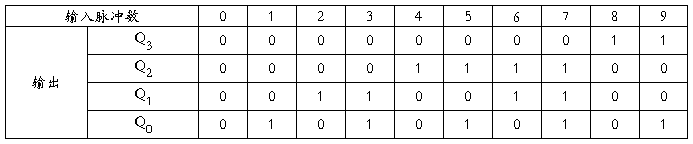

2、计数器的级联使用

一个十进制计数器只能表示0~9十个数,为了扩大计数器范围,常用多个十进制计数器级联使用。

同步计数器往往设有进位(或借位)输出端,故可选用其进位(或借位)输出信号驱动下一级计数器。

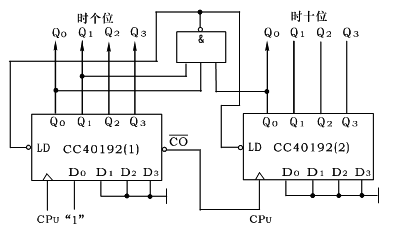

图9-3是由CC40192利用进位输出 控制高一位的CPU端构成的加数级联图。

控制高一位的CPU端构成的加数级联图。

图9-3 CC40192级联电路

3、实现任意进制计数

(1) 用复位法获得任意进制计数器

假定已有N进制计数器,而需要得到一个M进制计数器时,只要M<N,用复位法使计数器计数到M时置“0”,即获得M进制计数器。如图9-4所示为一个由CC40192十进制计数器接成的6进制计数器。

图9-4 六进制计数器

(2) 图9-6是一个特殊12进制的计数器电路方案。在数字钟里,对时位的计数序列是1、2、…11,12、1、…是12进制的,且无0数。如图所示,当计数到13时,通过与非门产生一个复位信号,使CC40192(2)〔时十位〕直接置成0000,而CC40192(1),即时的个位直接置成0001,从而实现了1-12计数。

图9-6 特殊12进制计数器

三、实验设备与器件

1、 +5V直流电源 2、 双踪示波器

3、 连续脉冲源 4、 单次脉冲源

5、 逻辑电平开关 6、 逻辑电平显示器

7、 译码显示器

8、 CC40192×2(74LS192×2) CC4012×1(74LS20×1)

四、实验内容

1、测试CC40192或74LS192同步十进制可逆计数器的逻辑功能

计数脉冲由单次脉冲源提供,清除端CR、置数端 、数据输入端D3 、D2、D1、D0 分别接逻辑开关,输出端 Q3、Q2、Q1、Q0接实验设备的一个译码显示输入相应插口A、B、C、D;

、数据输入端D3 、D2、D1、D0 分别接逻辑开关,输出端 Q3、Q2、Q1、Q0接实验设备的一个译码显示输入相应插口A、B、C、D; 和

和 接逻辑电平显示插口。按表9-1逐项测试并判断该集成块的功能是否正常。

接逻辑电平显示插口。按表9-1逐项测试并判断该集成块的功能是否正常。

(1) 清除

令CR=1,其它输入为任意态,这时Q3Q2Q1Q0=0000,译码数字显示为0。清除功能完成后,置CR=0

(2) 置数

CR=0,CPU,CPD 任意,数据输入端输入任意一组二进制数,令 = 0,观察计数译码显示输出,置数功能是否完成,此后置

= 0,观察计数译码显示输出,置数功能是否完成,此后置 =1。

=1。

(3) 加计数

CR=0, =CPD =1,CPU 接单次脉冲源。清零后送入10个单次脉冲,观察译码数字显示是否按8421码十进制状态转换表进行;输出状态变化是否发生在CPU 的上升沿。

=CPD =1,CPU 接单次脉冲源。清零后送入10个单次脉冲,观察译码数字显示是否按8421码十进制状态转换表进行;输出状态变化是否发生在CPU 的上升沿。

(4) 减计数

CR=0, =CPU =1,CPD 接单次脉冲源。参照3)进行实验。

=CPU =1,CPD 接单次脉冲源。参照3)进行实验。

(5)计数器的分频功能

使CC40192或74LS192工作于加计数状态,CR=0, =CPD =1,CPU输入1KHz连续脉冲,用示波器观察Q3、Q2、Q1、Q0的波形,并记录它们各自的波形和频率;分析Q3、Q2、Q1、Q0分别是对输入计数脉冲CPU 的几分频?

=CPD =1,CPU输入1KHz连续脉冲,用示波器观察Q3、Q2、Q1、Q0的波形,并记录它们各自的波形和频率;分析Q3、Q2、Q1、Q0分别是对输入计数脉冲CPU 的几分频?

(选做)2、图9-3所示,用两片CC40192组成两位十进制加法计数器,输入1Hz连续计数脉冲,进行由00—99累加计数,记录之。

五、实验预习要求

1、复习有关计数器部分内容

2、绘出各实验内容的详细线路图

3、拟出各实验内容所需的测试记录表格

4、查手册,给出并熟悉实验所用各集成块的引脚排列图

六、实验报告

1、画出实验线路图,记录、整理实验现象及实验所得的有关波形。对实验结果进行分析。

2、总结使用集成计数器的体会。

第二篇:数电实验报告:计数器及其应用

数字电子技术实验报告

实验四:计数器及其应用

一、实验目的:

1、熟悉常用中规模计数器的逻辑功能。

2、掌握二进制计数器和十进制计数器的工作原理和使用方法。

二、实验设备:

1、数字电路实验箱;

2、74LS90。

三、实验原理:

1、 计数是一种最简单基本运算,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时具有分频功能。计数器按计数进制分有:二进制计数器,十进制计数器和任意进制计数器;按计数单元中触发器所接收计数脉冲和翻转顺序分有:异步计数器,同步计数器;按计数功能分有:加法计数器,减法计数器,可逆(双向)计数器等。

2、 74LS90是一块二-五-十进制异步计数器,外形为双列直插,NC表示空脚,不接线,它由四个主从JK触发器和一些附加门电路组成,其中一个触发器构成一位二进制计数器;另三个触发器构成异步五进制计数器。在74LS90计数器电路中,设有专用置“0”端R0(1),R0(2)和置“9”端S9(1)S9(2)。。其中前两个为异步清0端,后两个为异步置9端。CP1, CP2为两个时钟输入端;Q0 ~Q3为计数输出端。当R1=R2=S1=S2=0时,时钟从CP1引入,Q0输出为二进制;从CP2引入,Q3输出为五进制。时钟从CP1引入,二Q0接CP1,则Q3Q2Q1Q0输出为十进制(8421码);时钟从CP2引入,而Q3接CP1,则Q0Q3Q2Q1输出为十进制(5421码)。

四、实验原理图及实验结果:

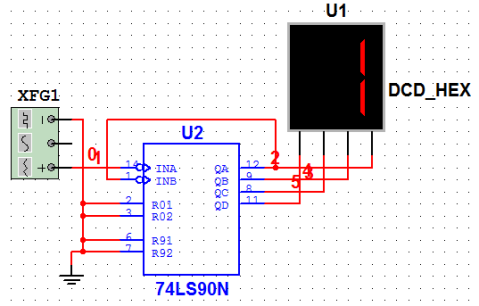

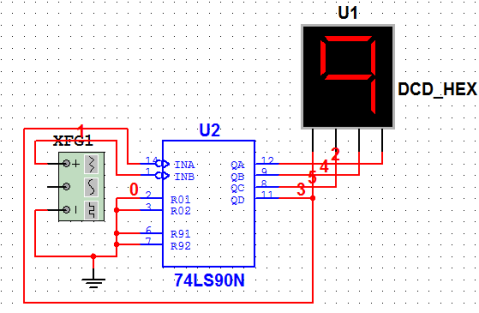

1、实现0~9十进制计数。

1)实验原理图如下:(函数信号发生器:5V 3Hz 偏移2.5V方波)

2)实验结果:

解码器上依次显示0~9十个数字。

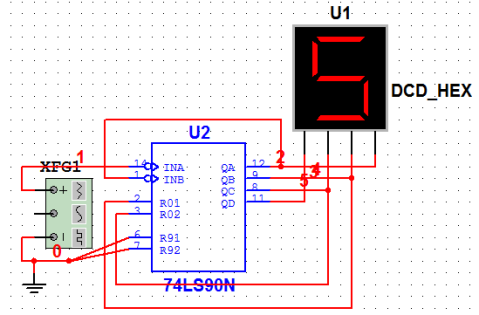

2、实现六进制计数。

1)实验原理图如下:(函数信号发生器:5V 3Hz 偏移2.5V方波)

2)实验结果:解码器上依次显示0~5六个数字。

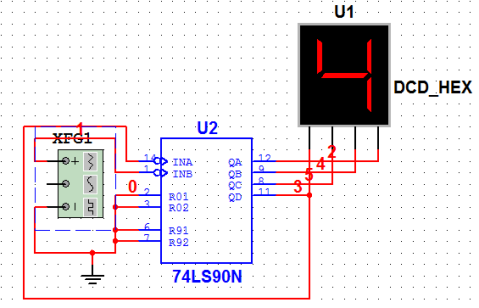

3、实现0、2、4、6、8、1、3、5、7、9计数。

1)实验原理图如下:(函数信号发生器:5V 3Hz 偏移2.5V方波)

2)实验结果:

解码器上依次显示0、2、4、6、8、1、3、5、7、9十个数字。

五、实验结果分析:

1、实验要求实现0~9十进制计数,结合实验结果知所设计的电路符合要求。

2、实验要求实现六进制计数,结合实验结果知所设计的电路符合要求。

3、实验要求实现0、2、4、6、8、1、3、5、7、9计数,结合实验结果知所设计的电路符合要求。

六、实验心得体会:

通过这次实验,我对74LS90有了一定的了解,并会用它来实现一些功能,在实验的过程中我遇到了一些问题,但后来在同学和老师的帮助下还是顺利的完成了实验,我学到了很多;通过这次实验,我对5421码掌握的更好了。

-

计数器的应用——实验报告

计数器的应用20xx0810410计科四班阚琛琛实验内容1测试74LS90的逻辑功能2用模拟示波器测试74LS90的输入出波形图3…

- 电子技术实验报告7-计数器及其应用(葛楚雄)

-

数字电路实验报告 计数器的逻辑功能及应用

数字电路实验报告计数器逻辑功能及其应用一实验目的1熟悉中等规模集成电路计数器74LS160的逻辑功能使用方法及应用2掌握构成任意进…

-

西工大数电实验报告——计数器及其应用

计数器及其应用班级03051001班学号姓名同组成员一实验目的1熟悉常用中规模计数器的逻辑功能2掌握二进制计数器和十进制计数器的工…

- 数字逻辑实验报告:计数器及其应用

-

数电实验报告

数字电子技术实验报告中频自动增益数字电路研究学院班级姓名学号指导老师电子信息工程学院通信1309目录一设计任务要求2基础部分2发挥…

-

数电实验报告

数电实验报告班级学号姓名班内序号20xx年5月30日一实验内容及要求一Quartus原理图输入法设计1用逻辑门设计实现一个半加器仿…

-

数电实验报告

信息工程学院20xx20xx学年第一学期课程设计报告课程名称数字电子技术课程设计班级学号电信1201班12610103151093…

-

哈工大数电实验报告

HarbinInstituteofTechnology数字逻辑电路与系统课程名称院系班级哈尔滨工业大学20xx年11月实验二时序逻…

-

数电实验报告

数电实验报告一实验要求实验目的1熟悉用QuartusII原理图输入法进行电路设计和仿真2掌握QuartusII图形模块单元的生成与…