数字逻辑实验-触发器实验报告

肇 庆 学 院

电子信息与机电工程学院 数字电路 课 实验报告

12电气(1) 班 姓名李俊杰 学号 201224122119 实验日期2014年5 月19 日

实验合作者:王圆圆 老师评定

实验题目:触发器的功能测试

一、实验目的

(一)掌握基本RS触发器的功能测试。

(二)掌握集成触发器的电路组成形式及其功能。

(三)熟悉时钟触发器不同逻辑功能之间的相互转换。

(四)认识触发器构成的脉冲分频电路。

二、实验仪器:

DZX-1型电子学综合实验装置 UT52万用表 GDS-806S双踪示波器 74LS00 74LS74 74LS76

三、实验内容&数据分析

触发器具有两个稳定状态,用以表示逻辑状态“1”和“0”,在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态,它是一种具有记忆功能的二进制信息存贮器件,是构成各种时序电路的最基本逻辑单元。第一步,将触发器74LS74、74LS76引出端排列图和状态表画在实验报告上。(注:此项内容必须在进实验室前完成。)

(一)测试基本RS触发器的逻辑功能

用两个与非门组成基本RS触发器如图4-1,输入端 ,

, 接逻辑电平开关输出插口,输出端

接逻辑电平开关输出插口,输出端 、

、 接逻辑电平显示插口,按表4-1要求测试。

接逻辑电平显示插口,按表4-1要求测试。

表4-1 基本RS触发器特性表(输入低电平有效)

表4-1 基本RS触发器特性表(输入低电平有效)

图4-1 由74ls00连接成的基本RS触发器

测试集成双JK触发器74LS76的逻辑功能

1、测试 、

、 端的复位、置位功能

端的复位、置位功能

74LS76逻辑符号如图4-2,对照其插脚(查阅附录B)取其中一JK触发器, 、

、 、J、K端分别接逻辑电平开关输出插口,CP接单次脉冲源(正脉冲),

、J、K端分别接逻辑电平开关输出插口,CP接单次脉冲源(正脉冲), 、

、 接至逻辑电平显示输入插口。要求在

接至逻辑电平显示输入插口。要求在 =0,

=0, =1以及

=1以及 =0,

=0, =1时任意改变J、K及CP的状态用“ⅹ”符号表示,观测

=1时任意改变J、K及CP的状态用“ⅹ”符号表示,观测 、

、 状态。

状态。

表4-2 集成双JK触发器74LS76特性表1

表4-2 集成双JK触发器74LS76特性表1

图4-2 74LS76管脚排列

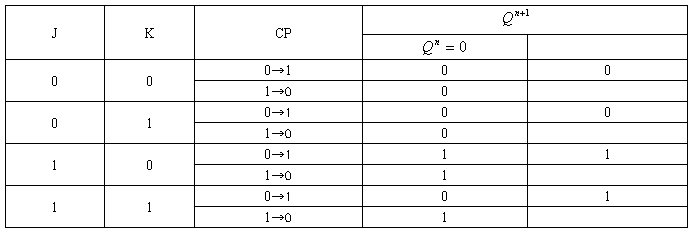

2、测试触发器的逻辑功能

按表4-2的要求改变J、K、CP端状态,记录Q的状态变化,观察触发器状态的更新发生在CP脉冲(单脉冲)的上降沿还是下降沿?(注意 、

、 端的电平接法)

端的电平接法)

表4-3 集成双JK触发器74LS76特性表2

表4-3 集成双JK触发器74LS76特性表2

图4-2 JK触发器逻辑符号

3、JK触发器的J、K端连在一起,构成T’触发器。

在CP端输入1MHZ连续脉冲,用双踪示波器观察CP、Q端的波形,注意相位与时间的关系。

图4-3 JK触发器构成T’触发器电路图 及CP、Q端的波形图

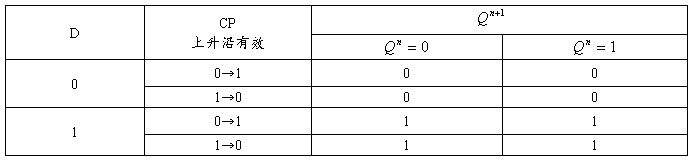

(三)测试集成双D触发器74LS74的逻辑功能

1、74LS74逻辑符号如图4-3,对照其插脚,任取一只D触发器,按表4-3要求进行测试,并观察触发器状态的更新是在CP脉冲的上降沿还是下降沿?(注意复位

1、74LS74逻辑符号如图4-3,对照其插脚,任取一只D触发器,按表4-3要求进行测试,并观察触发器状态的更新是在CP脉冲的上降沿还是下降沿?(注意复位 、置位

、置位 端的电平接法)

端的电平接法)

表4-3 集成双D触发器74LS74的特性表

表4-3 集成双D触发器74LS74的特性表

图4-4 D触发器逻辑符号及74LS74引脚图

2、将D触发器的 端与D端相连接,构成

端与D端相连接,构成 触发器。测试方法同实验内容(二)(3)。

触发器。测试方法同实验内容(二)(3)。

图4-5 D触发器构成 触发器电路图

触发器电路图

(四)JK触发器简单应用实验————电路构成及测试

实验电路照图4-6连接(注意复位 、置位

、置位 端的电平接法)。时钟频率用时钟信号源的“Q7”,加到CP端,用示波器分别显示Q0、Q1和

端的电平接法)。时钟频率用时钟信号源的“Q7”,加到CP端,用示波器分别显示Q0、Q1和 的波形,并把波形图画在实验报告中。

的波形,并把波形图画在实验报告中。

图4-7 JK触发器Q0、Q1和 的波形

的波形

分析D触发器和JK触发器,找出它们的相同点和不同点。

同:

两者都是由基本RS触发器构成的边沿触发器

异:

1、 JK触发器有JK两个输入端,能实现保持、置零、置一、翻转功能

2、 D触发器只有一输入端,能实现置零、置一功能

第二篇:华科计算机数字逻辑实验报告 D触发器设计

实验名称: D触发器设计

专业班级:

学 号:

姓 名:

同组成员:

指导教师:

报告日期: 2013.6.11

1、系统需求

PC 个人计算机

ISE14.2 软件

D.V 文件

D.UCF 文件

USB下载线

Adept软件

开发板Basys2

2、实验内容:

用电平异步时序逻辑电路,实现上升沿触发的D触发器(无空翻).需要一个复位信号RESET,和一个置位信号RET,均为低电平有效.

接线:

输入信号:

D-------- 接板子上SW0(FPGA内部“p11”);;

CP-------接FPGA内部“B8”(50MHz);

RESET-----L3;

SET----- K3;

输出信号:

Q---------接板子上灯ld0(FPGA内部“m5”);

Q(非)----M11;

3、实验目的 :

当你完成整个项目之后,你将学会以下的功能.

(1)?用ISE14.2 的软件开启一个 Spartan3E的项目.

(2)撰写一个简单的Schematic原理图,?用语法检查器(Syntax Check)来修

正语法的错误

(3)产生测试模板(Test Bench) 来辅助你的设计.

(4)加入系统所需的Constraints 文件.(UCF file)

(5)完成整个设计?程.并产生D.bit文件。

(6)?用Adept软件来烧录D.bit 文件到FPGA.

4、实验过程

4.1 verilog代码

`timescale 1ns / 1ps

module D3(

input d,

input clk,

input set,

input reset,

output q,

output qn

);

reg qt,qnt;

always @(posedge clk or negedge set or negedge reset)

begin

if (!reset) begin

qt <= 0; //异步清0,低电平有效

qnt <= 1;

end

else if (!set) begin

qt <= 1; //异步置1,低电平有效

qnt <= 0;

end

else begin

qt <= d;

qnt <= ~d;

end

end

assign q = qt;

assign qn = qnt;

endmodule

4.2 设计仿真

4.2.1编辑激励:

`timescale 1ns / 1ps

`module test;

// Inputs

reg d;

reg clk;

reg set;

reg reset;

// Outputs

wire q;

wire qn;

// Instantiate the Unit Under Test (UUT)

D3 uut (

.d(d),

.clk(clk),

.set(set),

.reset(reset),

.q(q),

.qn(qn)

);

always #20 clk = ~clk;

always #10 d = {$random}%2;

always begin

#100 set = 1'b0;

#10 set = 1'b1;

end

always begin

#200 reset = 1'b0;

#10 reset = 1'b1;

end

initial begin

// Initialize Inputs

d = 0;

clk = 0;

set = 1;

reset = 1;

// Wait 800 ns for global reset to finish

#800;

// Add stimulus here

End

Endmodule

4.2.2 仿真模拟图

图 1:仿真结果

4.3 创建约束

Ucf文件内容:

#Created by Constraints Editor (xc3s100e-cp132-4) - 2013/06/01

NET "clk" TNM_NET = "clk";

TIMESPEC TS_clk = PERIOD "clk" 20 ns HIGH 50 %;

# PlanAhead Generated physical constraints

NET "clk" LOC = B8;

NET "d" LOC = P11;

NET "q" LOC = M5;

NET "qn" LOC = M11;

NET "reset" LOC = L3;

NET "set" LOC = K3;

4.4 下载到板子

5.感想

没有用原理图方式做,因为在仿真时怎么都过不了,所以就用verilog做了。

就觉得语法规则还不熟悉,但是思路比较简单,因为逻辑功能都知道了。

后来看别人用原理图做出来了,其实只要图画出来就行了,激励的编辑可能开始一些语法有错误。

-

触发器实验报告

深圳大学实验报告课程名称学院计算机与软件学院实验时间实验报告提交时间教务部制注1报告内的项目或内容设置可根据实际情况加以调整和补充…

- 触发器及其应用实验报告

- 电子技术实验报告5-触发器及其应用

- 数字逻辑实验-触发器实验报告

-

触发器 R-S、D 、J-K 实验报告(有数据)

实验五触发器RSDJK一实验目的1熟悉并掌握RSDJK触发器的构成工作原理和功能测试方法2学会正确使用触发器集成芯片3了解不同逻辑…

-

触发器实验报告

深圳大学实验报告课程名称学院计算机与软件学院实验时间实验报告提交时间教务部制注1报告内的项目或内容设置可根据实际情况加以调整和补充…

-

数字逻辑JK触发器实验报告

信息工程学院数字逻辑与数字系统实习报告学院信息工程学院班级信息103姓名张丽玲学号20xx013077成绩实验五JK触发器一实验目…

- 触发器及其应用实验报告

- 电子技术实验报告5-触发器及其应用

-

触发器的使用实验报告

实验II触发器及其应用一实验目的1掌握基本RSJKD和T触发器的逻辑功能2掌握集成触发器的逻辑功能及使用方法3熟悉触发器之间相互转…

-

浙大电工电子实验报告 实验十五 集成定时器及其应用

实验报告课程名称:电工电子学实验指导老师:实验名称:集成定时器及其应用一、实验目的1.了解集成定时器的功能和外引线排列。2.掌握用…