实验8 移位寄存器逻辑功能测试及应用

实验八 移位寄存器逻辑功能测试及应用

一、实验目的:

1、掌握中规模4位双向移位寄存器逻辑功能及使用方法;

2、熟悉移位寄存器的应用——构成环形计数器和实现数据的串行、并行转换。

二、实验原理:

移位寄存器是一个具有移位功能的寄存器,是指寄存器中所存的代码能够在移位脉冲的作用下依次左移或右移。既能左移又能右移的称为双向移位寄存器,只需要改变左、右移的控制信号便可实现双向移位要求。本实验选用的4位双向移位寄存器,型号为74LS194,其引脚排列如图11—1所示。

移位寄存器不仅可以组成串行—并行数码转换器,还可以方便地组成移位寄存器型计数器、脉冲分配器等电路。常用的移位寄存器有环行计数器和扭环型计数器。

图11—1 74LS194引脚排列及功能

三、实验仪器及器材:

实验仪器设备:DGJ—2型电工技术实验装置 (D71—2数电实验挂箱)

集成块:74LS194 74LS04

四、实验内容与步骤:

1、验证移位寄存器74LS194的逻辑功能:

计数脉冲由单次脉冲源提供,清零端 、工作状态控制端M1 M2、并行数据输入端D0—D3、DSL为左移串行数据输入端、DSR右移串行数据输入端分别接逻辑电平开关,输出端Q0—Q3均接逻辑电平显示。按如下逐项测试并判断该集成块的功能是否正常。

、工作状态控制端M1 M2、并行数据输入端D0—D3、DSL为左移串行数据输入端、DSR右移串行数据输入端分别接逻辑电平开关,输出端Q0—Q3均接逻辑电平显示。按如下逐项测试并判断该集成块的功能是否正常。

(1)异步清零功能:当 =0时,这时Q3Q2Q1Q0=0000,双向移位寄存器清零。其它输入信号都不起作用,与CP无关,故称为异步清零。

=0时,这时Q3Q2Q1Q0=0000,双向移位寄存器清零。其它输入信号都不起作用,与CP无关,故称为异步清零。

(2)保持功能:当 =1,且CP=0或M1 =M2=0时,双向移位寄存器保持状态不变。

=1,且CP=0或M1 =M2=0时,双向移位寄存器保持状态不变。

(3) 同步并行送数功能:当 =1,M1 =M2=1时,在CP上升沿操作下,并行输入数据d3 d2 d1 d0送入寄存器。

=1,M1 =M2=1时,在CP上升沿操作下,并行输入数据d3 d2 d1 d0送入寄存器。

(4)右移串行送数功能:当 =1,M1 =0、M2=1时,在CP上升沿操作下,可依次把加在

=1,M1 =0、M2=1时,在CP上升沿操作下,可依次把加在 端的数据从时钟触发器 行送入寄存器中。

端的数据从时钟触发器 行送入寄存器中。

(5)左移串行送数功能:当 =1,M1 =1、M2=0时,在CP上升沿操作下,可依次把加在DSL端的数据从时钟触发器串行送入寄存器中。

=1,M1 =1、M2=0时,在CP上升沿操作下,可依次把加在DSL端的数据从时钟触发器串行送入寄存器中。

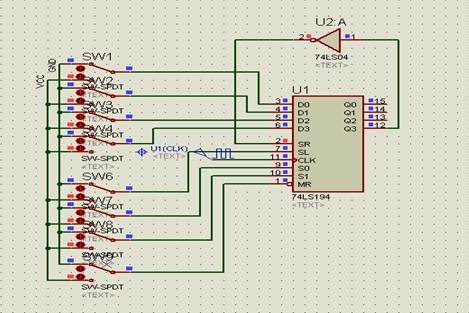

其仿真图为:

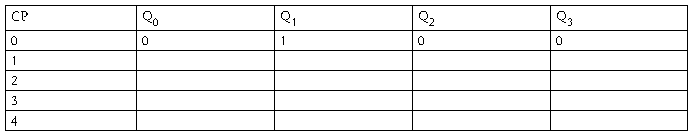

根据仿真图可得到如下状态图:

2、用74LS194构成环行计数器,画出实验电路图及其状态图,并陈述电路功能。

3、用74LS194构成扭环行计数器,画出实验电路图及其状态图,并陈述电路功能。

五、实验报告要求

整理实验数据,总结本次实验的收获与体会。

1、 熟悉并了解74LS194的功能。

第二篇:移位寄存器功能测试及应用

实验八 移位寄存器功能测试及应用

一、实验目的:

1.掌握中规模4位双向寄存器逻辑功能及使用方法。

2.熟悉移位寄存器的应用,实现数据的串行、并行转换和构成环形计数器

二、实验仪器及材料

a) TDS-4数电实验箱、双踪示波器、数字万用表。

b) 参考元件:74LS194一片。

三、预习要求及思考题

1.预习要求:

1) 复习有关寄存器有关内容。

2)熟悉74LS194逻辑功能及引脚排列。

3)用multisim软件对实验进行仿真并分析实验是否成功。

2.思考题:

1) 使寄存器 清零,除采用 输入低电平外,可否采用右移或左移的方法?可否使用并行送数法?若可行,如何进行操作?

输入低电平外,可否采用右移或左移的方法?可否使用并行送数法?若可行,如何进行操作?

2) 环行计数器的最大优点和缺点是什么?

四、实验原理

1.位寄存器是一个具有移位功能的寄存器,是指寄存器中所存的代码能够在移位脉冲

的作用下依次左移或右移。既能左移又能右移的称为双向移位寄存器,只需要改变左、右移的控制信号便可实现双向移位要求。根据移位寄存器存取信息的方式不同分为:串入串出、串入并出、并入串出、并入并出四种形式。

本实验选用的4位双向通用移位寄存器,型号为CC40194或74LS194,两者功能相

同,可互换使用,其逻辑符号及引脚图如图8-1所示。

图8-1 74LS194的逻辑符号图及引脚功能图.

其中D0、D1、D2、D3为并行输入端;Q0、Q1、Q2、Q3为并行输出端;SR为右移串行输入端;SL为左移串行输入端;S0、S1为操作模式控制端;CR为直接无条件清零端;CP为时钟脉冲输入端。

其中D0、D1、D2、D3为并行输入端;Q0、Q1、Q2、Q3为并行输出端;SR为右移串行输入端;SL为左移串行输入端;S0、S1为操作模式控制端;CR为直接无条件清零端;CP为时钟脉冲输入端。

74LS194有5种不同操作模式:即并行送数寄存,右移(方向由Q0-->Q3),左移(方向由Q3→Q0),保持及清零。

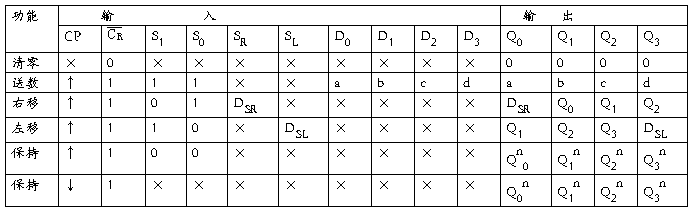

S1、S0和CR端的控制作用如表8-1

S1、S0和CR端的控制作用如表8-1

2、移位寄存器应用很广,可构成移位寄存器型计数器:顺序脉冲发生器;串行累加器;可用数据转换,即把串行数据转换为并行数据,或把并行数据转换为串行数据等。本实验研究移位寄存器用作环形计数器和数据的串、并行转换。

(1)环行计数器

把移位寄存器的输出反馈到它的串行输入端,就可以进行循环移位。

(2)实现数据、并行转换器

a)串行∕并行转换器

串行∕并行转换器是指串行输入的数码,经转换电路之后变换成并行输出

b)并行∕串行转换器

并行∕串行转换器是指并行输入的数码经转换电路之后,换成串行输出。

表8-1

五、实验内容

1、测试74LS194的逻辑功能完成表8-2

按图8-1接线 、S1、S0、SL、SR、D0、D1、D2、D3分别接至逻辑开关;Q0、Q1、Q2、Q3接至发光二极管。CP端接单次脉冲源。按表7-1所规定的输入状态,逐项进行测试。

、S1、S0、SL、SR、D0、D1、D2、D3分别接至逻辑开关;Q0、Q1、Q2、Q3接至发光二极管。CP端接单次脉冲源。按表7-1所规定的输入状态,逐项进行测试。

74LS194逻辑功能测试

(1)清除:令 =0,其它输入均为任意态,这时寄存器输出Q0、 Q1、 Q2 、Q3应均为0。清除后,至

=0,其它输入均为任意态,这时寄存器输出Q0、 Q1、 Q2 、Q3应均为0。清除后,至 =1。

=1。

(2)送数:令 =S1=S0=1 ,送入任意4位二进制数,如D0、D1、D2、D3=abcd,加CP脉冲,观察CP=0、CP由1→0、三种情况下寄存器输出状态的变化,观察寄存输出状态变化是否发生在CP脉冲的上升沿。

=S1=S0=1 ,送入任意4位二进制数,如D0、D1、D2、D3=abcd,加CP脉冲,观察CP=0、CP由1→0、三种情况下寄存器输出状态的变化,观察寄存输出状态变化是否发生在CP脉冲的上升沿。

(3)右移:清零后,令 =1, S1=0 S0=1,由右移输入端SR送入二进制数码如0100,由CP端连续加4个脉冲,观察输出情况,记录之。

=1, S1=0 S0=1,由右移输入端SR送入二进制数码如0100,由CP端连续加4个脉冲,观察输出情况,记录之。

(4)左移:先清零或予至,再令 =1 S1=1,S0=0,由左移 输入端SL送入二进制数码如1111,连续加四个CP脉冲,观察输出端情况,记录之。

=1 S1=1,S0=0,由左移 输入端SL送入二进制数码如1111,连续加四个CP脉冲,观察输出端情况,记录之。

(5)保持:寄存器予置任意4位二进制数码abcd,令 =1,S1=S0=0,加CP脉冲,观察寄存器输出状态,记录之。

=1,S1=S0=0,加CP脉冲,观察寄存器输出状态,记录之。

表8-2

2、环形计数器

自拟实验步骤.用并行送数法予置寄存器为某二进制数码(如0100),然后进行右移循环,观察寄存器输出端状态的变化,记入表8-3中。

表8-3

六、实验报告要求:

1.根据实验内容1的实验步骤完成表8-2。

2.根据实验内容2的完成表8-3,并画出4位环形计数器的状态转换图及波形图。

- 电子技术实验报告6—移位寄存器及其应用

- 数电6实验报告--移位寄存器及其应用

-

实验七 移位寄存器及其应用

实验七移位寄存器及其应用一、实验目的1.移位寄存器74LS194的逻辑功能及使用方法;2.熟悉4位移位寄存器的应用。二、实验预习要…

-

实验六 移位寄存器及其应用

实验六移位寄存器及其应用一实验目的1掌握中规模4位双向移位寄存器逻辑功能及使用方法2熟悉移位寄存器的应用实现数据的串行并行转换和构…

-

移位寄存器实验报告

移位寄存器实验报告一实验原理移位寄存器是用来寄存二进制数字信息并且能进行信息移位的时序逻辑电路根据移位寄存器存取信息的方式可分为串…

-

实验一、线性移位寄存器实验报告

实验一实验报告姓名何璟学号120xx60099实验日期20xx108一实验名称线性移位寄存器二实验目的1234了解线性移位寄存器产…

-

组成原理实验报告(运算器、通用寄存器、移位寄存器)

西安财经学院信息学院实验报告实验名称运算器实验通用寄存器实验移位寄存器实验实验室实验楼418实验日期20xx112920xx122…

-

eda 八位寄存器实验报告.doc

EDA实验报告设计学院物信学院班级电信一班学号11220xx01122姓名杨义指导老师漆为民目录实验题目3实验目的和要求3实验原理…

-

移位寄存器实验报告

移位寄存器实验报告424实验目的1掌握移位寄存器的工作原理2综合移位寄存器数码扫描电路在实验板上下载并验证结果3掌握电路仿真的基本…

-

实验8 移位寄存器实验报告

移位寄存器实验报告一实验原理移位寄存器是用来寄存二进制数字信息并且能进行信息移位的时序逻辑电路根据移位寄存器存取信息的方式可分为串…

-

实验七 移位寄存器及其应用

实验七移位寄存器及其应用一实验目的1掌握中规模4位双向移位寄存器逻辑功能及使用方法2熟悉移位寄存器的应用实现数据的串行并行转换和构…