实验一、线性移位寄存器实验报告

实验一、实验报告

姓名: 何璟 学号: 1208060099 实验日期:2014.10.8

一、实验名称: 线性移位寄存器

二、 实验目的

1、

2、

3、

4、 了解线性移位寄存器产生伪随机序列的原理。 伪随机寄存器的软件实现。 同一个反馈函数不同初始值下的输出序列。 同一个初始值在不同反馈函数下的输出序列。

三、 实验基本方法

用C语言编写一个32位线性移位寄存器,其输出的伪随机序列显示在屏幕上。

四、 实验步骤

1、 编程实现32位线性移位寄存器。

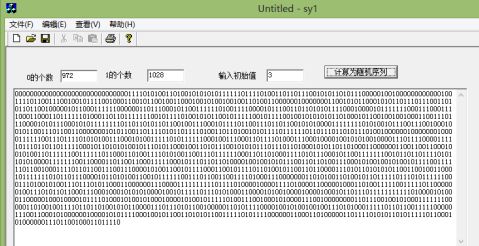

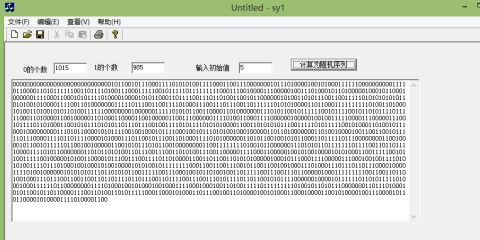

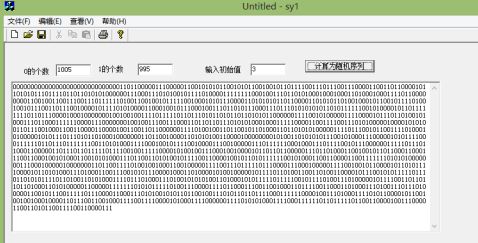

2、 观察输出序列前1000——2000位的随机性。

3、 改变反馈函数,再观察输出序列前1000——2000位的随机性。

4、 改变初始值,再观察输出序列前1000——2000位的随机性。

5、 将寄存器改成8位,找到一个m序列。**

五、 实验结果

1、 程序设计的思想,及程序原代码。

计算为随机序列按钮的程序代码

void CSy1View::OnButton1()

{

// TODO: Add your control notification handler code here

unsigned int lfsr,fsc=0x94411889;// 反馈函数

unsigned int t1,s,f,fs;

int i,j,c0=0,c1=0; // 0和1个数

UpdateData(TRUE);

lfsr=m_shuru;

m_ed="";

fs=lfsr&fsc;

for(i=0;i<2000;i++)

{

fs=lfsr&fsc;

t1=lfsr&0x80000000;

if(t1==0)

{

c0++;

m_ed = m_ed+"0";

}

else

{

m_ed = m_ed+"1";

c1++;

}

f=0; //反馈函数计算

for(j=0;j<32;j++)

{

if(fs&0x1!=0) //最低位

f=f^1;

else

f=f^0;

fs=fs/2;

}

lfsr=lfsr*2+f; //移位

}

m_c0.Format("%d",c0);

m_c1.Format("%d",c1);

UpdateData(FALSE);

}

改变反馈函数

void CSy1View::OnButton1()

{

// TODO: Add your control notification handler code here unsigned int lfsr,fsc=0x23193324;//反馈函数 unsigned int t1,s,f,fs;

int i,j,c0=0,c1=0; // 0和1个数

UpdateData(TRUE);

lfsr=m_shuru;

m_ed="";

fs=lfsr&fsc;

for(i=0;i<2000;i++)

{

} fs=lfsr&fsc; t1=lfsr&0x80000000; if(t1==0) { c0++; m_ed = m_ed+"0"; } else { m_ed = m_ed+"1"; c1++; } f=0; //反馈函数计算 for(j=0;j<32;j++) { if(fs&0x1!=0) //最低位 f=f^1; else f=f^0; fs=fs/2; } lfsr=lfsr*2+f; //移位 } m_c0.Format("%d",c0); m_c1.Format("%d",c1); UpdateData(FALSE);

2、 报告观察结果。

改变初始值

改变反馈函数

3、 对观察结果的分析。

4、 分析8位寄存器产生的m序列。*** 打**号的选做。

第二篇:实验十一移位寄存器实验报告

实验十一--移位寄存器实验报告 姓名: 洪至远 学号: 3100104624 专业: 工科信息1015 课程名称:逻辑与计算机设计基础实验

实验时间: 011-12-6 2同组学生姓名:谢志聪 指导老师: 蒋方炎,陆汉权 实验地点: 紫金港东4-509

一、实验目的和要求

1、掌握移位寄存器的工作原理及设计方法。

2、掌握串、并数据转换的概念与方法。

3、了解序列信号在CPU控制器设计中的应用。

二、实验内容和原理

实验内容:

1、用Verilog语言采用结构化描述方法设计一个16位带并行输入的右移移位寄存器。

2、在xCal上增加串行、并行输入功能。

实验原理:

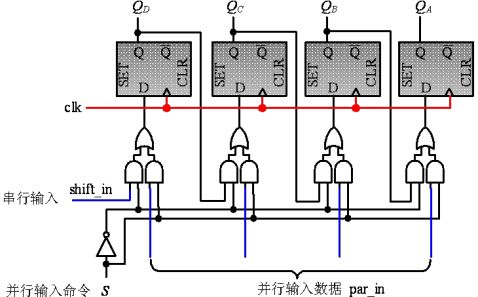

1、带并行置入的移位寄存器

移位寄存器:每来一个时钟脉冲,寄存器中的数据按顺序向左或向右移动一位。 -必须采用主从触发器或边沿触发器

-不能采用电平触发器

数据移动方式:左移、右移。 数据输入输出方式。 -串行输入,串行输出 -串行输入,并行输出

-并行输入,串行输出

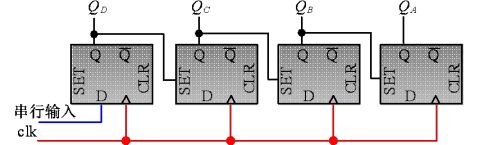

2、串行输入的移位寄存器

使用D触发器,可构成串行输入的移位寄存器

第1页/共14页

3、带并行输入的右移移位寄存器

数据输入移位寄存器的方式:串行输入、并行输入。

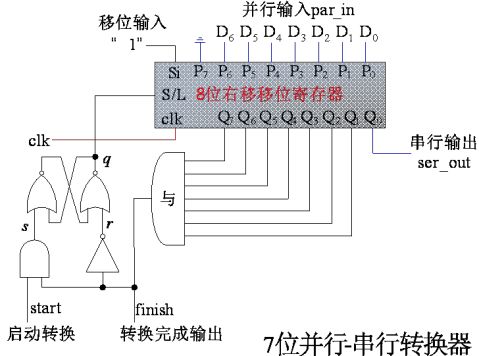

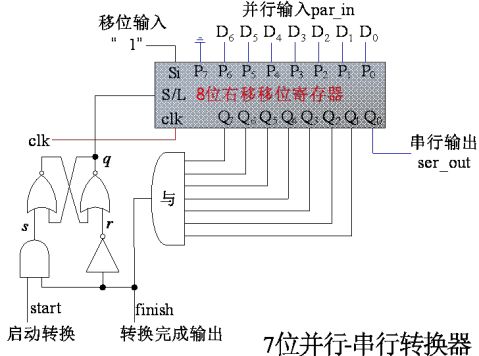

4、并行-串行转换器

没有启动命令时:

有启动命令时:

第2页/共14页

三、主要仪器设备

1、装有ISE的计算机系统 1台

2、Spartan III 实验板 1套

四、操作方法与实验步骤

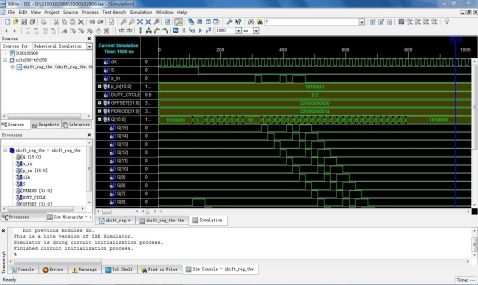

1、对移位寄存器模块波形仿真

实验步骤:

(1)、用Verilog HDL语言,采用结构化描述方法设计一个16位带并行输入的右移移位寄存器。

(2)、编写该移位寄存器的代码模块shift_reg。

(3)、针对该模块,编写波形仿真输入代码。

(4)、进行波形仿真,并分析仿真结果是否正确。

源代码: module shift_reg(clk, S, s_in, p_in, Q);

input wire clk, S, s_in;

input wire [15:0] p_in;

output wire [15:0] Q;

wire [15:0] D;

wire nS;

FD FDQ0(.C(clk), .D(D[0]), .Q(Q[0])),

FDQ1(.C(clk), .D(D[1]), .Q(Q[1])),

FDQ2(.C(clk), .D(D[2]), .Q(Q[2])),

FDQ3(.C(clk), .D(D[3]), .Q(Q[3])),

FDQ4(.C(clk), .D(D[4]), .Q(Q[4])),

FDQ5(.C(clk), .D(D[5]), .Q(Q[5])),

FDQ6(.C(clk), .D(D[6]), .Q(Q[6])),

第3页/共14页

FDQ7(.C(clk), .D(D[7]), .Q(Q[7])), FDQ8(.C(clk), .D(D[8]), .Q(Q[8])), FDQ9(.C(clk), .D(D[9]), .Q(Q[9])), FDQ10(.C(clk), .D(D[10]), .Q(Q[10])), FDQ11(.C(clk), .D(D[11]), .Q(Q[11])), FDQ12(.C(clk), .D(D[12]), .Q(Q[12])), FDQ13(.C(clk), .D(D[13]), .Q(Q[13])), FDQ14(.C(clk), .D(D[14]), .Q(Q[14])), FDQ15(.C(clk), .D(D[15]), .Q(Q[15]));

OR2 D0_L(.I0(L_0), .I1(R_0), .O(D[0])), D1_L(.I0(L_1), .I1(R_1), .O(D[1])), D2_L(.I0(L_2), .I1(R_2), .O(D[2])), D3_L(.I0(L_3), .I1(R_3), .O(D[3])), D4_L(.I0(L_4), .I1(R_4), .O(D[4])), D5_L(.I0(L_5), .I1(R_5), .O(D[5])), D6_L(.I0(L_6), .I1(R_6), .O(D[6])), D7_L(.I0(L_7), .I1(R_7), .O(D[7])), D8_L(.I0(L_8), .I1(R_8), .O(D[8])), D9_L(.I0(L_9), .I1(R_9), .O(D[9])),

D10_L(.I0(L_10), .I1(R_10), .O(D[10])), D11_L(.I0(L_11), .I1(R_11), .O(D[11])), D12_L(.I0(L_12), .I1(R_12), .O(D[12])), D13_L(.I0(L_13), .I1(R_13), .O(D[13])), D14_L(.I0(L_14), .I1(R_14), .O(D[14])), D15_L(.I0(L_15), .I1(R_15), .O(D[15]));

AND2 L0_L(.I0(Q[1]), .I1(nS), .O(L_0)), L1_L(.I0(Q[2]), .I1(nS), .O(L_1)), L2_L(.I0(Q[3]), .I1(nS), .O(L_2)), L3_L(.I0(Q[4]), .I1(nS), .O(L_3)), L4_L(.I0(Q[5]), .I1(nS), .O(L_4)), L5_L(.I0(Q[6]), .I1(nS), .O(L_5)), L6_L(.I0(Q[7]), .I1(nS), .O(L_6)), L7_L(.I0(Q[8]), .I1(nS), .O(L_7)), L8_L(.I0(Q[9]), .I1(nS), .O(L_8)), L9_L(.I0(Q[10]), .I1(nS), .O(L_9)), L10_L(.I0(Q[11]), .I1(nS), .O(L_10)), L11_L(.I0(Q[12]), .I1(nS), .O(L_11)), L12_L(.I0(Q[13]), .I1(nS), .O(L_12)), L13_L(.I0(Q[14]), .I1(nS), .O(L_13)), L14_L(.I0(Q[15]), .I1(nS), .O(L_14)), L15_L(.I0(s_in), .I1(nS), .O(L_15));

AND2 R0_L(.I0(p_in[0]), .I1(S), .O(R_0)), R1_L(.I0(p_in[1]), .I1(S), .O(R_1)), R2_L(.I0(p_in[2]), .I1(S), .O(R_2)), R3_L(.I0(p_in[3]), .I1(S), .O(R_3)), R4_L(.I0(p_in[4]), .I1(S), .O(R_4)), R5_L(.I0(p_in[5]), .I1(S), .O(R_5)), R6_L(.I0(p_in[6]), .I1(S), .O(R_6)), R7_L(.I0(p_in[7]), .I1(S), .O(R_7)), R8_L(.I0(p_in[8]), .I1(S), .O(R_8)), R9_L(.I0(p_in[9]), .I1(S), .O(R_9)), R10_L(.I0(p_in[10]), .I1(S), .O(R_10)), R11_L(.I0(p_in[11]), .I1(S), .O(R_11)), R12_L(.I0(p_in[12]), .I1(S), .O(R_12)), R13_L(.I0(p_in[13]), .I1(S), .O(R_13)), R14_L(.I0(p_in[14]), .I1(S), .O(R_14)), R15_L(.I0(p_in[15]), .I1(S), .O(R_15)); INV nS_L(.I(S), .O(nS));

第4页/共14页

endmodule

2、在多功能计算器中加入串行、并行输入功能部分程序

实验步骤:

(1)、设计16位带并行输入的右移移位寄存器。

(2)、增加到create_operands模块中。

(3)、修改相关代码。

(4)、修改ucf文件。

(5)、下载并验证。

源代码:

module top(input wire clk, input wire [3:0]btn_in, input wire

[7:0]switch, output wire [3:0]anode, output wire [7:0]segment);

wire [15:0]op1;

wire [15:0]op2;

wire [15:0]result;

reg [15:0]display_num;

wire [3:0]btn_out;

wire [15:0] disp_counter;

wire clk_1s;

display m0(clk, display_num, anode, segment); //display module

calculate_result m1(btn_out[3:0], op1, op2, result); //calculate result create_oprands m2(switch[7:0], btn_out[3:0], op1, op2); //generate clock_1s m3(clk,clk_1s);

counter_16_rev m4((clk_1ms&btn_out[0]),switch[2],disp_counter); clock_24h m5(clk_1ms&btn_out[1],disp_clock);

timer_1ms m6(clk, clk_1ms);

pbdebounce p0(clk,btn_in[0],btn_out[0]);

pbdebounce p1(clk,btn_in[1],btn_out[1]);

pbdebounce p2(clk,btn_in[2],btn_out[2]);

pbdebounce p3(clk,btn_in[3],btn_out[3]);

always @* begin

case (switch[1:0])

2'b01: display_num = op1; //operand 1

2'b10: display_num = op2; //operand 2

2'b00: display_num = result; //result

2'b11: begin

if(btn_out[1:0]==2'b01)

display_num=disp_counter;

else if(btn_out[1:0]==2'b10)

display_num=disp_clock;

end

endcase

end

endmodule

module create_oprands(switch,btn,op1,op2);

input [7:0] switch;

input [3:0] btn;

output [15:0] op1,op2;

reg [15:0] op1,op2;

第5页/共14页

wire [15:0] out_inc1,out_inc2,out_shift1,out_shift2;

initial begin

op1=16'b1010_1010_1010_1010;//AAAA

op2=16'b1011_1011_1011_1011;//BBBB

end

btn_increment m0(btn[3:0], switch[1:0], out_inc1, out_inc2);

shift_reg_16 m1(btn[2:0], switch[3:0],switch[7:4], out_shift1, out_shift2);

always @* begin

if(switch[1:0] == 2'b01)

case(switch[3:2])

2'b00:op1 = out_inc1;

2'b01:op1 = out_shift1;

endcase

else if(switch[1:0] == 2'b10)

case(switch[3:2])

2'b00:op2 = out_inc2;

2'b01:op2 = out_shift2;

endcase

end

endmodule

module btn_increment(input wire [3:0]btn, input wire [1:0]switch, output reg [15:0]out_inc1, output reg [15:0]out_inc2);

always @(posedge btn[0])begin

if(switch[1:0] == 4'b01) out_inc1[ 3: 0]<= out_inc1[ 3: 0] + 4'd1; else if(switch [1:0] == 4'b10)out_inc2[ 3: 0]<= out_inc2[ 3: 0] + 4'd1; end

always @(posedge btn[1])begin

if(switch[1:0] == 4'b01) out_inc1[ 7: 4]<= out_inc1[ 7: 4] + 4'd1; else if(switch[1:0] == 4'b10) out_inc2[ 7: 4]<=out_inc2[ 7: 4] + 4'd1; end

always @(posedge btn[2])begin

if(switch[1:0] == 4'b01) out_inc1[ 11: 8]<= out_inc1[ 11: 8] + 4'd1; else if(switch[1:0] == 4'b10) out_inc2[ 11: 8]<= out_inc2[ 11: 8] + 4'd1; end

always @(posedge btn[3])begin

if(switch[1:0] == 4'b01) out_inc1[ 15: 12]<= out_inc1[ 15: 12] + 4'd1; else if(switch[1:0] == 4'b10) out_inc2[ 15: 12]<= out_inc2[ 15: 12] + 4'd1;

end

endmodule

module shift_reg_16( input wire [2:0]btn, input wire [3:0]switch, input wire

[3:0]p_in, output reg [15:0]op_out1, output reg [15:0]op_out2); wire [15:0] Q1,Q2;

wire clk1 = btn[1]&switch[2]&~switch[3]&switch[0]&~switch[1];

wire clk2 = btn[1]&switch[2]&~switch[3]&switch[1]&~switch[0];

shift_reg sr1(clk1, btn[2], btn[0], {4{p_in[0],p_in[1],p_in[2],p_in[3]}}, Q1);

shift_reg sr2(clk2, btn[2], btn[0], {4{p_in[0],p_in[1],p_in[2],p_in[3]}}, Q2);

always @* begin

if(switch == 4'b0101) op_out1[15:0] = Q1[15:0];

else if(switch == 4'b0110) op_out2[15:0] = Q2[15:0];

end

第6页/共14页

endmodule

module shift_reg(clk, S, s_in, p_in, Q); input wire clk, S, s_in;

input wire [15:0] p_in;

output wire [15:0] Q;

wire [15:0] D;

wire nS;

FD FDQ0(.C(clk), .D(D[0]), .Q(Q[0])), FDQ1(.C(clk), .D(D[1]), .Q(Q[1])), FDQ2(.C(clk), .D(D[2]), .Q(Q[2])), FDQ3(.C(clk), .D(D[3]), .Q(Q[3])), FDQ4(.C(clk), .D(D[4]), .Q(Q[4])), FDQ5(.C(clk), .D(D[5]), .Q(Q[5])), FDQ6(.C(clk), .D(D[6]), .Q(Q[6])), FDQ7(.C(clk), .D(D[7]), .Q(Q[7])), FDQ8(.C(clk), .D(D[8]), .Q(Q[8])), FDQ9(.C(clk), .D(D[9]), .Q(Q[9])), FDQ10(.C(clk), .D(D[10]), .Q(Q[10])), FDQ11(.C(clk), .D(D[11]), .Q(Q[11])), FDQ12(.C(clk), .D(D[12]), .Q(Q[12])), FDQ13(.C(clk), .D(D[13]), .Q(Q[13])), FDQ14(.C(clk), .D(D[14]), .Q(Q[14])), FDQ15(.C(clk), .D(D[15]), .Q(Q[15]));

OR2 D0_L(.I0(L_0), .I1(R_0), .O(D[0])), D1_L(.I0(L_1), .I1(R_1), .O(D[1])), D2_L(.I0(L_2), .I1(R_2), .O(D[2])), D3_L(.I0(L_3), .I1(R_3), .O(D[3])), D4_L(.I0(L_4), .I1(R_4), .O(D[4])), D5_L(.I0(L_5), .I1(R_5), .O(D[5])), D6_L(.I0(L_6), .I1(R_6), .O(D[6])), D7_L(.I0(L_7), .I1(R_7), .O(D[7])), D8_L(.I0(L_8), .I1(R_8), .O(D[8])), D9_L(.I0(L_9), .I1(R_9), .O(D[9])),

D10_L(.I0(L_10), .I1(R_10), .O(D[10])), D11_L(.I0(L_11), .I1(R_11), .O(D[11])), D12_L(.I0(L_12), .I1(R_12), .O(D[12])), D13_L(.I0(L_13), .I1(R_13), .O(D[13])), D14_L(.I0(L_14), .I1(R_14), .O(D[14])), D15_L(.I0(L_15), .I1(R_15), .O(D[15]));

AND2 L0_L(.I0(Q[1]), .I1(nS), .O(L_0)), L1_L(.I0(Q[2]), .I1(nS), .O(L_1)), L2_L(.I0(Q[3]), .I1(nS), .O(L_2)), L3_L(.I0(Q[4]), .I1(nS), .O(L_3)), L4_L(.I0(Q[5]), .I1(nS), .O(L_4)), L5_L(.I0(Q[6]), .I1(nS), .O(L_5)), L6_L(.I0(Q[7]), .I1(nS), .O(L_6)), L7_L(.I0(Q[8]), .I1(nS), .O(L_7)), L8_L(.I0(Q[9]), .I1(nS), .O(L_8)), L9_L(.I0(Q[10]), .I1(nS), .O(L_9)), L10_L(.I0(Q[11]), .I1(nS), .O(L_10)), L11_L(.I0(Q[12]), .I1(nS), .O(L_11)), L12_L(.I0(Q[13]), .I1(nS), .O(L_12)), L13_L(.I0(Q[14]), .I1(nS), .O(L_13)), L14_L(.I0(Q[15]), .I1(nS), .O(L_14)), L15_L(.I0(s_in), .I1(nS), .O(L_15));

AND2 R0_L(.I0(p_in[0]), .I1(S), .O(R_0)),

第7页/共14页

R1_L(.I0(p_in[1]), .I1(S), .O(R_1)),

R2_L(.I0(p_in[2]), .I1(S), .O(R_2)),

R3_L(.I0(p_in[3]), .I1(S), .O(R_3)),

R4_L(.I0(p_in[4]), .I1(S), .O(R_4)),

R5_L(.I0(p_in[5]), .I1(S), .O(R_5)),

R6_L(.I0(p_in[6]), .I1(S), .O(R_6)),

R7_L(.I0(p_in[7]), .I1(S), .O(R_7)),

R8_L(.I0(p_in[8]), .I1(S), .O(R_8)),

R9_L(.I0(p_in[9]), .I1(S), .O(R_9)),

R10_L(.I0(p_in[10]), .I1(S), .O(R_10)),

R11_L(.I0(p_in[11]), .I1(S), .O(R_11)),

R12_L(.I0(p_in[12]), .I1(S), .O(R_12)),

R13_L(.I0(p_in[13]), .I1(S), .O(R_13)),

R14_L(.I0(p_in[14]), .I1(S), .O(R_14)),

R15_L(.I0(p_in[15]), .I1(S), .O(R_15));

INV nS_L(.I(S), .O(nS));

endmodule

module calculate_result(btn,op1,op2,result);

input [3:0] btn;

input [15:0] op1;

input [15:0] op2;

output reg [15:0] result;

wire [15:0] add_sub_result;

add_sub_16bits m0(op1, op2, btn[1], add_sub_result, co);

always @(btn) begin

if(btn[0] ==1 || btn[1] == 1)

result = add_sub_result;

if(btn[2] == 1)

result = op1 & op2;

if(btn[3] == 1)

result = op1 | op2;

end

endmodule

module clock_1s(clk,clk_1s);

input wire clk;

output reg clk_1s;

reg [31:0] cnt;

always @ (posedge clk)begin

if (cnt < 25_000_000)begin//25M*(1/50M)S=0.5S

cnt <= cnt+ 1;

end

else begin

cnt<= 0;

clk_1s<=~clk_1s;// clk_1s==1的时间=0.5s

end // clk_1s==0的时间=0.5s

end //周期T=1S

endmodule

module m_gen_min(input wire clk_sec,output reg clk_hour,output reg[3:0] min_low,output reg[3:0] min_high);

reg[15:0] cnt;

always @(posedge clk_sec) begin

if(clk_hour==1)

clk_hour=0;

if(cnt==59) begin

cnt=0;

if(min_low==9) begin

min_low=0;

第8页/共14页

if(min_high==5) begin

min_high=0;

clk_hour=1;

end else

min_high=min_high+1;

end else

min_low=min_low+1;

end else

cnt=cnt+1;

end

endmodule

module m_gen_hour(input wire clk_hour, output reg clk_day, output reg[3:0] hour_low, output reg[3:0] hour_high);

always @(posedge clk_hour)

if(hour_low==3&&hour_high==2)begin

hour_low=0;

hour_high=0;

clk_day=~clk_day;

end else if(hour_low==9)begin

hour_low=0;

hour_high=hour_high+1;

end else

hour_low=hour_low+1;

endmodule

module clock_24h(input wire clk_sec, output wire[15:0]digit); wire clk_hour,clk_day;

wire [3:0]min_low,min_high,hour_low,hour_high;

m_gen_min MIN(clk_sec,clk_hour,min_low,min_high);

m_gen_hour HOUR(clk_hour,clk_day,hour_low,hour_high);

assign digit[15:12]=hour_high[3:0];

assign digit[11:8]=hour_low[3:0];

assign digit[7:4]=min_high[3:0];

assign digit[3:0]=min_low[3:0];

endmodule

module counter_16_rev(clk,s,cnt);

input wire clk,s;

output reg [15:0]cnt;

always@(posedge clk)begin

if(s)

cnt<=cnt+1;

else

cnt<=cnt-1;

end

endmodule

module add_sub_16bits(input wire[16:1] A,input wire[16:1] B,input wire Ci,output wire[16:1] S,output wire Co);

wire [15:1]ctemp;

wire [16:1]bo;

assign bo={Ci,Ci,Ci,Ci,Ci,Ci,Ci,Ci,Ci,Ci,Ci,Ci,Ci,Ci,Ci,Ci}^B; adder_1bit A1_2(A[1], bo[1], Ci,S[1],ctemp[1]),

A1_3(A[2], bo[2], ctemp[1],S[2],ctemp[2]),

A1_4(A[3], bo[3], ctemp[2],S[3],ctemp[3]),

A1_5(A[4], bo[4], ctemp[3],S[4],ctemp[4]),

第9页/共14页

A1_6(A[5], bo[5], ctemp[4],S[5],ctemp[5]),

A1_7(A[6], bo[6], ctemp[5],S[6],ctemp[6]),

A1_8(A[7], bo[7], ctemp[6],S[7],ctemp[7]),

A1_9(A[8], bo[8], ctemp[7],S[8],ctemp[8]),

A1_10(A[9], bo[9], ctemp[8],S[9],ctemp[9]),

A1_11(A[10], bo[10], ctemp[9],S[10],ctemp[10]),

A1_12(A[11], bo[11], ctemp[10],S[11],ctemp[11]),

A1_13(A[12], bo[12], ctemp[11],S[12],ctemp[12]),

A1_14(A[13], bo[13], ctemp[12],S[13],ctemp[13]),

A1_15(A[14], bo[14], ctemp[13],S[14],ctemp[14]),

A1_16(A[15], bo[15], ctemp[14],S[15],ctemp[15]),

A1_17(A[16], bo[16], ctemp[15],S[16],Co);

endmodule

module adder_1bit(input wire a,input wire b,input wire ci, output wire s, output wire co);

wire c1,c2,c3,s1;

and (c1,a,b),

(c2,b,ci),

(c3,a,ci);

xor (s1,a,b),

(s,s1,ci);

or (co,c1,c2,c3);

endmodule

module display(

input wire clk,

input wire [15:0] digit,//显示的数据

output reg [ 3:0] node,

output reg [ 7:0] segment);//七段+小数点

reg [3:0] code = 4'b0;

reg [15:0] count = 15'b0;

always @(posedge clk) begin

case (count[15:14])

2'b00 : begin

node <= 4'b1110;

code <= digit[3:0];

end

2'b01 : begin

node <= 4'b1101;

code <= digit[7:4];

end

2'b10 : begin

node <= 4'b1011;

code <= digit[11:8];

end

2'b11 : begin

node <= 4'b0111;

code <= digit[15:12];

end

endcase

case (code)

4'b0000: segment <= 8'b11000000;

4'b0001: segment <= 8'b11111001;

4'b0010: segment <= 8'b10100100;

4'b0011: segment <= 8'b10110000;

4'b0100: segment <= 8'b10011001;

4'b0101: segment <= 8'b10010010;

第10页/共14页

4'b0110: segment <= 8'b10000010; 4'b0111: segment <= 8'b11111000; 4'b1000: segment <= 8'b10000000; 4'b1001: segment <= 8'b10010000; 4'b1010: segment <= 8'b10001000; 4'b1011: segment <= 8'b10000011; 4'b1100: segment <= 8'b11000110; 4'b1101: segment <= 8'b10100001; 4'b1110: segment <= 8'b10000110; 4'b1111: segment <= 8'b10001110; default: segment <= 8'b00000000; endcase

count <= count + 1;

end

endmodule

module pbdebounce

(input wire clk,

input wire button,

output reg pbreg);

reg [7:0] pbshift;

wire clk_1ms;

timer_1ms m0(clk, clk_1ms);

always@(posedge clk_1ms) begin pbshift=pbshift<<1;//左移1位

pbshift[0]=button;

if (pbshift==0)

pbreg=0;

if (pbshift==8'hFF)// pbshift八位全为1 pbreg=1;

end

endmodule

module timer_1ms

(input wire clk,

output reg clk_1ms);

reg [15:0] cnt;

initial begin

cnt [15:0] <=0;

clk_1ms <= 0;

end

always@(posedge clk)

if(cnt>=25000) begin

cnt<=0;

clk_1ms <= ~clk_1ms;

end

else begin

cnt<=cnt+1;

end

endmodule

第11页/共14页

ucf引脚分配代码:

net "clk" loc = "T9";

net "btn_in[0]" loc="M13"; net "btn_in[1]" loc="M14"; net "btn_in[2]"

loc="L13"; net "btn_in[3]" loc="L14"; net "switch[0]" loc="F12"; net "switch[1]" loc="G12"; net "switch[2]" loc="H14"; net "switch[3]" loc="H13"; net "switch[4]" loc="J14"; net "switch[5]" loc="J13"; net "switch[6]" loc="K14"; net "switch[7]" loc="K13"; net "segment[0]" loc = "E14"; net "segment[1]" loc = "G13"; net "segment[2]" loc = "N15"; net "segment[3]" loc = "P15"; net "segment[4]" loc = "R16"; net "segment[5]" loc = "F13"; net "segment[6]" loc = "N16"; net "segment[7]" loc = "P16"; net "anode[0]" loc = "D14"; net "anode[1]" loc = "G14"; net "anode[2]" loc = "F14"; net "anode[3]" loc = "E13";

五、实验结果与分析

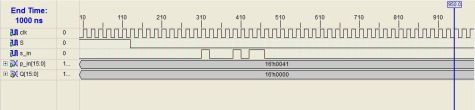

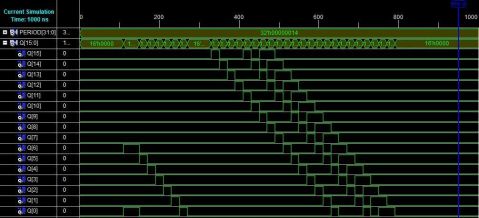

1、波形仿真

输入波形:

输出波形:

第12页/共14页

第13页/共14页

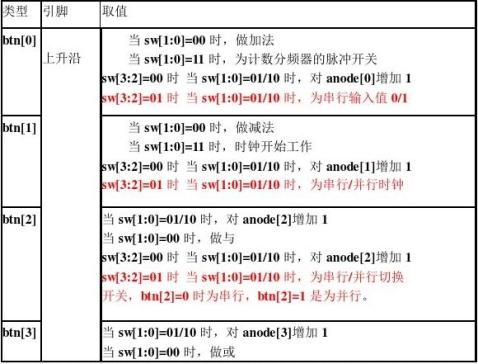

2、在多功能计算器中加入串行、并行输入功能

当实验板上从右往左的拨动开关分别为关开关开关开时,按下实验板上从右往左数第二个按钮,进行右移移入1的移位计算,最后结果为FFFF;按下实验板上从右往左数第一个按钮和第二个按钮,进行右移移入0的移位计算,最后结果为0000。 3、实验分析:

波形仿真中,clk是时钟,每一次上升沿触发一次移位,S是移位寄存器的开关,S为低电平时开始移位,s_in是右移移位时左边移入的情况,Q[0]-Q[15]代表16进制数各位上的情况,高电平为1,低电平为0。由右移移位寄存器的性质可知,仿真图形是正确的。

实验操作过程中,btn[n]为实验板上从右往左数第n+1个按钮。sw[m:n]=XY,Y=0或1表示实验板上从右往左数第n+1个拨动开关拨在下或上,X=0或1表示实验板上从右往左数第m+1个拨动开关拨在下或上。

六、讨论、心得

这次实验比较难,主要是因为对移位寄存器和串、并行的了解不够透彻。这次实验让我对移位寄存器有了更深入的了解,对结构化描述方法也有了更深入的认识。在做实验时,我还不能够快速并且敏锐地发现错误,导致我做实验的速度比较慢,这也是我需要努力的地方。

第14页/共14页

-

移位寄存器实验报告

移位寄存器实验报告一实验原理移位寄存器是用来寄存二进制数字信息并且能进行信息移位的时序逻辑电路根据移位寄存器存取信息的方式可分为串…

-

移位寄存器实验报告

移位寄存器实验报告一、实验目的和要求掌握移位寄存器的工作原理及设计方法掌握串、并数据转换的概念与方法了解序列信号在CPU控制器设计…

-

实验一、线性移位寄存器实验报告

实验一实验报告姓名何璟学号120xx60099实验日期20xx108一实验名称线性移位寄存器二实验目的1234了解线性移位寄存器产…

-

实验8 移位寄存器实验报告

移位寄存器实验报告一实验原理移位寄存器是用来寄存二进制数字信息并且能进行信息移位的时序逻辑电路根据移位寄存器存取信息的方式可分为串…

-

移位寄存器实验报告

移位寄存器实验报告424实验目的1掌握移位寄存器的工作原理2综合移位寄存器数码扫描电路在实验板上下载并验证结果3掌握电路仿真的基本…

-

组成原理实验报告(运算器、通用寄存器、移位寄存器)

西安财经学院信息学院实验报告实验名称运算器实验通用寄存器实验移位寄存器实验实验室实验楼418实验日期20xx112920xx122…

-

实验8 移位寄存器实验报告

移位寄存器实验报告一实验原理移位寄存器是用来寄存二进制数字信息并且能进行信息移位的时序逻辑电路根据移位寄存器存取信息的方式可分为串…

-

移位寄存器实验报告

移位寄存器实验报告一、实验目的和要求掌握移位寄存器的工作原理及设计方法掌握串、并数据转换的概念与方法了解序列信号在CPU控制器设计…

- 数电6实验报告--移位寄存器及其应用

- 电子技术实验报告6—移位寄存器及其应用

-

eda 八位寄存器实验报告.doc

EDA实验报告设计学院物信学院班级电信一班学号11220xx01122姓名杨义指导老师漆为民目录实验题目3实验目的和要求3实验原理…