移位寄存器实验报告

移位寄存器实验报告

一、实验目的和要求

掌握移位寄存器的工作原理及设计方法

掌握串、并数据转换的概念与方法

了解序列信号在CPU控制器设计中的应用

二、实验内容和原理

2.1 实验原理

带并行置入的移位寄存器

移位寄存器:每来一个时钟脉冲,寄存器中的数据按顺序向左或向右移动一位

必须采用主从触发器或边沿触发器

不能采用电平触发器

数据移动方式:左移、右移

数据输入输出方式

串行输入,串行输出

串行输入,并行输出

并行输入,串行输出

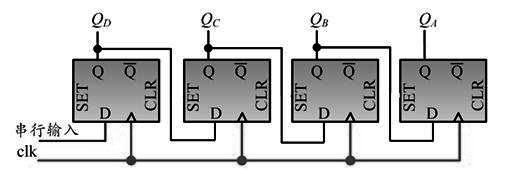

串行输入的移位寄存器

使用D触发器,可构成串行输入的移位寄存器

2.2 标题

<正文>

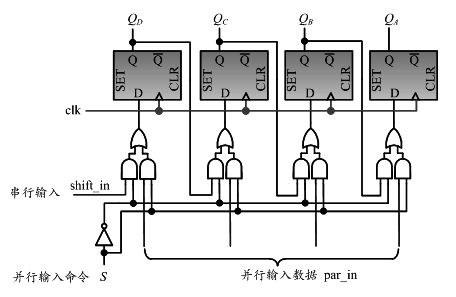

带并行输入的右移移位寄存器

数据输入移位寄存器的方式:串行输入、并行输入

带并行输入的8位右移移位寄存器

module shift_reg(clk, S, s_in, p_in, Q);

input wire clk, S, s_in;

input wire [7:0] p_in;

output wire [7:0] Q;

wire [7:0] D;

wire nS;

FD FDQ0(.C(clk), .D(D[0]), .Q(Q[0])),

FDQ1(.C(clk), .D(D[1]), .Q(Q[1])),

FDQ2(.C(clk), .D(D[2]), .Q(Q[2])),

FDQ3(.C(clk), .D(D[3]), .Q(Q[3])),

FDQ4(.C(clk), .D(D[4]), .Q(Q[4])),

FDQ5(.C(clk), .D(D[5]), .Q(Q[5])),

FDQ6(.C(clk), .D(D[6]), .Q(Q[6])),

FDQ7(.C(clk), .D(D[7]), .Q(Q[7]));

OR2 D0_L(.I0(L_0), .I1(R_0), .O(D[0])),

D1_L(.I0(L_1), .I1(R_1), .O(D[1])),

D2_L(.I0(L_2), .I1(R_2), .O(D[2])),

D3_L(.I0(L_3), .I1(R_3), .O(D[3])),

D4_L(.I0(L_4), .I1(R_4), .O(D[4])),

D5_L(.I0(L_5), .I1(R_5), .O(D[5])),

D6_L(.I0(L_6), .I1(R_6), .O(D[6])),

D7_L(.I0(L_7), .I1(R_7), .O(D[7]));

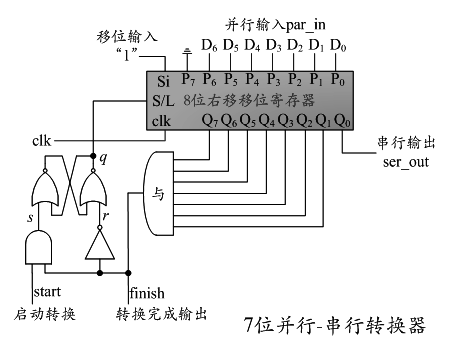

并行-串行转换器

没有启动命令时

并行-串行转换器

2.1 实验内容

用Verilog HDL语言,采用结构化描述方法设计一个8位带并行输入的右移移位寄存器。

编写该移位寄存器的代码模块shift_reg

针对该模块,编写波形仿真输入代码

进行波形仿真,并分析仿真结果是否正确

设计16位带并行输入的右移移位寄存器。

2、增加到计算器模块中。

3、修改相关代码。

4、修改ucf文件。

5、下载并验证。

三、主要仪器设备

必须采用编号样式,设备的数量和单位应对齐。示范如下:

1. xx开发板 1套

2. 装有ISE的PC机 1台

四、操作方法与实验步骤

修改TOP程序,添加移位寄存器

报告的第二、三、四部分是重点,请认真书写。

五、实验结果与分析

btn[1] CLK上升沿 作为移位和并行置数寄存器打入脉冲

六、讨论、心得

这次实验计算机下载到板上的时候出了问题,所以没能完全完成。

第二篇:8位移位寄存器

8位移位寄存器

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY shifter IS PORT ( data_in : IN STD_LOGIC_VECTOR(7 DOWNTO 0); --输入的数据 n : IN STD_LOGIC_VECTOR(2 DOWNTO 0); --移位的数量

dir : IN STD_LOGIC; --移动的方向 0:左 1:右 kind : IN STD_LOGIC_VECTOR(1 DOWNTO 0); --移动类型 00:算术移 01:逻辑移 10:循环移

clock : IN BIT; --手动时钟PULSE

data_out : OUT STD_LOGIC_VECTOR(7 DOWNTO 0) --移位的结果

); END shifter;

ARCHITECTURE behav of shifter IS BEGIN

PROCESS (data_in, n, dir, kind) VARIABLE x,y : STD_LOGIC_VECTOR(7 DOWNTO 0);

VARIABLE ctrl0,ctrl1,ctrl2 : STD_LOGIC_VECTOR (3 DOWNTO 0); BEGIN

IF (clock'EVENT AND clock = '1')THEN --产生控制向量ctrl

ctrl0 := n(0) & dir & kind(1) & kind(0); ctrl1 := n(1) & dir & kind(1) & kind(0); ctrl2 := n(2) & dir & kind(1) & kind(0);

CASE ctrl0 IS

WHEN "0000" | "0001" | "0010" | "0100" | "0101" | "0110" => x := data_in; --n=0时不移动 WHEN --算术左移1位 WHEN --逻辑左移1位 WHEN --循环左移1位 WHEN --算术右移1位 WHEN

"1000" "1001" "1010" "1100" "1101"

=> => => => =>

x x x x x

:= data_in(6 :=

DOWNTO 0) & 0) &

data_in(0); &

data_in(6 DOWNTO

0)

'0';

:= :=

data_in(6 data_in(7) :=

'0'

DOWNTO & &

data_in(7);

data_in(7 data_in(7

DOWNTO DOWNTO

1);

1);

--逻辑右移1位

WHEN

--循环右移1位 "1110" => x := data_in(0) & data_in(7 DOWNTO 1);

WHEN others => null;

END CASE;

CASE ctrl1 IS

WHEN "0000" | "0001" | "0010" | "0100" | "0101" | "0110" => y := x;

--n=0时不移动

WHEN

--算术左移2位 "1000" => y := x(5 DOWNTO 0) & x(0) & x(0);

WHEN "1001" => y := x(5 DOWNTO 0) & "00"; --逻辑左移2位

WHEN "1010" => y := x(5 DOWNTO 0) & x(7 DOWNTO 6); --循环左移2位

WHEN

--算术右移2位

WHEN

--逻辑右移2位 "1100" "1101" => y := y x(7) := & "00" x(7) & & x(7 DOWNTO DOWNTO 2); => x(7 2);

WHEN "1110" => y := x(1 DOWNTO 0) & x(7 DOWNTO 2); --循环右移2位

WHEN others => null;

END CASE;

CASE ctrl2 IS

WHEN "0000" | "0001" | "0010" | "0100" | "0101" | "0110" => data_out <= y;

--n=0时不移动

WHEN "1000" => data_out <= y(3 DOWNTO 0) & y(0) & y(0) & y(0) & y(0);

--算术左移4位

WHEN

--逻辑左移4位 "1001" => data_out <= y(3 DOWNTO 0) & "0000";

WHEN "1010" | "1110" => data_out <= y(3 DOWNTO 0) & y(7 DOWNTO 4); --循环左(右)移4位

WHEN "1100" => data_out <= y(7) & y(7) & y(7) & y(7) & y(7 DOWNTO 4);

--算术右移4位

WHEN "1101"

--逻辑右移4位 => data_out <= "0000" & y(7 DOWNTO 4);

WHEN others => null;

END CASE;

END IF;

END PROCESS;

END behav;

-

移位寄存器实验报告

移位寄存器实验报告一实验原理移位寄存器是用来寄存二进制数字信息并且能进行信息移位的时序逻辑电路根据移位寄存器存取信息的方式可分为串…

-

移位寄存器实验报告

移位寄存器实验报告一、实验目的和要求掌握移位寄存器的工作原理及设计方法掌握串、并数据转换的概念与方法了解序列信号在CPU控制器设计…

-

实验一、线性移位寄存器实验报告

实验一实验报告姓名何璟学号120xx60099实验日期20xx108一实验名称线性移位寄存器二实验目的1234了解线性移位寄存器产…

-

实验8 移位寄存器实验报告

移位寄存器实验报告一实验原理移位寄存器是用来寄存二进制数字信息并且能进行信息移位的时序逻辑电路根据移位寄存器存取信息的方式可分为串…

-

移位寄存器实验报告

移位寄存器实验报告424实验目的1掌握移位寄存器的工作原理2综合移位寄存器数码扫描电路在实验板上下载并验证结果3掌握电路仿真的基本…

-

实验一、线性移位寄存器实验报告

实验一实验报告姓名何璟学号120xx60099实验日期20xx108一实验名称线性移位寄存器二实验目的1234了解线性移位寄存器产…

-

组成原理实验报告(运算器、通用寄存器、移位寄存器)

西安财经学院信息学院实验报告实验名称运算器实验通用寄存器实验移位寄存器实验实验室实验楼418实验日期20xx112920xx122…

-

实验8 移位寄存器实验报告

移位寄存器实验报告一实验原理移位寄存器是用来寄存二进制数字信息并且能进行信息移位的时序逻辑电路根据移位寄存器存取信息的方式可分为串…

- 数电6实验报告--移位寄存器及其应用

- 电子技术实验报告6—移位寄存器及其应用

-

eda 八位寄存器实验报告.doc

EDA实验报告设计学院物信学院班级电信一班学号11220xx01122姓名杨义指导老师漆为民目录实验题目3实验目的和要求3实验原理…