EDA课程设计实验报告

课 程 设 计 报 告

课程名称 数字系统与逻辑设计

课题名称 16*16点阵显示

专 业 通信工程

班 级 1181

学 号

姓 名

指导教师

20##年 7月 2日

《数字系统与逻辑设计》课程设计任务书

一、设计目的

全面熟悉、掌握VHDL语言基本知识,掌握利用VHDL语言对常用的的组合逻辑电路和时序逻辑电路编程,把编程和实际结合起来,熟悉编制和调试程序的技巧,掌握分析结果的若干有效方法,进一步提高上机动手能力,培养使用设计综合电路的能力,养成提供文档资料的习惯和规范编程的思想。

二、设计要求

1、设计正确,方案合理。

2、程序精炼,结构清晰。

3、设计报告5000字以上,含程序设计说明,用户使用说明,源程序清单及程序框图。

4、上机演示。

5、有详细的文档。文档中包括设计思路、设计仿真程序、仿真结果及相应的分析与结论。

三、进度安排

第十八周 星期一: 课题讲解,查阅资料

星期二: 总体设计,详细设计

星期三: 编程,上机调试、修改程序

星期四: 上机调试、完善程序

星期五: 答辩

星期六-星期天:撰写课程设计报告

附:

课程设计报告装订顺序:封面、任务书、目录、正文、评分、附件(A4大小的图纸及程序清单)。

正文的格式:一级标题用3号黑体,二级标题用四号宋体加粗,正文用小四号宋体;行距为22。

正文的内容:一、课题的主要功能;二、课题的功能模块的划分(要求画出模块图);三、主要功能的实现;四、系统调试与仿真;五、总结与体会;六、附件(所有程序的原代码,要求对程序写出必要的注释);七、评分表。

目 录

一、 课题的主要功能............................................ 3

1.1问题描述................................................ 3

1.2 功能描述................................................ 4

二、 课题的功能模块的划分...................................... 4

2.1 系统的总体框图.......................................... 4

三、主要功能的实现............................................. 5

3.1 1 8进制加法器设计...................................... 5

3.2 2 16进制计数器设计..................................... 5

3.3 列驱动设计.............................................. 5

3.4 字体显示控制器.......................................... 5

3.5 顶层文件设计........................................... 5

四、 系统调试与仿真............................................ 6

4.1 程序仿真图............................................. 6

4.2 16*16 LED点阵显示引脚分配.............................. 8

4.3 程序运行结果............................................ 9

五、 总结与体会................................................ 9

六、 附件..................................................... 10

七、 课程设计评分表....................................................................................... 20

一、课题的主要功能

1.1问题描述

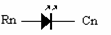

本实验主要完成汉字字符在LED 上的显示,16*16 扫描LED 点阵的工作原理与8 位扫描数码管类似,只是显示的方式与结果不一样而已。下面就本实验系统的16*16 点阵的工件原理做一些简单的说明。16*16 点阵由此256 个LED 通过排列组合而形成16 行*16 列的一个矩阵式的LED 阵列,俗称16*16 点阵。单个的LED 的电路如下图11-1 所示:

图11-1 单个LED 电路图

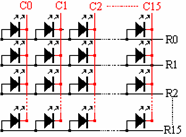

由上图可知,对于单个LED 的电路图当Rn 输入一个高电平,同时Cn 输入一个低电平时,电路形成一个回路,LED 发光。也就是LED 点阵对应的这个点被点亮。16*16 点阵也就是由16 行和16 列的LED 组成,其中每一行的所有16 个LED的Rn 端并联在一起,每一列的所有16 个LED 的Cn 端并联在一起。通过给Rn 输入一个高电平,也就相当于给这一列所有LED 输入了一个高电平,这时只要某个LED 的Cn 端输入一个低电平时,对应的LED 就会被点亮。具体的电路如下图11-2所示:

图11-2 16*16 点阵电路原理图

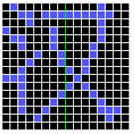

在点阵上显示一字符是根据其字符在点阵上的显示的点的亮灭来表示的,如下图11-3 所示:

图11-3 字符在点阵上的显示

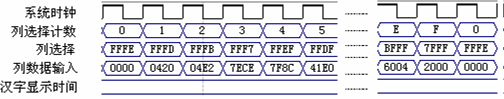

在上图中,显示的是一个“汉”字,只要将被“汉”字所覆盖的区域的点点亮,则在点阵中就会显示一个“汉”字。根据前面我们所介绍的点阵显示的原理,当我们选中第一列后,根据要显示汉字的第一列中所需要被点亮的点对应的Rn置为高电平,则在第一列中需要被点亮的点就会被点亮。依此类推,显示第二列、第三列……第N 列中需要被点亮的点。然后根据人眼的视觉原理,将每一列显示的点的间隔时间设为一定的值,那么我们就会感觉显示一个完整的不闪烁的汉字。同时也可以按照这个原理来显示其它的汉字。下图11-4 是一个汉字显示所需要的时序图:

图11-4 显示时序图

1.2功能描述

本实验的示例程序依次显示的是“湖南工程学院”,要求每隔一秒换下一个字显示。

二、课题的功能模块的划分

2.1 系统的总体框图

2-1 模块图

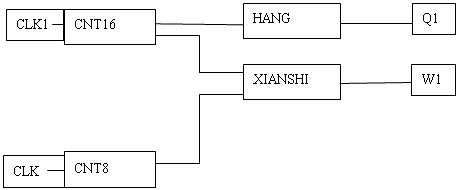

此程序分为五个模块,两个计数器和一个行驱动程序和一个显示字体控制程序,最后再加上一个顶层文件,用来连接前四个模块,程序简图如下:

图2-2 电路连接简图

三、主要功能的实现

3.1 1 8进制加法器设计

CNT8.vhd是8进制的计数器,其每计一次数,输出一个字。例如当计数为“000B”时显示“湖”,当计数为“001B”时显示“南”。给其脉冲周期为1S。

3.2 2 16进制计数器设计

CNT16.vhd是16进制的计数器,其输出端控制行和列驱动控制器的输出数据;

3.3 列驱动设计

HANG.vhd为列驱动控制器,该模块控制所亮的行,当输出为0001H时,给点阵的第一行高电平,输出为0010H时,给点阵的第二行高电平,依次类推,逐次给每行高电平。

3.4 字体显示控制器

XIANSHI.vhd为字体显示控制器,SHI控制的是所显示的字。例如当SHI为00H时,表示显示第一个字;当SHI为01H时,表示显示第二个字,依次类推。WEI控制所显示的为字的第几行,例如当WEI为0000B时,表示输出字的第一行文字信息;WEI为0001B时,表示输出字的第二行文字信息,依次类推。

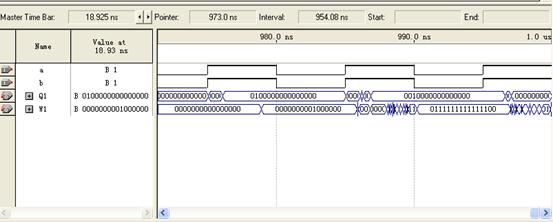

3.5 顶层文件设计

JUZHEN16.vhd是顶层文件设计,文件在实体中首先定义了顶层设计元件的端口信号,然后在architecture和begin之间利用component语句对准备调用的元件做了声明,并定义了c,d两个信号作为器件内部的连接线。最后利用端口映射语句PORT MAP()将两个计数器和列驱动,字体显示驱动连接起来构成一个完整的器件。

四、系统调试与仿真

4.1 程序仿真图

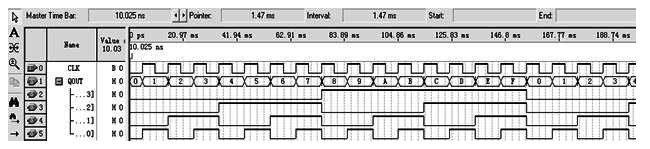

图4-1 CNT16.vhd仿真波形图

图4-2 HANG.vhd仿真波形图

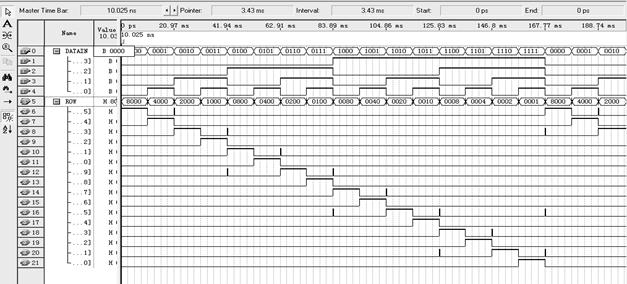

图4.3 顶层仿真图

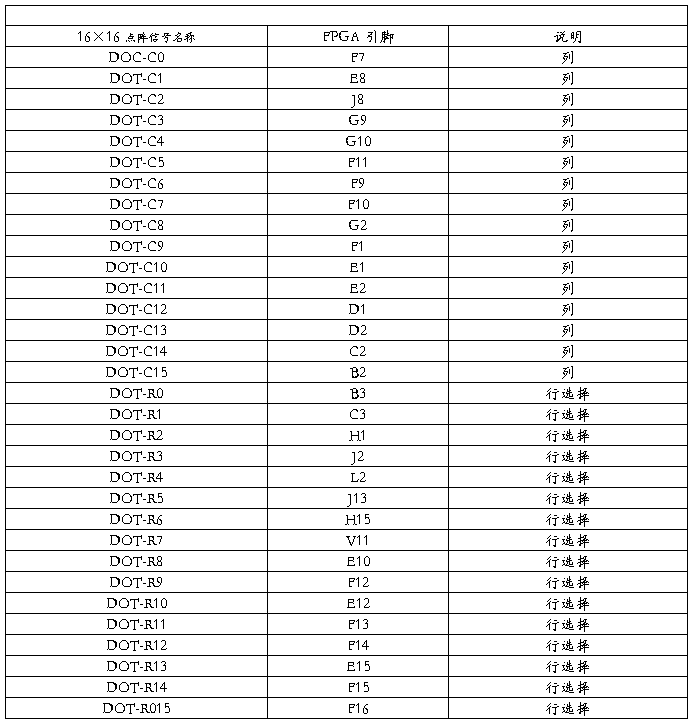

4.2 16*16 LED点阵显示引脚分配

时钟:

图4.4 引脚分配

4.3 程序运行结果

程序仿真完全正确后,线封锁引脚,然后连接硬件,再次编译,没有错误后下载程序到硬件之中,当拨码开关闭合时,得到点阵LED显示结果,其中每个汉字显示时间为一秒,一秒过后自动换下一个汉字,直到显示完“湖南工程学院”,再循环显示以上内容;当拨码开关断开时,点阵LED不显示任何内容

五、总结与体会

通过此次课程设计,使我更加扎实的掌握了有关EDA方面的知识,在设计过程中虽然遇到了一些问题,但经过一次又一次的思考,一遍又一遍的检查终于找出了原因所在,也暴露出了前期我在这方面的知识欠缺和经验不足。实践出真知,通过亲自动手制作,使我们掌握的知识不再是纸上谈兵。

过而能改,善莫大焉。在课程设计过程中,我们不断发现错误,不断改正,不断领悟,不断获取。最终的检测调试环节,本身就是在践行“过而能改,善莫大焉”的知行观。这次课程设计终于顺利完成了,在设计中遇到了很多问题,最后在老师的指导下,终于游逆而解。在今后社会的发展和学习实践过程中,一定要不懈努力,不能遇到问题就想到要退缩,一定要不厌其烦的发现问题所在,然后一一进行解决,只有这样,才能成功的做成想做的事,才能在今后的道路上劈荆斩棘,而不是知难而退,那样永远不可能收获成功,收获喜悦,也永远不可能得到社会及他人对你的认可!

课程设计诚然是一门专业课,给我很多专业知识以及专业技能上的提升,同时又是一门讲道课,一门辩思课,给了我许多道,给了我很多思,给了我莫大的空间。同时,设计让我感触很深。使我对抽象的理论有了具体的认识。通过这次课程设计,我掌握了LED点阵显示的原理及设计,进一步提高了用VHDL语言编程的能力。

我认为,在这学期的实验中,不仅培养了独立思考、动手操作的能力,在各种其它能力上也都有了提高。更重要的是,在实验课上,我们学会了很多学习的方法。而这是日后最实用的,真的是受益匪浅。要面对社会的挑战,只有不断的学习、实践,再学习、再实践。这对于我们的将来也有很大的帮助。以后,不管有多苦,我想我们都能变苦为乐,找寻有趣的事情,发现其中珍贵的事情。就像中国提倡的艰苦奋斗一样,我们都可以在实验结束之后变的更加成熟,会面对需要面对的事情。

回顾起此课程设计,至今我仍感慨颇多,从理论到实践,在这段日子里,可以说得是苦多于甜,但是可以学到很多很多的东西,同时不仅可以巩固了以前所学过的知识,而且学到了很多在书本上所没有学到过的知识。通过这次课程设计使我懂得了理论与实际相结合是很重要的,只有理论知识是远远不够的,只有把所学的理论知识与实践相结合起来,从理论中得出结论,才能真正为社会服务,从而提高自己的实际动手能力和独立思考的能力。在设计的过程中遇到问题,可以说得是困难重重,但可喜的是最终都得到了解决。

实验过程中,也对团队精神的进行了考察,让我们在合作起来更加默契,在成功后一起体会喜悦的心情。果然是团结就是力量,只有互相之间默契融洽的配合才能换来最终完美的结果。

此次设计也让我明白了思路即出路,有什么不懂不明白的地方要及时请教或上网查询,只要认真钻研,动脑思考,动手实践,就没有弄不懂的知识,收获颇丰。

六、附件

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY CNT8 IS

PORT( CLK1: IN STD_LOGIC;

QOUT : OUT STD_LOGIC_VECTOR(2 DOWNTO 0));

END ENTITY CNT8;

ARCHITECTURE BEHV OF CNT8 IS

SIGNAL CQI : STD_LOGIC_VECTOR(2 DOWNTO 0);

BEGIN

PROCESS(CLK1)

BEGIN

IF (CLK1'EVENT AND CLK1='1') THEN

CQI<=CQI+1;

END IF;

QOUT<=CQI;

END PROCESS;

END ARCHITECTURE BEHV;

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY CNT16 IS

PORT( CLK : IN STD_LOGIC;

QOUT : OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

END ENTITY CNT16;

ARCHITECTURE BEHV OF CNT16 IS

SIGNAL CQI : STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

PROCESS(CLK)

BEGIN

IF (CLK'EVENT AND CLK='1') THEN

CQI<=CQI+1;

END IF;

QOUT<=CQI;

END PROCESS;

END ARCHITECTURE BEHV;

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY HANG IS

PORT(DATAIN : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

ROW : OUT STD_LOGIC_VECTOR(15 DOWNTO 0));

END ENTITY HANG;

ARCHITECTURE BEHV OF HANG IS

SIGNAL HANG : STD_LOGIC_VECTOR(15 DOWNTO 0);

BEGIN

PROCESS(DATAIN)

BEGIN

CASE DATAIN IS

WHEN "0000"=> ROW<="1000000000000000";

WHEN "0001"=> ROW<="0100000000000000";

WHEN "0010"=> ROW<="0010000000000000";

WHEN "0011"=> ROW<="0001000000000000";

WHEN "0100"=> ROW<="0000100000000000";

WHEN "0101"=> ROW<="0000010000000000";

WHEN "0110"=> ROW<="0000001000000000";

WHEN "0111"=> ROW<="0000000100000000";

WHEN "1000"=> ROW<="0000000010000000";

WHEN "1001"=> ROW<="0000000001000000";

WHEN "1010"=> ROW<="0000000000100000";

WHEN "1011"=> ROW<="0000000000010000";

WHEN "1100"=> ROW<="0000000000001000";

WHEN "1101"=> ROW<="0000000000000100";

WHEN "1110"=> ROW<="0000000000000010";

WHEN "1111"=> ROW<="0000000000000001";

WHEN OTHERS=> ROW<="0000000000000000";

END CASE;END PROCESS;

END ARCHITECTURE BEHV;

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY XIANSHI IS

PORT( WEI : IN STD_LOGIC_VECTOR(3 downto 0);

SHI : IN STD_LOGIC_VECTOR(2 downto 0);

Q : OUT STD_LOGIC_VECTOR(15 downto 0));

END XIANSHI;

ARCHITECTURE XIANSHI_architecture OF XIANSHI IS

BEGIN

process(shi,wei)

variable b:std_logic_vector(15 downto 0);

begin

case shi is

When "000"=>

case wei is

when "0000" =>b:="1111111111111111";

when "0001" =>b:="1011111111110111";

when "0010" =>b:="1101111111110000";

when "0011" =>b:="1110111011101110";

when "0100" =>b:="1111111101110110";

when "0101" =>b:="1000000001110000";

when "0110" =>b:="0010011111111001";

when "0111" =>b:="1110111101110110";

when "1000" =>b:="1111111101110000";

when "1001" =>b:="1111110000010110";

when "1010" =>b:="1111010111010110";

when "1011" =>b:="1110110111010110";

when "1100" =>b:="1101110000010110";

when "1101" =>b:="1011111111011110";

when "1110" =>b:="1011111111011110";

when "1111" =>b:="1111111111111111";

when others=>null; end case;

When "001"=>

case wei is

when "0000" =>b:="1111111111111111";

when "0001" =>b:="1111111110111111";

when "0010" =>b:="1111111101111111";

when "0011" =>b:="1110000000000111";

when "0100" =>b:="1111110111111111";

when "0101" =>b:="1111101111111111";

when "0110" =>b:="1111000000000111";

when "0111" =>b:="1111011011010111";

when "1000" =>b:="1111011010110111";

when "1001" =>b:="1111010000010111";

when "1010" =>b:="1111011101110111";

when "1011" =>b:="1111010000010111";

when "1100" =>b:="1111011101110111";

when "1101" =>b:="1111011101110111";

when "1110" =>b:="1111111111111111";

when "1111" =>b:="1111111111111111";

when others=>null; end case;

When "010"=>

case wei is

when "0000" =>b:="1111111111111111";

when "0001" =>b:="1111111111110111";

when "0010" =>b:="1000000000000011";

when "0011" =>b:="1111111011111111";

when "0100" =>b:="1111111011111111";

when "0101" =>b:="1111111011111111";

when "0110" =>b:="1111111011111111";

when "0111" =>b:="1111111011111111";

when "1000" =>b:="1111111011111111";

when "1001" =>b:="1111111011111111";

when "1010" =>b:="1111111011111111";

when "1011" =>b:="1111111011111111";

when "1100" =>b:="1111111011111011";

when "1101" =>b:="0000000000000001";

when "1110" =>b:="1111111111111111";

when "1111" =>b:="1111111111111111";

when others=>null; end case;

When "011"=>

case wei is

when "0000" =>b:="1111111111111111";

when "0001" =>b:="1111101111111111";

when "0010" =>b:="1111011111111111";

when "0011" =>b:="1110111100000111";

when "0100" =>b:="1000111101110111";

when "0101" =>b:="1110111101110111";

when "0110" =>b:="1110111100000111";

when "0111" =>b:="1000000111111111";

when "1000" =>b:="1110111000000011";

when "1001" =>b:="1100011111011111";

when "1010" =>b:="1010101000000011";

when "1011" =>b:="0110101111011111";

when "1100" =>b:="0110110111011111";

when "1101" =>b:="1110111000000011";

when "1110" =>b:="1110111111111111";

when "1111" =>b:="1111111111111111";

when others=>null; end case;

When "100"=>

case wei is

when "0000" =>b:="1101110111110111";

when "0001" =>b:="1110111011110111";

when "0010" =>b:="1111111111111111";

when "0011" =>b:="1111111111011111";

when "0100" =>b:="1000000000000001";

when "0101" =>b:="1011111111111101";

when "0110" =>b:="0111111111111011";

when "0111" =>b:="1110000000011111";

when "1000" =>b:="1111111110111111";

when "1001" =>b:="1111111001111011";

when "1010" =>b:="0000000000000001";

when "1011" =>b:="1111111011111111";

when "1100" =>b:="1111111011111111";

when "1101" =>b:="1111111011111111";

when "1110" =>b:="1111101011111111";

when "1111" =>b:="1111110111111111";

when others=>null; end case;

When "101"=>

case wei is

when "0000" =>b:="1111111111111111";

when "0001" =>b:="1111011110011111";

when "0010" =>b:="1110101111101111";

when "0011" =>b:="1101110100000001";

when "0100" =>b:="1101110011111110";

when "0101" =>b:="1100001011000110";

when "0110" =>b:="1101001111111111";

when "0111" =>b:="1101110100000001";

when "1000" =>b:="1100010111010111";

when "1001" =>b:="1101101111010111";

when "1010" =>b:="1101111111010111";

when "1011" =>b:="1101111110010111";

when "1100" =>b:="1101111110110101";

when "1101" =>b:="1101111101110000";

when "1110" =>b:="1111111111111111";

when "1111" =>b:="1111111111111111";

when others=>null; end case;

when others=>null;

end case;

q<=b;

end process;

END XIANSHI_architecture;

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY JUZHEN16 IS

PORT (a,b : IN STD_LOGIC ;

Q1,W1: OUT STD_LOGIC_VECTOR(15 DOWNTO 0));

END ENTITY JUZHEN16;

ARCHITECTURE JZ16 OF JUZHEN16 IS

COMPONENT CNT8

PORT( CLK1: IN STD_LOGIC;

QOUT : OUT STD_LOGIC_VECTOR(2 DOWNTO 0));

END COMPONENT;

COMPONENT CNT16

PORT( CLK : IN STD_LOGIC;

QOUT : OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

END COMPONENT;

COMPONENT HANG

PORT(DATAIN : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

ROW : OUT STD_LOGIC_VECTOR(15 DOWNTO 0));

END COMPONENT;

COMPONENT XIANSHI

PORT( WEI : IN STD_LOGIC_VECTOR(3 downto 0);

SHI : IN STD_LOGIC_VECTOR(2 downto 0);

Q : OUT STD_LOGIC_VECTOR(15 downto 0));

END COMPONENT;

SIGNAL c: STD_LOGIC_VECTOR(3 downto 0);

SIGNAL d: STD_LOGIC_VECTOR(2 downto 0);

BEGIN

U1: CNT8 PORT MAP( CLK1=>b,QOUT=>d );

U2: CNT16 PORT MAP( CLK=>a,QOUT=>c );

U3: HANG PORT MAP(datain=>c,ROW=>Q1);

U4: XIANSHI PORT MAP (wei=>c,shi=>d,Q=>W1);

END ARCHITECTURE JZ16;

七、评分表

课程设计评分表

课程名称: 16*16点阵设计

教师签名:

日 期:

-

课程设计实验报告

C程序设计课程设计说明题目名称学生成绩管理系统学生学号120xx3503037学生姓名张金宝指导老师张玉军马驰20xx年3月书目录…

-

课程设计实验报告-模板

成都理工大学课程设计实验报告课程名称程序设计院系信科院数字媒体技术系班级所属小组姓名学号指导教师何建军20xx年月日课程设计要求课…

-

软件课程设计实验报告个人报告

软件课程设计实验报告个人报告课班成员学一需求分析1引言32预期功能33设计目标4二界面方案设计说明1拟选用的开发平台和工具介绍42…

-

课程设计实验报告(史上最全面最详细)

信息科学与技术学院课班设计报告课程名称面向对象程序设计姓名XXXXXXXXXX级126班学号12263716指导教师钱苏斌XXXX…

-

课程设计实验报告

XXXXXXXX课程设计报告课题名称带式输送机传动装置设计学院机电工程系专业班级机械设计制造及其自动化学号学生指导老师XXXXXX…

-

EDA课程设计实验报告

大学课程设计报告设计名称3位数字频率设计姓名学号专业班级08级电子信息工程专业二班院系计算机与信息工程学院设计时间20xx年1月日…

-

EDA课程设计实验报告 电子电工实习

华北电力大学实验报告实验名称课程名称电子电工实习专业班级学生姓名号成绩指导教师实验日期20xx12学华北电力大学实验报告第页共页华…

-

EDA综合课程设计实验报告

EDA综合课程设计实验报告题目设计一个全双工院系学号姓名教师时间UART电路XXXXX20xx06021课程设计的摘要原理22设计…

-

EDA课程设计报告 数字钟(综合实验) 哈尔滨学院

EDA课程设计报告设计课题数字钟综合实验专业班级电子101学生姓名岳杨指导教师刘宏设计时间20xx62420xx75数字钟综合实验…

-

EDA课程设计实验报告模板

基于Protel99se的太阳能干燥机的设计一实验目的通过实验熟练掌握Protel99se软件的基本操作和应用能熟练使用Prote…

-

EDA秒表设计 实验报告

EDA课程设计报告基于VHDL语言的秒表设计课程名称EDA技术院系地球物理及信息工程学院专业班级电子信息工程08级2班学生姓名学号…