EDA秒表设计 实验报告

EDA课程设计报告

——基于VHDL语言的秒表设计

课程名称: EDA技术

院 系: 地球物理及信息工程学院

专业班级: 电子信息工程08级2班

学生姓名:

学 号:

指导老师:

完成时间: 2011年5月18日

秒表设计

一. 设计要求

利用EDA实验箱,通过VHDL语言进行编程,设计一个简单的秒表,并用EDA实验箱进行实现,具体设计要求如下:

(1)有使能、暂停、继续、秒表计数功能;

(2)带有异步复位功能;

(3)显示分、秒信息,若需要,显示秒表信息。

二. 设计的作用、目的

在本次设计中,可以简单的了解EDA技术的应用以及VHDL语言编写的方法。通过设计一个秒表,可以掌握用VHDL设计多位加法计数器的方法,尤其是调整时钟使得每过一秒就改变一个数,达到设计的要求。

三. 设计的具体实现

1.系统概述

本次系统设计主要分三个部分,一是通过VHDL语言设计一个八位的加法计数器,来实现秒表的计时功能;二是通过调整时钟使秒表计数为每秒改变一个数;三是加入一些控制按键,实现使能、暂停、继续等功能。

2.程序具体设计

秒表显示共有6位,两位显示分,两位显示秒,十分秒和百分秒各一位。设计时使用一个计数器,随着时钟上升沿的到来循环计数,每计数一次,百分秒位加一,通过百分秒位满十进位来控制十分位的计数,十分位满十进位,依次类推,实现秒表计数。

为实现秒位的计时精确,百秒位必须以0.01秒的时间间隔计数,即时钟的频率是100Hz。为此,本设计采用3MHz的时钟频率通过分频得到100Hz的时钟频率,再送给控制时钟以得到比较精确的CLK信号。具体程序设计见附录。

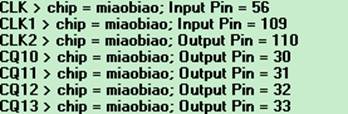

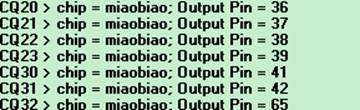

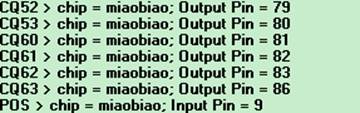

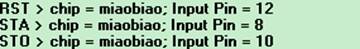

引脚定义如下:

其中,时钟信号CLK为3MHz的时钟频率,分频后得到的时钟为CLK2,输出引脚CLK2和输入引脚CLK2在外部相连,实现将分频后的时钟送入。

3.调试

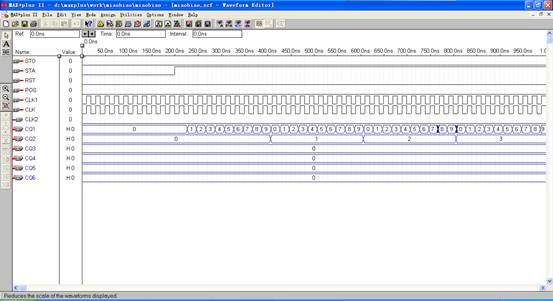

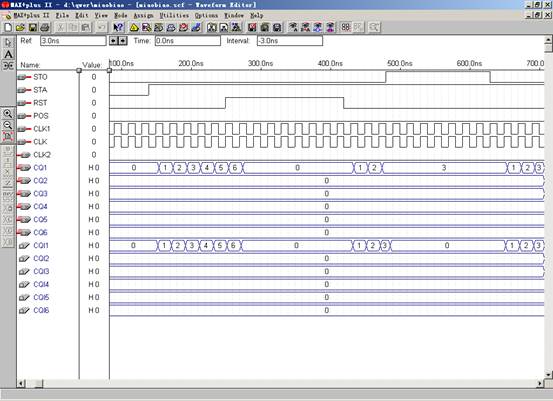

应用MAX+plus II软件编译调试实验控制程序, 仿真运行结果如下:

(1)给时钟后,实现开始功能:

开始键按下(STA=‘1’)后,秒表计数开始。

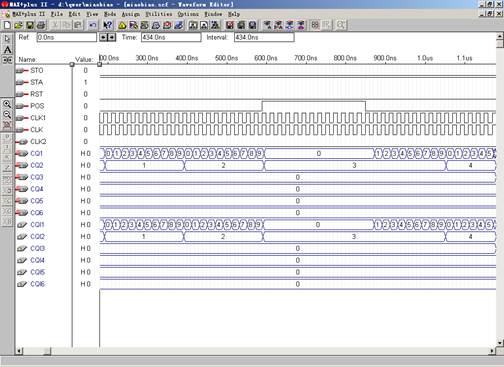

(2)给时钟后,实现暂停功能:

从上图可以看出暂停键按下后(POS=‘1’),输出(CQ)保持不变,直到暂停键再次按下(POS=‘0’),输出才继续计数,从而实现了暂停的功能。

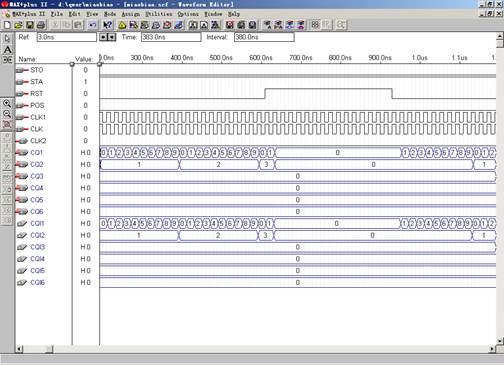

(3)给时钟后,实现复位功能:

从上图可以看出复位键按下后(RST=‘1’),输出(CQ)全部变为复位状态(0),直到复位键再次按下(RST=‘0’),输出才继续计数,从而实现了复位的功能。

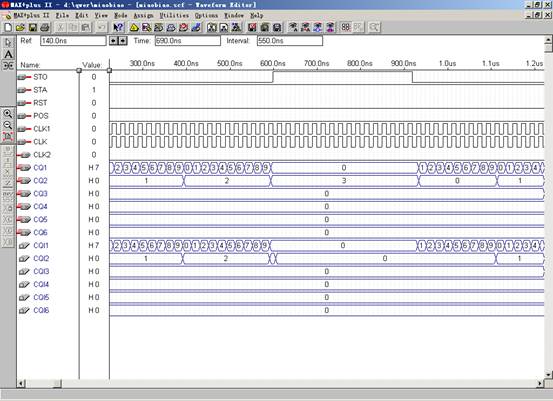

(4)给时钟后,实现停止的功能:

从上图可以看出停止键按下后(STO=‘1’),输出(CQ)全部保持当前状态不变,直到停止键再次按下(STO=‘0’),输出才从全零状态继续计数,从而实现了停止的功能。

(5)综合功能的实现:

4.系统调试中出现的问题

在初次系统调试的过程中,由于实验箱上并没有时钟满足运行时是一秒计一个数,所以无法实现秒表的功能。后来通过在程序中加入一个时钟分频的进程,利用实验箱上现有的时钟再得到一个新的时钟,实现了秒表的计时功能。

四.心得体会

通过本次EDA的实验,进一步了解了VHDL语言的特点,了解了硬件描述语言的编程思想、编程规范,在一定程度上提高了实际编程能力。

附录

运行程序如下:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY MIAOBIAO IS

PORT (CLK,CLK1,STA,POS,STO,RST: IN STD_LOGIC;

CQ1,CQ2,CQ3,CQ4,CQ5,CQ6 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

CLK2:OUT STD_LOGIC

);

END MIAOBIAO;

ARCHITECTURE BEHAV OF MIAOBIAO IS

BEGIN

PROCESS(CLK) --由频率为3MHz的时钟产生频率为100Hz的时钟

VARIABLE NUM:INTEGER RANGE 0 TO 15000;--定义计数器

VARIABLE Q:STD_LOGIC;

BEGIN

IF CLK'EVENT AND CLK='1' THEN

IF NUM=15000 THEN NUM:=0;Q:=NOT Q;--计数器每计数15000,时钟改变电平--值

ELSE NUM:=NUM+1;

END IF;

END IF;

CLK2<=Q;

END PROCESS;

PROCESS(CLK1,STA,POS,STO,RST)

VARIABLE CQI1:STD_LOGIC_VECTOR(3 DOWNTO 0);

VARIABLE CQI2:STD_LOGIC_VECTOR(3 DOWNTO 0);

VARIABLE CQI3:STD_LOGIC_VECTOR(3 DOWNTO 0);

VARIABLE CQI4:STD_LOGIC_VECTOR(3 DOWNTO 0);

VARIABLE CQI5:STD_LOGIC_VECTOR(3 DOWNTO 0);

VARIABLE CQI6:STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

IF STO='1' THEN CQI1:=(OTHERS=>'0');CQI2:=(OTHERS=>'0');CQI3:=(OTHERS=>'0');

CQI4:=(OTHERS=>'0');CQI5:=(OTHERS=>'0');CQI6:=(OTHERS=>'0');

ELSIF CLK1'EVENT AND CLK1='1' THEN

IF STA='1' THEN

IF RST='0' THEN

IF POS='0' THEN

IF CQI1="1001" THEN CQI1:=(OTHERS => '0');--百分秒位满十进--位

IF CQI2="1001" THEN CQI2:=(OTHERS => '0'); --十分秒位满十进--位

IF CQI3="1001" THEN CQI3:=(OTHERS => '0'); --秒位满十进位

IF CQI4="0101" THEN CQI4:=(OTHERS => '0'); --十秒位满六进位

IF CQI5="1001" THEN CQI5:=(OTHERS => '0'); --分位满十进位

IF CQI6="0101" THEN CQI6:=(OTHERS => '0'); --十分位满六进位

ELSE CQI6:=CQI6+1;

END IF;

ELSE CQI5:=CQI5+1;

END IF;

ELSE CQI4:=CQI4+1;

END IF;

ELSE CQI3:=CQI3+1;

END IF;

ELSE CQI2:=CQI2+1;

END IF;

ELSE CQI1:=CQI1+1;

END IF;

END IF;

END IF;

END IF;

IF RST='1' THEN

CQI1:=(OTHERS => '0');CQI2:=(OTHERS => '0');

CQI3:=(OTHERS => '0');CQI4:=(OTHERS => '0');

CQI5:=(OTHERS => '0');CQI6:=(OTHERS => '0');

END IF;

CQ1<=CQI1;CQ2<=CQI2;CQ3<=CQI3;

CQ4<=CQI4;CQ5<=CQI5;CQ6<=CQI6;

END IF;

END PROCESS;

END BEHAV;

第二篇:EDA课程设计数字秒表设计

北 华 航 天 工 业 学 院

《EDA技术综合设计》

课程设计报告

报告题目 : 数字秒表设计

作者所在系部: 电子工程系

作者所在专业: 自动化

作者所在班级: B08221

作 者 姓 名 : 李龙

指导教师姓名: 崔瑞雪

完 成 时 间 : 2010/12/3

内 容 摘 要

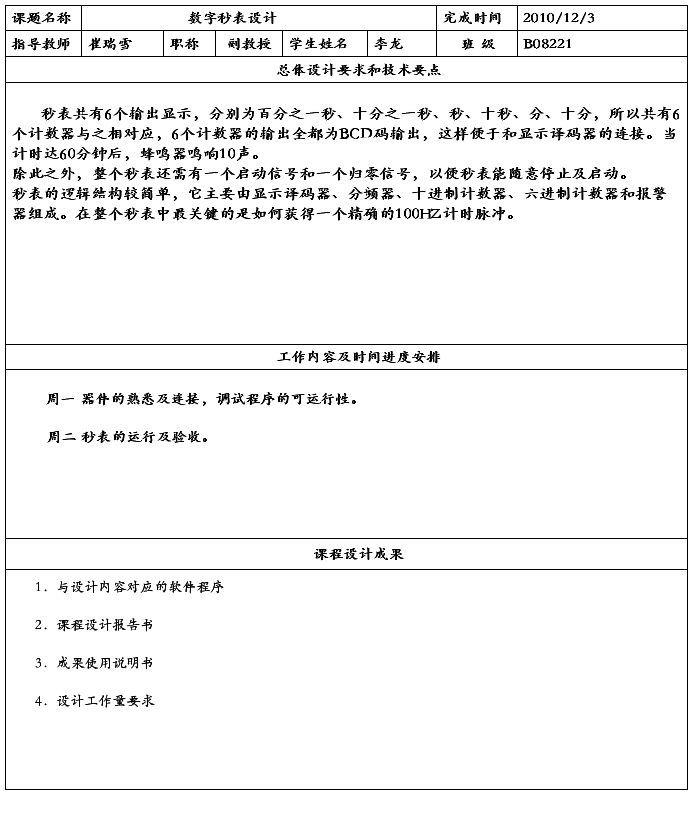

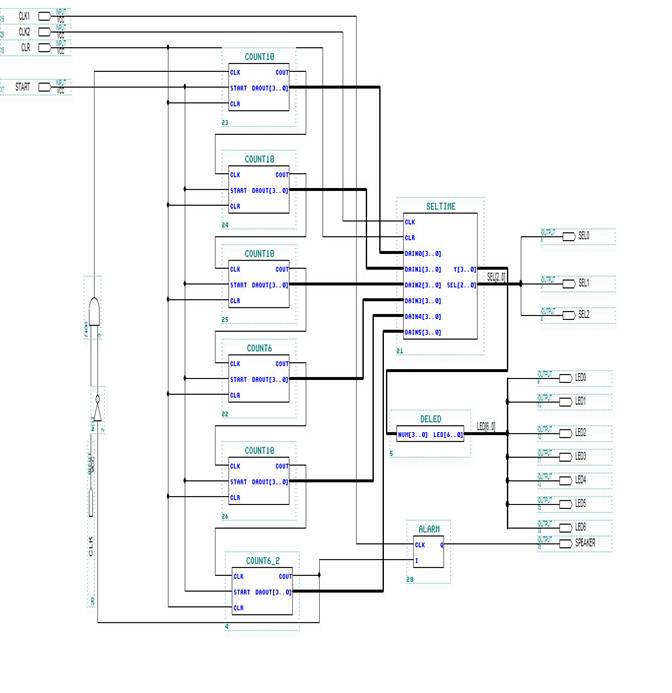

秒表共有6个输出显示,分别为百分之一秒、十分之一秒、秒、十秒、分、十分,所以共有6个计数器与之相对应,6个计数器的输出全都为BCD码输出,这样便于和显示译码器的连接。当计时达60分钟后,蜂鸣器鸣响10声。

除此之外,整个秒表还需有一个启动信号和一个归零信号,以便秒表能随意停止及启动。

秒表的逻辑结构较简单,它主要由显示译码器、分频器、十进制计数器、六进制计数器和报警器组成。

四个10进制计数器:用来分别对百分之一秒、十分之一秒、秒和分进行计数;

两个6进制计数器:用来分别对十秒和十分进行计数;

分频器:用来产生100HZ计时脉冲;

显示译码器:完成对显示的控制。

根据电路持点,用层次设计概念将此设计任务分成若干模块,规定每一模块的功能和各模块之间的接口。

。

按适配划分后的管脚定位,同相关功能块硬件电路接口连线。

用VHDL语言描述所有底层模块。

清零信号为异步清零。

当最高位记到6时 停止计数 显示译码器全部显示零,并发出十声警报声。按下复位按钮后继续计数。

关键词:秒表、计数器、蜂鸣器、显示器

目 录

十进制计数器?????????????????????????????????????????????????????5

六进制计数器?????????????????????????????????????????????????????6

选择数码管????????????????????????????????????????????????????????8

显示数码管????????????????????????????????????????????????????????9

响铃装置????????????????????????????????????????????????????????????10

总设计电路图?????????????????????????????????????????????????????11

实验总结????????????????????????????????????????????????????????????12

参考文献????????????????????????????????????????????????????????????12

课程设计任务书

十进制计数器模块

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

entity count10 is

port(

clr,start,clk:in std_logic;

cout:out std_logic;

daout:buffer std_logic_vector(3 downto 0));

end count10;

architecture behave of count10 is

begin

process(clr,start,clk)

begin

if clr='1' then daout<="0000";

elsif ( clk'event and clk='1') then

if start='1' then

if daout="1001" then daout<="0000";cout<='1';

else daout<=daout+1;cout<='0';

end if;

end if;

end if;

end process;

end behave;

六进制计数器模块

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

entity count6 is

port(

clr,start,clk:in std_logic;

cout:out std_logic;

daout:buffer std_logic_vector(3 downto 0));

end count6;

architecture behave of count6 is

begin

process(clr,start,clk)

begin

if clr='1' then daout<="0000";

elsif ( clk'event and clk='1') then

if start='1' then

if daout="0101" then daout<="0000";cout<='1';

else daout<=daout+1;cout<='0';

end if;

end if;

end if;

end process;

end behave;

六进制计数器模块(当最高位为六时清零)

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity count6_2 is

port (clk,start,clr : in std_logic;

cout : out std_logic;

daout: out std_logic_vector(3 downto 0));

end count6_2;

architecture two of count6_2 is

signal q0 : std_logic_vector(3 downto 0);

signal q1 : std_logic;

begin

process(clk,clr)

begin

if clr='1' then q0<="0000";q1<='0';

elsif clk'event and clk='1' then

if start='1' then

if q0="0101" then

q0<="0000";

q1<='1';

else q0<=q0+1;

q1<='0';

end if;

end if;

end if;

end process;

daout<=q0;

cout<=q1;

end;

选择模块

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

entity seltime is

port(

clr,clk:in std_logic;

dain1:in std_logic_vector(3 downto 0);

dain2:in std_logic_vector(3 downto 0);

dain3:in std_logic_vector(3 downto 0);

dain4:in std_logic_vector(3 downto 0);

dain5:in std_logic_vector(3 downto 0);

dain6:in std_logic_vector(3 downto 0);

sel:out std_logic_vector(2 downto 0);

daout:out std_logic_vector(3 downto 0));

end seltime;

architecture behave of seltime is

signal count: std_logic_vector(2 downto 0);

begin

sel<=count;

process(clr,clk)

begin

if clr='1' then

count<="000";

elsif( clk'event and clk='1') then

if count="110" then count<="000";

else count<=count+1;

end if;

end if;

case count is

when"001"=>daout<=dain1;

when"010"=>daout<=dain2;

when"011"=>daout<=dain3;

when"100"=>daout<=dain4;

when"101"=>daout<=dain5;

when"110"=>daout<=dain6;

when others=>null;

end case;

end process;

end behave;

数码管显示模块

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

entity deled is

port(

num:in std_logic_vector(3 downto 0);

led:out std_logic_vector(6 downto 0));

end deled;

architecture behave of deled is

begin

process(num)

--abcdefg

begin

case num is

when"0000"=>led<="1111110";

when"0001"=>led<="0110000";

when"0010"=>led<="1101101";

when"0011"=>led<="1111001";

when"0100"=>led<="0110011";

when"0101"=>led<="1011011";

when"0110"=>led<="1011111";

when"0111"=>led<="1110000";

when"1000"=>led<="1111111";

when"1001"=>led<="1111101";

when others=>null;

end case;

end process;

end behave;

Alarm模块

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

entity alarm is

port(

clk,i:in std_logic;

q:out std_logic);

end alarm;

architecture behave of alarm is

signal count:integer range 0 to 20;

signal q0:std_logic;

begin

process(clk,i)

begin

if ( clk'event and clk='1') then

if i='0' then count<=0;q0<='0';

elsif i='1' then

if count<=19 then count<=count+1;q0<=not q0;

end if;

end if;

end if;

end process;

q <=q0;

end behave;

实验总结

这次课程设计历时两天,通过这次的学习,发现了自己的很多不足(你的不足之一就是欠认真,请重写报告,其他不足我还未发现,若有,自己偷着改吧),自己知识的很多漏洞,看到了自己的实践经验还是比较缺乏,理论联系实际的能力还需要提高。

通过这次学习,我不仅学会了使用Max+plusⅡ软件进行仿真,进一步学会了EDA的理论知识。

这次课程设计让我理解到理论与实际结合的重要性,尤其是在我们现在所学习的领域中,更是要不断的实践,只有通过不断的实践,来强化自己的动手能力,理论与实际相结合,才能使自己在日益激烈的竞争中胜出。

在这次课程设计中,刚开始的时候我们设计的程序没错,但是连接到实际中,却发现秒表不能正常运行,通过不断的修改才能正常的运行,这说明了理论只有在实践中才能更好的见证错与对。

参考文献

李国洪、沈明山 主编 胡辉 副主编

《可编程器件 EDA技术与实践》

-

程序设计实验报告模板

C语言程序设计实验报告1实验目的(1)掌握函数的定义方法、调用方法、参数说明以及返回值;(2)掌握实参与形参的对应关系,以及参数之…

-

教案设计实验报告

课文7布置作业2选择媒体的依据是什么答一般使用PPT因为它是个集合多媒体展示功能的黑板学生不仅可以直接看到很多关于课文内容的图片介…

-

数据库设计实验报告

HEFEIUNIVERSITY数据库设计报告题目产品销售系统系别电子信息与电气工程系班级09级电气信息类5班学号090507503…

-

PCB设计实验报告

Protel99SE原理图与PCB设计的实验报告摘要:Protel99SE是一种基于Windows环境下的电路板设计软件。该软件功…

-

Web网页设计实验报告

WEB系统开发综合实验报告题目红尘客栈网上订房页面专业计算机科学与技术信息技术及应用班级学生重庆交通大学20xx年目录一设计目的3…

-

EDA课程设计实验报告

课程设计报告课程名称数字系统与逻辑设计课题名称16*16点阵显示专业通信工程班级1181学号姓名指导教师20##年7月2日《数字系…

-

EDA课程设计实验报告

大学课程设计报告设计名称3位数字频率设计姓名学号专业班级08级电子信息工程专业二班院系计算机与信息工程学院设计时间20xx年1月日…

-

EDA课程设计实验报告 电子电工实习

华北电力大学实验报告实验名称课程名称电子电工实习专业班级学生姓名号成绩指导教师实验日期20xx12学华北电力大学实验报告第页共页华…

-

EDA综合课程设计实验报告

EDA综合课程设计实验报告题目设计一个全双工院系学号姓名教师时间UART电路XXXXX20xx06021课程设计的摘要原理22设计…

-

EDA课程实验设计报告

EDA课程实验设计报告洗衣机自动控制器设计一实验要求1由一个按键控制洗衣机的启动暂停2洗衣机洗涤一定时间后能自动停止由一个LED灯…