EDA课程设计

EDA8路彩灯控制系统VHDL

程序设计

院系:@@院

专业: 0802班

学号:############

姓名:@@@

一、设计要求

1、设计一个七段数码管动态扫描电路。数码管个数为8个,共阴极接法。

2、设计一电路,控制上述电路实现“12345678”八个数字的显示,要求显示方式为:

(1)自左至右逐个点亮数码管,最后全亮;再重复以上动作。

(2)自左至右点亮数码管,每次只点亮一个,最后全息灭,再重复以上动作。

(3) 先中间两个点亮,再依次向外点亮;全亮后,再依次向中间熄灭;重复上述步骤。

二、设计方案()

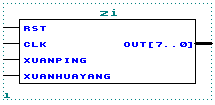

整个系统共有三个输入信号:控制彩灯节奏快慢的基准时钟信号CLK,彩灯变化频率选择开关xuanping,彩灯花样选择开关xuanhuayang;共有8个输出信号out[7..0],分别用于控制八路彩灯。系统整体框图如下:

主要模块组成:时序控制电路模块和显示电路模块。时序控制电路模块由分频和选频两部分构成,可以控制彩灯变化的快慢。

三,设计过程

1、主程序:8路彩灯

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

ENTITY color8 IS

PORT (clk,rst:IN std_LOGIC;

sel:in std_LOGIC_VECTOR(1 DOWNTO 0);

aout:OUT std_LOGIC_VECTOR(7 DOWNTO 0));

END color8;

ARCHITECTURE color OF color8 IS

TYPE state_1 IS (s0,s1,s2,s3,s4,s5,s6,s7,s8);

SIGNAL state_2:state_1;

BEGIN

pr_1:PROCESS (clk,rst)

BEGIN

IF rst='1' THEN state_2<=s0;

ELSIF clk'event AND clk='1' THEN

CASE state_2 IS

WHEN s0=> state_2<=s1;

WHEN s1=> state_2<=s2;

WHEN s2=> state_2<=s3;

WHEN s3=> state_2<=s4;

WHEN s4=> state_2<=s5;

WHEN s5=> state_2<=s6;

WHEN s6=> state_2<=s7;

WHEN s7=> state_2<=s8;

WHEN s8=> state_2<=s0;

END CASE;

END IF;

END PROCESS pr_1;

pr_2:PROCESS(sel,state_2)

BEGIN

if sel="00" then

--when "00" =>

CASE state_2 IS

WHEN s0=> aout<="00000000";

WHEN s1=> aout<="10000000";

WHEN s2=> aout<="11000000";

WHEN s3=> aout<="11100000";

WHEN s4=> aout<="11110000";

WHEN s5=> aout<="11111000";

WHEN s6=> aout<="11111100";

WHEN s7=> aout<="11111110";

WHEN s8=> aout<="11111111";

END CASE;

elsif sel="01" then

CASE state_2 IS

WHEN s0=> aout<="00000000";

WHEN s1=> aout<="10000000";

WHEN s2=> aout<="01000000";

WHEN s3=> aout<="00100000";

WHEN s4=> aout<="00010000";

WHEN s5=> aout<="00001000";

WHEN s6=> aout<="00000100";

WHEN s7=> aout<="00000010";

WHEN s8=> aout<="00000001";

END CASE;

--when "10"=>

elsif sel="10" then

CASE state_2 IS

WHEN s0=> aout<="00000000";

WHEN s1=> aout<="00011000";

WHEN s2=> aout<="00111100";

WHEN s3=> aout<="01111110";

WHEN s4=> aout<="11111111";

WHEN s5=> aout<="01111110";

WHEN s6=> aout<="00111100";

WHEN s7=> aout<="00011000";

WHEN s8=> aout<="00000000";

END CASE;

end if;

END PROCESS pr_2;

END color8;

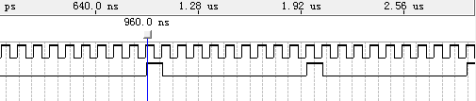

仿真结果如下图:

(1)当sel为“00”时, 8路彩灯被选中运行方式一,即自左至右逐个点亮数码管,最后全亮;再重复以上动作。此时波形图如下:

注:由于rst高电平时是复位,所以仿真时便将它一直设为低电平。

(2)当sel为“01”时, 8路彩灯被选中运行方式二,即自左至右点亮数码管,每次只点亮一个,最后全息灭,再重复以上动作。此时波形图如下:

(3)当sel为“10”时, 8路彩灯被选中运行方式三,即先中间两个点亮,再依次向外点亮;全亮后,再依次向中间熄灭;重复上述步骤。此时波形图如下:

注:由于之前都有9个状态,这个彩灯的花样只需要8个状态即可,但为了与主控时序进程中的状态转换设计相符合,我将最后一个状态变为全零即与第一个状态相同。所以在此仿真中有连续两个clk上升沿出现全零的状况。

2、同步时钟CLK频率计算

CLK频率计算:

根据人的视觉暂留现象,一个数码管所要显示的字符只要在一秒内点亮24次以上,则感觉上该数码管没有熄灭一样。若8只数码管要出现这种效果,要求在一秒内每只数码管要闪亮24次以上。则CLK频率应为24X8=192Hz以上,为了减少闪烁现象,达到较好的显示效果,取CLK频率为1024Hz,每秒内每个数码管显示次数为128次。

分频器程序

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE ieee.std_logic_unsigned.all;

ENTITY fenpin IS

PORT(CLK : IN STD_LOGIC;

CLK1 : OUT STD_LOGIC;

CLK2 : OUT STD_LOGIC);

END fenpin ;

ARCHITECTURE a OF fenpin IS

SIGNAL cou : STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

PROCESS(clk)

BEGIN

IF clk'event and clk='1' THEN

cou <= cou+1;

END IF;

END PROCESS;

CLK1 <= cou(2);

CLK2 <= cou(1);

END a;

仿真波形:

3、频率选择模块(选择不同的模块实现快慢不同节奏)

library ieee;

use ieee.std_logic_1164.all;

entity xuanzepl is

port(clk1,clk2,s: in std_logic;

CLKOUT: out std_logic);

end xuanzepl;

architecture a of xuanzepl is

signal sel: std_logic;

begin

process(clk1,clk2,S)

begin

if s='0' then

CLKOUT<=clk1;

else

CLKOUT<=clk2;

end if;

sel<=s;

end process;

end a;

仿真结果如下:

结果分析:当S为高电平时,clkout选择CLK2,当S为低电平时,选择CLK1。

4、彩灯运行方式的选择:

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE ieee.std_logic_unsigned.all;

ENTITY y IS

PORT( clk: IN STD_LOGIC;

S: OUT std_logic_vector(1 downto 0));

END y;

ARCHITECTURE a OF y IS

Signal ja :std_logic_vector(1 downto 0);

BEGIN

PROCESS(clk)

BEGIN

IF CLK'event AND CLK='1' THEN

IF ja="10" THEN ja<="00";

else ja<=ja+1;

END IF;

END IF;

Case ja is

when "00"=>s<="00";

when "01"=>s<="01";

when "10"=>s<="10";

when others=>null;

end case;

END PROCESS ;

END a;

结果分析:此时这的CLK相当于一个切换键,是为了切换彩灯的运行方式。起初S为“00”此时选择方式1;当clk来了一个上升沿时,S变为“01”此时选择方式二;当clk再来一个上升沿时,S变为“10”此时选择方式三。然后将S引脚与主程序模块color8的sel脚相接。所以我们可以通过clk键在这三种方式中选择彩灯的花样。

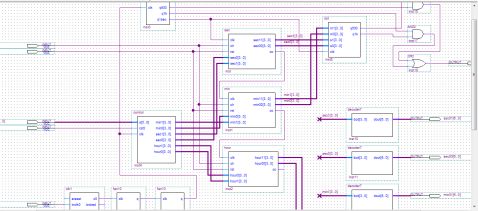

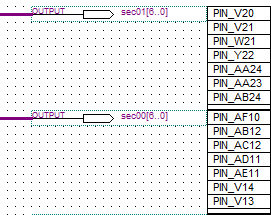

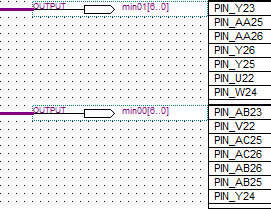

5、总的原理图:

仿真结果:

当xuanhuayang取不同的值时,out输出的花样也随之变化。同时,xuanping为通过输入高低电平来控制out的变化频率。

四、总结

在此次课程设计中,我们要有一个大致的整体框图,然后分别实现各个模块,以达到设计要求。在设计过程中,尤其是在编程的时候,出现了许多错误,经过一步步改正,向同学请教等,终于得以成功,这次实验主要考察了我们的VHDL语言的掌握能力,以及将其运用到我们的生活中去,具有很好的实用价值,也加强了我们对EDA的掌握能力。

第二篇:EDA课程设计——数字钟

EDA设计报告 题 目:

姓 名:学 院:专 业:班 级:学 号:指导教师: 数字钟

20xx年6月7日

目录

一. 数字钟的设计目的

二. 数字钟设计的内容

三. 数字钟程序设计的思路

四. 数字钟设计的整体框图

五. 数字钟的下载和硬件测试

六. 心得体会

第一章 数字钟的设计目的

1.学习数字钟的设计方法

2.学习较复杂的的数字系统的设计方法

第二章 数字钟设计的内容

数字钟是数字电路中的一个典型应用,本设计实现数字钟的一些基本功能,能进行正常的时.分.秒计时功能,能实现整点报时功能,当计时达到59分52秒时开始报时,在59分52秒,59分,54秒,59分56秒,59分58秒时鸣叫,鸣叫的频率为500HZ,在到达59分60秒时最后一声整点报时,频率为1HZ。其外部接口及总体设计框图如图,包含control.sec.main.hour.sst五大模块。其中时间计数电路由秒个位和秒十位计数器,分个位和分十位计数器及时个位和时十位计数器电路构成,其中秒个位和秒十位计数器、分个位和分十位计数器为60进制计数器,而根据设计要求,时个位和时十位计数器为24进制计数器

第三章 数字中设计的思路

1.control模块:实现修改时间功能,其子模块con1功能为采集修改数值。 control控制模块的VHDL源代码如下:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY control IS

PORT( s:IN STD_LOGIC_VECTOR(5 DOWNTO 0);

rst0,clk:IN STD_LOGIC;

min1,min0:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

sec1,sec0:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

hour1,hour0:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

END;

ARCHITECTURE one OF control IS

SIGNAL min11,min00,sec11,sec00,hour11,hour00:STD_LOGIC_VECTOR(3 DOWNTO 0);

COMPONENT con1 IS

PORT(s,rst:IN STD_LOGIC;

q:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

END COMPONENT con1;

BEGIN

u0:con1 PORT MAP(s=>s(0),rst=>rst0,q=>sec00);

u1:con1 PORT MAP(s=>s(1),rst=>rst0,q=>sec11);

u2:con1 PORT MAP(s=>s(2),rst=>rst0,q=>min00);

u3:con1 PORT MAP(s=>s(3),rst=>rst0,q=>min11);

u4:con1 PORT MAP(s=>s(4),rst=>rst0,q=>hour00);

u5:con1 PORT MAP(s=>s(5),rst=>rst0,q=>hour11);

PROCESS(clk)

BEGIN

IF clk'EVENT AND clk='1' THEN

sec1<=sec11; sec0<=sec00;

min1<=min11; min0<=min00;

hour1<=hour11; hour0<=hour00;

END IF;

END PROCESS;

END;

2.con1 模块:实现对按键数的统计,按键一次,计数器加1,如果大于9时,自动清零。

con1模块的VHDL源代码如下

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY con1 IS

PORT(s,rst:IN STD_LOGIC;

q:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

END;

ARCHITECTURE one OF con1 IS

SIGNAL q1:STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

PROCESS(s,rst)

BEGIN

IF rst='1' THEN q1<="0000";

ELSIF s'EVENT AND s='1' THEN

IF q1<"1001" THEN

q1<=q1+1;

ELSE

q1<="0000";

END IF;

END IF;

END process;

q<=q1;

END;

3.sst模块:为整点报时提供控制信号,当58min,秒为52,54,56,58时,q500输出为“1”,秒为00时,q1k输出“1”,这两个信号经过逻辑门实现报时功能。 sst 模块的VHDL源代码如下

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY sst IS

PORT(m1,m0,s1,s0:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

clk:IN STD_LOGIC;

q500,q1k:OUT STD_LOGIC);

END;

ARCHITECTURE one OF sst IS

BEGIN

PROCESS(clk)

BEGIN

IF clk'EVENT AND clk='1' THEN

IF m1="0101" AND m0="1001" AND s1="0101" THEN

IF s0="0001" or s0="0011" or s0="0101" or s0="0111" THEN q500<='1';

ELSE

q500<='0';

END IF;

END IF;

IF m1="0101" AND m0="1001" AND s1="0101" AND s0="1001" THEN q1k<='1';

ELSE

q1k<='0';

END IF;

END IF;

END PROCESS;

END;

4. ccc模块:对系统时钟clk输入时4MHz频率进行分频,产生频率分别为1000HZ,500HZ和1HZ的时钟信号。

ccc模块的VHDL源代码如下

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY ccc IS

PORT( clk:IN STD_LOGIC;

q500,q1k,q1sec:OUT STD_LOGIC);

END;

ARCHITECTURE one OF ccc IS

SIGNAL x,y,z:STD_LOGIC;

BEGIN

PROCESS(clk)

VARIABLE cnt:INTEGER RANGE 0 TO 1999;

BEGIN

IF clk'EVENT AND clk='1' THEN

IF cnt<1999 THEN

cnt:=cnt+1;

ELSE

cnt:=0;

x<=NOT x;

END IF;

END IF;

END PROCESS;

q1k<=x;

PROCESS(x)

BEGIN

IF x'EVENT AND x='1' THEN

y<=not y;

END IF;

END PROCESS;

q500<=y;

PROCESS(y)

VARIABLE cnt:INTEGER RANGE 0 TO 499;

BEGIN

IF y'EVENT AND y='1' THEN

IF cnt<499 THEN

cnt:=cnt+1;

ELSE

cnt:=0;

z<=NOT z;

END IF;

END IF;

END PROCESS;

q1sec<=z;

END;

5.hour模块 源代码如下

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity hour is

Port ( clk ,clr: in std_logic;

rst : in std_logic;

hour0,hour1:in std_logic_vector(3 downto 0); hour11 : buffer std_logic_vector(3 downto 0);

hour00 : buffer std_logic_vector(3 downto 0); co : out std_logic);

end hour;

architecture behav of hour is

signal cnt1,cnt0:std_logic_vector(3 downto 0); begin

process(clk,clr)

begin

if clr='1'then cnt1<="0000";

cnt0<="0000";

elsif rst='1' then cnt1<=hour1;

cnt0<=hour0;

elsif clk'event and clk='1'then

if cnt1="0010" and cnt0="0100"then co<='1';

cnt1<="0000";

cnt0<="0000";

elsif cnt0<"1001"then cnt0<=cnt0+1;

co<='0';

else cnt0<="0000";

if cnt1<"0010"then cnt1<=cnt1+1; co<='0';

end if;

end if ;

end if ;

end process;

hour11<=cnt1;

hour00<=cnt0;

end behav;

6.min模块源代码如下

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity min is

Port ( clk ,clr: in std_logic;

rst : in std_logic;

min0,min1:in std_logic_vector(3 downto 0); min11 : buffer std_logic_vector(3 downto 0); min00 : buffer std_logic_vector(3 downto 0); co : out std_logic);

end min;

architecture behav of min is

signal cnt1,cnt0:std_logic_vector(3 downto 0); begin

process(clk,clr)

begin

if clr='1'then cnt1<="0000";

cnt0<="0000";

elsif rst='1' then cnt1<=min1;

cnt0<=min0;

elsif clk'event and clk='1'then

if cnt1="0110" and cnt0="1001"then co<='1';

cnt1<="0000";

cnt0<="0000";

elsif cnt0<"0110"then cnt0<=cnt0+1;

co<='0';

else cnt0<="0000";

if cnt1<"1001"then cnt1<=cnt1+1; co<='0';

end if;

end if ;

end if ;

end process;

min11<=cnt1;

min00<=cnt0;

end behav;

7.sec模块源代码如下

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity sec is

Port ( clk ,clr: in std_logic;

rst : in std_logic;

sec0,sec1:in std_logic_vector(3 downto 0); sec11 : buffer std_logic_vector(3 downto 0); sec00 : buffer std_logic_vector(3 downto 0); co : out std_logic);

end sec;

architecture behav of sec is

signal cnt1,cnt0:std_logic_vector(3 downto 0); begin

process(clk,clr)

begin

if clr='1'then cnt1<="0000";

cnt0<="0000";

elsif rst='1' then cnt1<=sec1;

cnt0<=sec0;

elsif clk'event and clk='1'then

if cnt1="0110" and cnt0="1001"then co<='1';

cnt1<="0000";

cnt0<="0000";

elsif cnt0<"0110"then cnt0<=cnt0+1;

co<='0';

else cnt0<="0000";

if cnt1<"1001"then cnt1<=cnt1+1; co<='0'; end if;

end if ;

end if ;

end process;

sec11<=cnt1;

sec00<=cnt0;

end behav;

8.10分频的VHDL语言

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY fen10 IS

PORT(clk:IN STD_LOGIC;

q:OUT STD_LOGIC);

END fen10;

ARCHITECTURE behav OF fen10 IS

BEGIN

PROCESS(clk)

VARIABLE cnt:INTEGER RANGE 0 TO 9;

BEGIN

IF clk'EVENT AND clk='1' THEN

IF cnt<9 THEN

cnt:=cnt+1;

q<='0';

ELSE cnt:=0;

q<='1';

END IF;

END IF;

END PROCESS;

END behav;

Fen10的仿真波形图

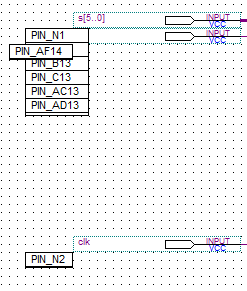

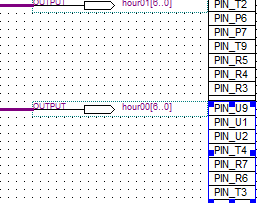

总的原理图:

端口说明

S[5..0]信号对应6个控制键,分别对应秒个位,秒十位,分个位,分十位,小时个位,小时十位。

rst信号为复位信号 ,在系统初始化时使用, clk 为时钟, clr为清零信号.

sound 信号连接扬声器,产生鸣叫。

sec1 [6..0]表示秒十位 sec0[6..0]表示秒个位

min1[6..0]表示分十位 min0[6..0]表示分个位

hour1[6..0]表示时十位 hour0[6..0]表示时个位

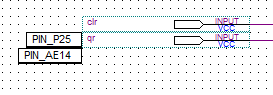

引脚的锁定

完成上述各部件全程编译然后封装,然后设计总图对总图进行编译,通过后锁 引脚以AS模式下载到开发板上。

第五章 数字钟的下载和硬件说明

将DE0开发板按要求接入电脑,清零信号开关为高电平时清零;当清零信号为低电平时,复位信号为高电平时时通过开光引脚调试时分秒,且数字钟从秒开始计时。

第六章 心得体会

看着开发板上的的数值开始计数,真的很开心,数字钟的每一个模块,如同自己走过来的每一步脚印,渗透着艰难与喜悦。数字钟是由三个计数器模块对时、分、秒进行计数,加上控制模块对其调整时钟的数字值组成的。在设计24进制计数器时,由于复位与清零没有进行合理的设置,导致编译始终通不过,后来在老师的耐心指导下,对VHDL的一遍遍修改,一次次的编译与仿真,终于完成了对数字钟的计数。在完成实验的过程中,虽然遇到了很多困难,但这次设计了锻炼了我们面对困难时的勇气与坚韧的毅力,它告诉我们遇到困难时不应该退缩,应该努力面对,并冷静下来分析困难的症结所在。通过这次设计让不仅让我们对EDA的应用有了进一步的了解,对而且让我了解到团队合作的力量。这次设计对我们而言,不仅仅是一次考试,而是给予了我们一种克服困难和解决困难的信念,相信以后我们以后面对困难时不再不知所措。

参考文献

1.《EDA技术与实践教程》 宋烈武 编著

-

工程预算课程设计总结

课程设计是培养学生综合运用所学知识,发现,提出,分析和解决实际问题,锻炼实践能力的重要环节,是对学生实际工作能力的具体训练和考察过…

-

c++课程设计总结

课程设计总结经过一个学期对《C++程序设计》的学习,我学习到了基本的理论知识,了解到了C++语言程序设计的思想,这些知识都为我的课…

-

化工原理课程设计总结

《化工原理课程设计》总结本学期顺利完成了化学工程与工艺专业共100名同学的化工原理课程设计,总体来看学生的工艺计算、过程设计及绘图…

-

PLC自动门课程设计心得体会

PLC自动门课程设计心得体会:通过此次C语言程序设计实践本人实在是获益不浅!C语言是上个学期开的课程所以这个学期并没怎么看过当要开…

-

课程设计心得体会

课程设计心得体会在初学C语言的一个学期后,学校组织我们进行了C语言实训,尝试编写一些有难度的程序。在为期两周的时间中,同组同学共同…

-

20xx年应急演练工作总结

旧县乡人民政府今年以来,我乡应急管理工作在乡党委政府的正确领导和指导下,按照“积极预防、有效应对”的工作思路,紧紧围绕乡经济、社会…

-

唐田小学20xx年亲子活动工作总结 2

唐田小学20xx年亲子活动工作总结家庭教育是建设中国特色社会主义事业的一项基础性工作,是教育系统工程的重要组成部分。亲子教育是学校…

-

应急演练总结

应急预案演练总结我公司按照XX市水利局关于转发XXX市安委办《关于做好20xx年安全生产月应急预案演练周活动的通知》的通知,自6月…

-

会务接待工作总结

20xx年x月x日至18日,中国企业家思想俱乐部一行9人在秘书长于彦忠的带领下,莅临****集团指导考察。本次工作的具体接待工作由…

-

教学计划检查总结1

教学计划检查总结20xx、3、4为加强教学常规管理,督促教师有效完成教学任务,结合实际,3月x日,我校对教师的教学计划和班级计划进…