数电实验报告模板

计算机科学学院

《数字电路》

实验报告

班级:20##级1班

组成员:

指导老师:

日期:

1.实验指导书有的内容全部弄下来

2.实验过程及实验图

3.实验数据

4.实验总结

实验4 时序电路

一、实验目的

1. 掌握常用时序电路分析,设计及测试方法。

2. 训练独立进行实验的技能。

二、实验仪器及材料料

1.双踪示波器 一台

2. Dais或XK实验仪 一台

3.器件 74LS73 双J-K触发器 2片

74LS174 双D触发器 1片

74LS10 三输入三与非门 1片

三、实验内容

1.异步二进制计数器

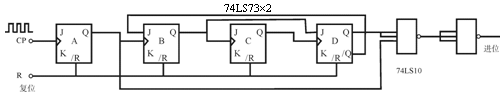

⑴ 按图4-1接线

图4-1

⑵ 由CP端输入单脉冲,测试并记录Q1~Q4端状态及波形。

⑶ 试将异步二进制加法计数改为减法计数,参考加法计数器,要求实验并记录。

四、具体步骤

1、检测芯片

2、链接芯片电路如图

3、加法计数器

Q4~Q1:0000→0001→0010→0011→0100→0101→0110

→0111→1000→1001→1010→1011→1100→1101→1110→1111→0000

减法计数器:

Q4~Q1:1111→1110→1101→1100→1011→1010→1001→1000→0111→0110→0101→0100→0011→0010→0001→0000

2.异步二一十进制加法计数器

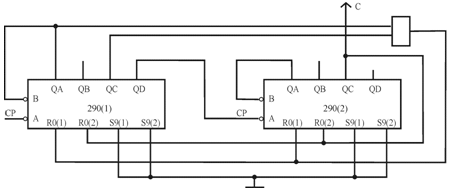

⑴ 按图4-2接线。

图4-2

QA、QB、QC、QD四个输出端分别接发光二极管显示,复位端R接入单脉冲,CP接连续脉冲。

⑵ 在CP端接连续脉冲,观察CP、QA、QB、QC及QD的波形,并画出它们的波形。

⑶ 将图4-1改为一个异步二一十进制减法计数器,并画出CP、QA、QB、QC及QD的波形。

(4)、具体步骤

1、检测芯片

2、连接电路芯片如图

3、波形图如下

3. 自循环移位寄存器一环形计数器。

⑴ 按图4-3接线,将A、B、C、D置为1000,用单脉冲计数,记录各触发器状态。

图4-3

改为连续脉冲计数,并将其中一个状态为“0”的触发器置为“1”(模拟干扰信号作用的结果),观察记数器能否正常工作。分析原因。

具体步骤

1、如上图连接电路,将A,B,C,D置为1000,用单脉冲计数

2、记录触发器状态

1000->1100->1110->1111->0111->0011->0001->0000->1000

能正常工作

⑵ 按图4-4接线,现非门用74LS10三输入端三与非门重复上述实验,对比实验结果,总结关于自启动的体会。

具体步骤

1、连接电路芯片如图

1000->0100->0010->0001->1000

不能自启动

2、与上述结果对比环形计数器的特点是环形计数器的计数模数M=移位寄存器位数

N,且工作状态是依次循环出1,0,如4为环形计数器状态为

0001->0010->0100->1000或1110->1101->1011->0111。设计该类计数器往往要求电路能自启动

实验5 集成计数器

一、实验目的

1.熟悉集成计数器逻辑功能和各控制端作用。

2.掌握计数器使用方法。

二、实验仪器有为材料

1. 双踪示波器 一台

2. Dais或XK实验仪 一台

3. 器件 74LS290 十进制计数器 2片

三、实验内容及步骤

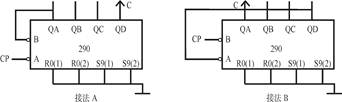

1. 集成计数器74LS290功能测试。

74LS290是二一五一十进制异步计数器。逻辑简图为图5-1所示。

图5-1 74LS290逻辑图

74LS290具有下述功能:

⑴ 直接置0(R0⑴·R0⑵=1),

直接置9(R9⑴·R9⑵=1)

⑵ 二进制计数(CP1输入QA输出)

⑶ 五进制计数(CP2输入QDQAQB输出)

⑷ 十进制计数(两种接法如图5-2A、B所示)。

图5-2 十进制计数器

2.计数器连接

分别用2片74LS290计数器连接成二位数五进制、十进制计数器。

⑴ 画出连线电路图。

⑵ 按图接线,并将输出端接到数码显示器的相应输入端,用单脉冲作为输入脉冲验证设计是否正确。

⑶ 画出四位计数器连接图并总结多级计数器连接规律。

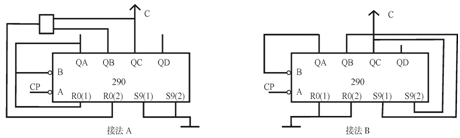

功能表

十进制

双五进制

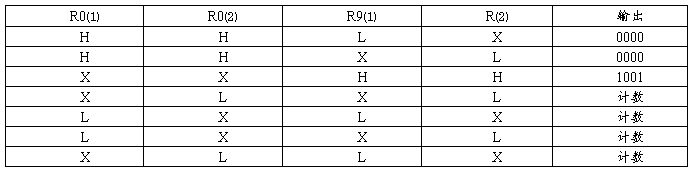

3.任意进制计数器设计方法。

采用脉冲反馈法(称复位法或置位法),可用74LS290组成任意模(M)计数器。图5-3是用74LS290实现模7计数器的两种方案,图(A)采用复位法,即计数计到M异步清0,图(B)采用置位法,即计数计到M-1异步置0。

图5-3 74LS290实现七进制数方法

当实现十以上时制的计数器时可将多片连接使用。

图5-4是45进制计数一种方案,输出为8421BCD码。

图5-4

⑴ 按图5-4接线,并将输出接到显示器上验证。

⑵ 设计一个六十进制计数器并接线验证。

⑶ 记录上述实验各级同步波形。

四、实验报告

1.整理实验内容和各实验数据。

2.画出实验内容1、2所要求的电路图及波形图。

3.总结计数器使用特点。

计数器逻辑功能一般都用功能表或者时序图再附加文字说明,对于带有附加控制端的计数器,除了需要了解正常工作状态下电路的逻辑功能以外,还必须了解附加控制端的作用和用法。了解集成计数器的功能扩展方法,以及用反馈复位发和预置等方法改变计数器的模值。根据给定的功能表和电路具体的连接情况,确定每个计数器的工作方式,进而找出电路状态的转换顺序和相应的输出在多芯片组成的逻辑电路中,还要分析各芯片输出与输人之间的关系,最后得到整个电路的输出与输入间的逻辑关系

第二篇:数电课设模板

华 中 科 技 大 学 课 程 设 计 报 告 数字电路与逻辑设计

课程设计报告

题目:XXX控制器的设计与实现

专 业: 班 级: 学 号: 姓 名: 电 话: 邮 件: 分 组: 完成日期: 指导教师: 赵贻竹

I

华 中 科 技 大 学 课 程 设 计 报 告

团队成员:

II

华 中 科 技 大 学 课 程 设 计 报 告

目 录

1 课程设计概述 ......................................................................................................................................... 5

1.1 课设目的 ...................................................................................................................................... 5

1.2 课设要求 ...................................................................................................................................... 5

1.3 课设任务 ...................................................................................................................................... 5

1.4 实验环境 ...................................................................................................................................... 5

2 基本方案设计 ......................................................................................................................................... 7

2.1 设计需求 ...................................................................................................................................... 7

2.2 总体结构设计 .............................................................................................................................. 7

2.2.1 主模块(main) ............................................................................................................... 7

2.2.2分频模块(frequence_div) ........................................................................................... 10

2.2.3 分频模块(frequence_div2) ........................................................................................ 10

2.2.4 数码管译码模块(display_decode) ............................................ 错误!未定义书签。

2.2.5 数码管译码模块(display_decode2) .......................................... 错误!未定义书签。

2.2.6 数码管位选模块(switch num) .................................................. 错误!未定义书签。

2.3 详细设计 .................................................................................................................................... 12

2.3.1 系统的整体流程及流程图 ............................................................................................. 12

2.3.2 主模块设计说明及流程图 ............................................................................................. 13

2.3.3 分频模块设计说明及流程图 ......................................................................................... 16

2.3.4 数码管译码模块设计说明及流程图 ............................................................................. 16

2.3.5 数码管位选模块设计说明及流程图 ............................................................................. 17

2.4 实验过程与调试 ........................................................................................................................ 18

2.4.1仿真结果 .......................................................................................................................... 12

2.4.2主要故障与调试 .............................................................................................................. 12

2.4.3模块内部图 ...................................................................................................................... 12

III

华 中 科 技 大 学 课 程 设 计 报 告

2.5 功能测试 .................................................................................................................................... 18

3 实验方案的改进意见 ........................................................................................................................... 11

3.1 设计需求 .................................................................................................................................... 11

3.2 改进方案 .................................................................................................................................... 11

3.2.1 时间预约模块结构设计 ................................................................................................. 11

3.2.2 时间预约模块详细设计 ................................................................................................. 11

3.3 仿真与测试 ................................................................................................................................ 11

4 总结与心得 ........................................................................................................................................... 13

4.1 课设总结 .................................................................................................................................... 13

4.2 课设心得 .................................................................................................................................... 13

参考文献 ................................................................................................................................................... 14

附 录 ..................................................................................................................................................... 15

IV

华 中 科 技 大 学 课 程 设 计 报 告

1

1.1 课设目的 课程设计概述

通过硬件描述语言VHDL的编程,深入了解并掌握可编程芯片PLD的设计技术,加强学生对《数字逻辑》课程所学知识综合利用的能力。培养学生创造性思维能力和独立解决实际问题的能力。

1.2 课设要求

(1) 能够全面地应用课程中所学的基本理论和基本方法,完成从设计逻辑电路到设计简单数

字系统的过渡。

(2) 能力独立思考、独立查阅资料,独立设计规定的系统。

(3) 能够独立地完成实施过程,包括安装、布线、测试和排除故障。

1.3 课设任务

(1) 制定出详细设计方案;

(2) 通过Verilog HDL完成规定的设计任务,然后进行编译和仿真,保证设计的正确性;

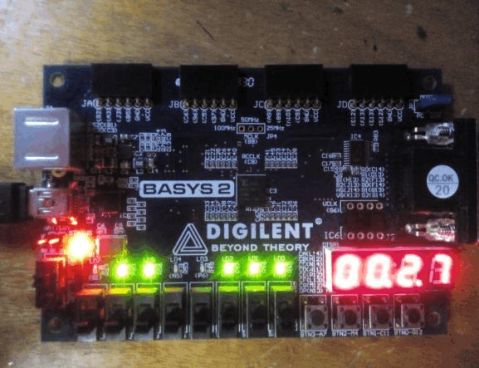

(3) 生成容丝图文件,下载到Basys2开发板,通过实际线路进行验证;

(4) 对复杂系统的设计采取模块化、层次化的设计方法;

(5) 撰写设计报告,并对存在的问题进行分析、提出改进意见。

1.4 实验环境

开发环境ISE Project Navigator:

ISE是使用XILINX的FPGA的必备的设计工具。目前官方提供下载的最新版本是14.4。它可以完成FPGA开发的全部流程,包括设计输入、仿真、 综合、布局布线、生成BIT文件、配置以及在线调试等,功能非常强大。ISE除了功能完整,使用方便外,它的设计性能也非常好,拿ISE 9.x来说,其设计性能比其他解决方案平均快30%,它集成的时序收敛流程整合了增强性物理综合优化,提供最佳的时钟布局、更好的封装和时序收敛映射,从 而获得更高的设计性能。先进的综合和实现算法将动态功耗降低了10%。

5

华 中 科 技 大 学 课 程 设 计 报 告

Basys2 开发板:

Basys2 开发板是一个电路设计实现平台,任何人都可以通过它来搭建一个真正的数字电路。Basys2是围绕着一个Xilinx Spartan-3E FPGA芯片和一个Atmel AT90USB USB控制器搭建的,它提供了完整、随时可以使用的硬件平台,并且它适合于从基本逻辑器件到复杂控制器件的各种主机电路。Basys2板上集成了大量的I/O设备和FPGA所需的支持电路,让用户能够构建无数的设计而不需要其他器件。用户设计可以不局限于Basys2板本身,还可以通过四个标准的扩展连接口延伸到面包板、用户自定义电路或Pmod模板中。所有6针接口上的信号都受到ESD和短路保护,从而确保在任何环境中的使用寿命。Basys2开发板兼容所有版本的Xilinx ISE工具。Basys2附带一个用于供电和编程的USB下载线,所以就不需要其他供电器件或编程下载线。

6

华 中 科 技 大 学 课 程 设 计 报 告

2

2.1 设计需求 基本方案设计

说明该系统的设计需求。

2.2 总体结构设计

说明电路的总体结构设计,包括哪些模块,并对相关模块设计进行说明。

2.2.1 时钟分频

说明该模块的需求,输入,输出、引脚说明等。

2.2.2 LED灯显示管理模块

说明该模块的需求,输入,输出、引脚说明等。

2.3 详细设计

对系统的整体流程进行说明,给出流程图,并对每个模块的设计进行说明,给出流程图。

7

华 中 科 技 大 学 课 程 设 计 报 告

2.3.1 时钟分频

对每个模块的设计进行说明,给出流程图。

2.4

2.4.1 实验过程与调试 仿真结果

给出各种情况的仿真文件,并对仿真文件进行说明,最后给出仿真结果,并对仿真结果进行分析。

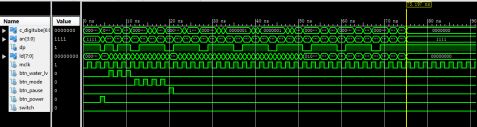

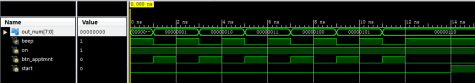

3.1.1 主模块仿真

主模块有6个输入,4个输出,其中输入依次为:时钟(mclk)、水位按键(btn_water_lv)、模式选择按键(btn_mode)、启动/暂停按键(btn_pause)、电源按键(btn_power)以及切换标志(switch)。仿真文件如下所示:

module washing_machine_test;

reg mclk; reg switch; wire [6:0] c_digitube; wire [3:0] an; wire dp; wire [7:0] ld; washing_machine uut ( .mclk(mclk), .btn_water_lv(btn_water_lv), .btn_mode(btn_mode), .btn_pause(btn_pause), .btn_power(btn_power), endmodule

数据全部初始化为0,而后电源按键脉冲一次启动程序,然后水位调节按键三次脉冲后进行四次模式选择,进行漂脱模式,而后模拟启动脉冲开始运行程序。仿真图如3.1.1所示。

8

华 中 科 技 大 学 课 程 设 计 报 告

图3.1.1 主模块仿真测试图

2.4.2 主要故障与调试

(1)故障1

问题描述:某些地方的判断语句不生效

问题分析:这些判断语句失效的地方全为 if({var1,var2} == xx),经过单独测试和查阅资料,{var1,var2}这种形式只能用于赋值语句,判断语句无效。

解决方法:改变写法

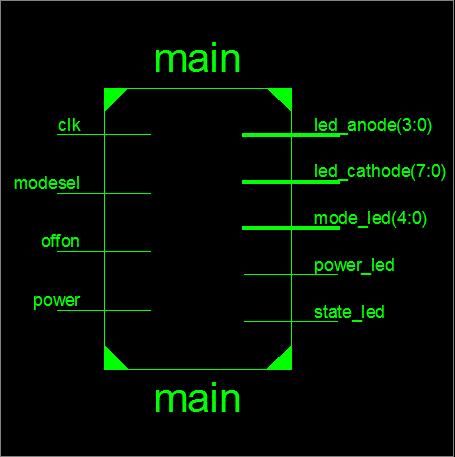

2.4.3 模块内部图(截图并加以说明)

1、主模块

输入:

clk:时钟端

modesel:模式选择

9

华 中 科 技 大 学 课 程 设 计 报 告 offon:暂停启动

power:电源

输出:

led_anode(3:0):七段译码显示器四个显示数字

led_cathode(7:0):七段译码显示器数字的八个显示部件 mode_led(4:0):模式led灯以及进出水led灯

2.5 功能测试

3.3.1 水位调节功能测试

对测试过程和测试结果进行说明:

图3.3.1 水位调节模块测试结果图

10

华 中 科 技 大 学 课 程 设 计 报 告

3

3.1 设计需求 实验方案的改进意见

新增时间预约功能,现实生活中经常不需要即时洗衣服而定时,该模块便用于实现该功能,通过。倒计时结束后即进行选择的模式。

3.2

3.2.1 改进方案 时间预约模块结构设计

时间选择范围为0~60,接引脚设置如表2.2.7所示。

表4.2.1时间预约模块引脚表

3.2.2 时间预约模块详细设计

图4.2.1 时间预约模块流程图

3.3 仿真与测试

4.3.1 时间预约模块仿真

预

r appointmnt uut (

11

华 中 科 技 大 学 课 程 设 计 报 告

数据电源标志初始化为1,其余输入变量初始为0,然后触发6次预约脉冲,相当于预约时间为6(最高可60),得到仿真图3.1.2如下。

图4.3.1 预约模块仿真测试图

4.3.2 时间预约模块测试

预约时间可调范围为0~60,且须在模式开始前进行选择,由于switch开关决定了模式选择按钮的功能是模式选择还是时间预约,故需要先将设计的拨动开关往上,实验测试图如下:

图4.3.3 时间预约模块倒计时效果图

四个数码管前两个显示的是预约的时间,后面现实的是时间的倒计时,开始是预约时间的倒计时,然后是所选择的洗衣模式的倒计时。最后倒计时完成后若无操作,则进入自动断电警告环节,对应的指示灯闪烁五次仍无操作则系统自动断电。

12

华 中 科 技 大 学 课 程 设 计 报 告

4

4.1 课设总结 总结与心得

为了实现洗衣机系统的功能要求,作了如下几点工作:

1) 整个设计过程分为了早期的基本功能的实现,中期的预约功能添加以及后期的系统

的仿己分析和请教同学,完成了对主要模块的仿真以及

2) 电(auto_off),这些实现了上述的基本功能。另外还设计了辅助模块,为了满足不

能。

3)

. 块仿真图,以此来辅助对整个系统的调试。

4.2 课设心得

1)

2)

3) 这请教同学,不能堆积,这样学才会有进步。 习的弊病,也让我不得不直视自己的缺点,从而学到了更多,理解得更深。 对了。

13

华 中 科 技 大 学 课 程 设 计 报 告

参考文献

[1]

欧阳

14

华 中 科 技 大 学 课 程 设 计 报 告

附 录(源程序)

15

-

数电实验报告模版

HarbinInstituteofTechnology数字逻辑电路与系统课程名称院系班级哈尔滨工业大学20xx年11月实验二时序逻…

-

数字电路实验报告模板

组合逻辑电路的设计与调试一、实验目的1、掌握用门电路设计组合逻辑电路的方法。2、掌握组合逻辑电路的调试方法。二、实验器材数字电路实…

-

数电实验报告模板

交通灯逻辑控制电路设计交通灯逻辑控制电路设计一绪论1意义交通的发达标志着城市的发达相对交通的管理则显得越来越重要对于复杂的城市交通…

-

数电实验报告模板

计算机科学学院数字电路班级20xx级1班组成员指导老师日期1实验指导书有的内容全部弄下来2实验过程及实验图实验报告3实验数据4实验…

-

数电实训报告模板

实训报告实训名称数字电子技术实习专业电子信息工程班级电信1017班组员1111学号1112指导老师陈榕福实习时间1011第2学期第…

-

数电实验报告

数字电子技术实验报告中频自动增益数字电路研究学院班级姓名学号指导老师电子信息工程学院通信1309目录一设计任务要求2基础部分2发挥…

-

数电实验报告

数电实验报告班级学号姓名班内序号20xx年5月30日一实验内容及要求一Quartus原理图输入法设计1用逻辑门设计实现一个半加器仿…

-

数电实验报告

信息工程学院20xx20xx学年第一学期课程设计报告课程名称数字电子技术课程设计班级学号电信1201班12610103151093…

-

哈工大数电实验报告

HarbinInstituteofTechnology数字逻辑电路与系统课程名称院系班级哈尔滨工业大学20xx年11月实验二时序逻…

-

数电实验报告

数电实验报告一实验要求实验目的1熟悉用QuartusII原理图输入法进行电路设计和仿真2掌握QuartusII图形模块单元的生成与…

-

数字电路实验报告模板

组合逻辑电路的设计与调试一、实验目的1、掌握用门电路设计组合逻辑电路的方法。2、掌握组合逻辑电路的调试方法。二、实验器材数字电路实…