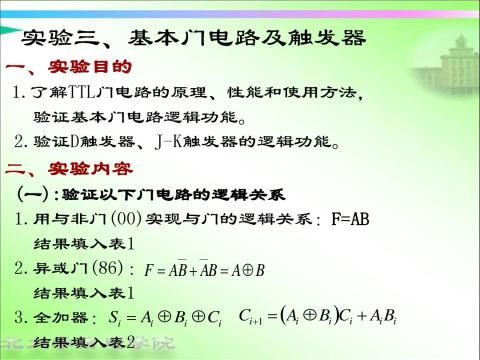

实验三、基本门电路及触发器 电子版实验报告

实验三:基本门电路及触发器实验

实验三:基本门电路及触发器实验

实 验 室: 实验台号: 日 期:

专业班级: 姓 名: 学 号:

一、实验目的

1.了解TTL门电路的原理、性能和使用方法;验证基本门电路逻辑功能。

2.验证D触发器;J-K触发器的逻辑功能。

二、实验内容

(一)验证以下门电路的逻辑关系

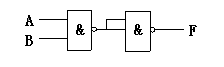

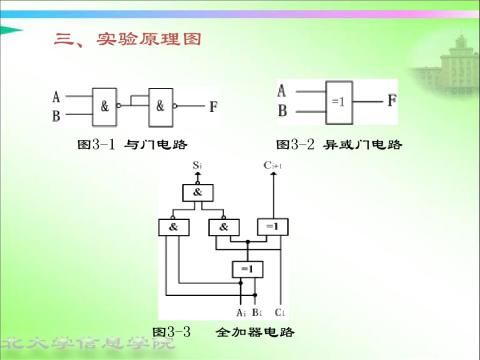

1. 用与非门(00)实现与门逻辑关系:F=AB

1. 用与非门(00)实现与门逻辑关系:F=AB

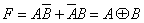

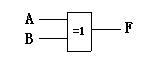

2. 异或门(86):

2. 异或门(86):

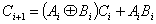

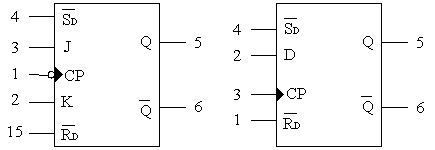

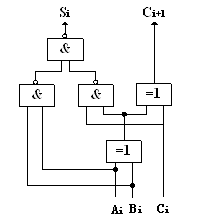

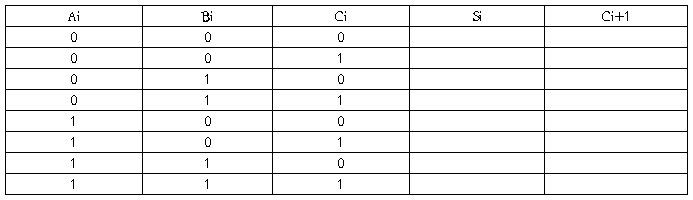

3. 全加器(00、86):

3. 全加器(00、86):

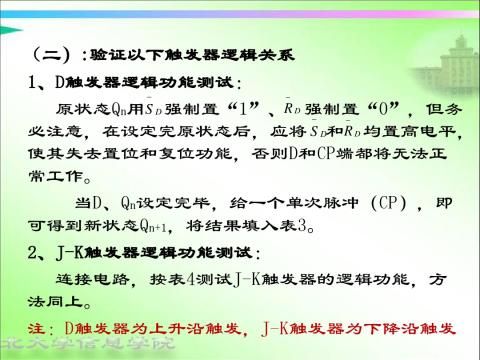

(二)验证以下触发器逻辑关系

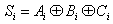

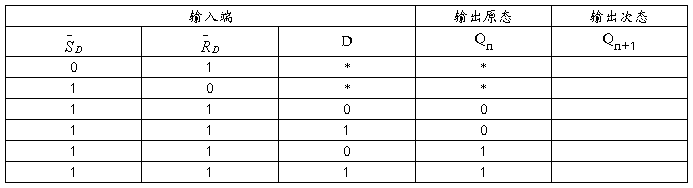

1.D触发器置位端、复位端的功能测试。

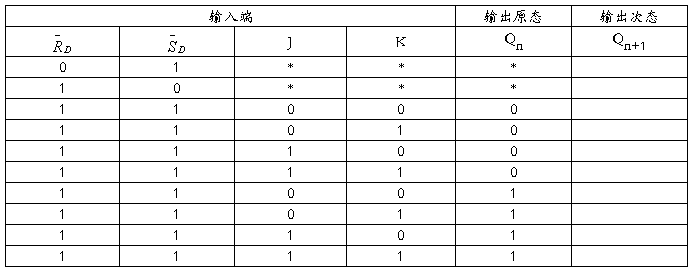

2.J-K触发器置位端、复位端的功能测试。

3.D、J-K触发器功能测试。

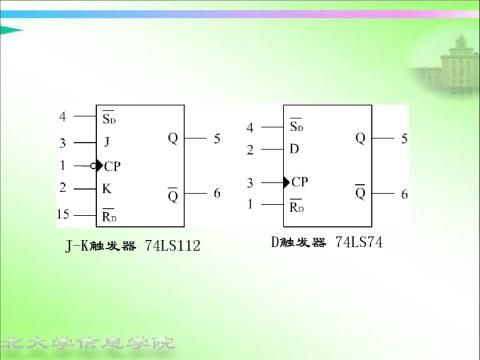

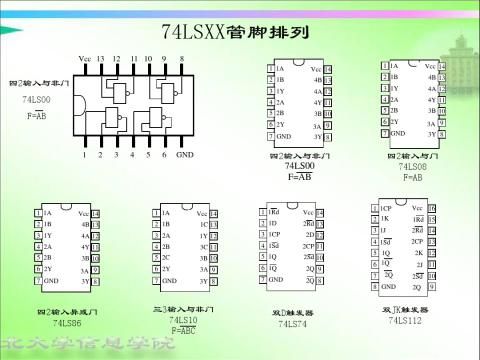

图3-1 JK触发器(74LS112)和D触发器(74LS74)

三、实验原理图

三、实验原理图

图3-2与门电路 图3-3异或门电路 图3-4 全加器电路

四、实验结果及数据处理

1.直接在实验原理图上标记芯片的引脚。

2.写出实验结果。

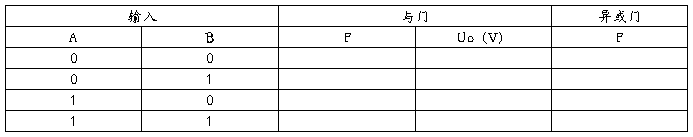

(1)与门、异或门实验结果表(用数字万用表测量高低电平1、0的电压值。)

(2)全加器实验结果表

(4)D触发器的功能测试

(5)J-K触发器的功能测试

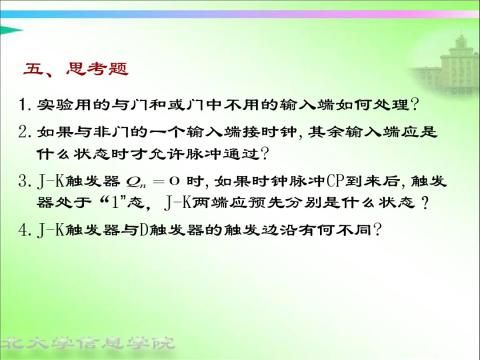

五、思考题

1.实验用的与非门和或门中不用的输入端如何处理?

2.如果与非门的一个输入端接时钟,其余输入端应是什么状态时才允许脉冲通过?

3.J-K触发器Qn=0时,如果时钟脉冲CP到来后,触发器处于“1”态,J-K两端应预先分别是什么状态?

J端为高电平 K端高电平或低电平

4.J-K触发器与D触发器的触发边沿有何不同?

J-K触发器是下降沿触发:当CP=1时,从触发器被封锁,输出保持原有状态不变,主触发器接收J.K输入端信号。当CP由1变0,主触发器被封锁。存储在主触发器中的信号送入从触发器。输出新状态。

D触发器是下降沿触发

第二篇:实验三、基本门电路及触发器

-

实验1 基本门电路及数字电_

实验一基本门电路及数字实验台的使用一实验目的1熟悉各种基本逻辑门电路的逻辑符号和逻辑功能2掌握集成门电路器件的使用及逻辑功能测试方…

-

集成门电路功能测试实验报告

集成门电路功能测试实验报告一实验预习1逻辑值与电压值的关系2常用逻辑门电路逻辑功能及其测试方法3硬件电路基础实验箱的结构基本功能和…

-

门电路实验报告

实验报告实验课题门电路实验目的掌握电路连接排除故障和调试的方法实验仪器与器材1数字电子技术实验系统实验内容及步骤TTL门电路逻辑功…

-

实验三、基本门电路及触发器 电子版实验报告

实验三基本门电路及触发器实验实验室实验台号日期专业班级姓名学号一实验目的1了解TTL门电路的原理性能和使用方法验证基本门电路逻辑功…

-

实验三、基本门电路及触发器 电子版实验报告(2)

实验三基本门电路及触发器实验室实验台号日期专业班级姓名学号一实验目的二实验内容一验证以下门电路的逻辑关系1用与非门00实现与门逻辑…

-

电路实验报告

一、实验目的及要求1.掌握三相负载作星形连接、三角形连接的方法,验证这两种接法下,线电压、相电压及线电流、相电流之间的关系。2.充…

-

数字电路与逻辑设计实验报告1-深圳大学

深圳大学实验报告课程名称学院计算机与软件学院实验时间实验报告提交时间教务部制注1报告内的项目或内容设置可根据实际情况加以调整和补充…

-

电路实验报告

数字电路实验报告姓名:***学号:***学院:信息学院专业:计算机科学与技术指导教师:***协助指导教师:20XX年12月28日实…

-

电路基础实验报告

电路基础实验报告一20xx923基尔霍夫定律和叠加定理的验证组长曹波组员袁怡潘依林王群梁泽宇郑勋一实验目的通过本次实验验证基尔霍夫…

-

电路实验报告

电路与电子线路基础课外设计制作总结报告题目E直流电源电压监控电路设计组号11任课教师组长20成员20成员20成员20成员20联系方…

-

晶体管共射极单管放大电路实验报告

实验二晶体管共射极单管放大器一、实验目的1.学会放大器静态工作点的调式方法和测量方法。2.掌握放大器电压放大倍数的测试方法及放大器…