FPGA电子秒表综合实验报告

一、 实验名称:

用VHDL实现基于FPGA的电子秒表

二、 实验目的:

1. 掌握基本的VHDL语言,可以实现简单的程序编写

2. 对系统设计原理、单元电路设计方法及仿真技术有所了解

3. 学会使用ISE软件与Modelsim仿真软件

三、 实验内容:

(一) 实验任务:

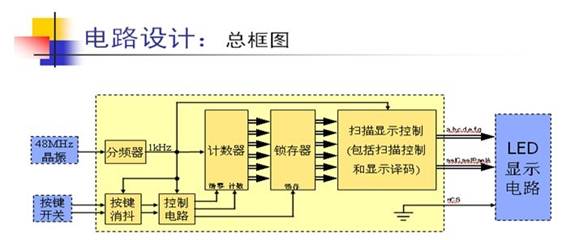

(二) 电路设计:

? 分频器:对晶体振荡器产生的时钟信号进行分频,产生时间基准信号;

? 计数器:对时间基准脉冲进行计数,完成计时功能;

? 数据锁存器:锁存数据使显示保持暂停;

? 控制器:控制计数器的运行、停止以及复位,产生锁存器的时能信号;

? 扫描显示与控制电路:包括扫描计数器、数据选择器和七段译码器,控制八个 数码管以扫描方式显示记时结果;

? 按键消抖电路:消除按键输入信号抖动的影响,输出单脉冲。

四、 实验仪器与软件

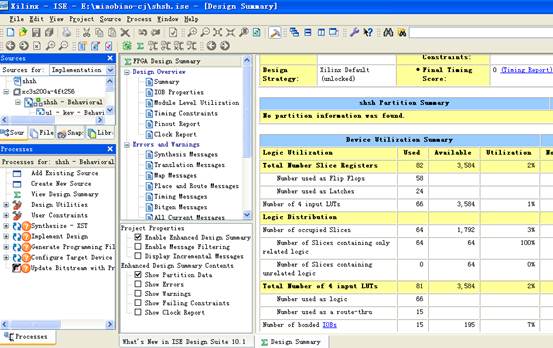

1.ISE软件,界面如下

该软件编程步骤:创建工程项目;设计输入;功能仿真;设计综合;设计实现;生

成编程文件;配置目标器件。

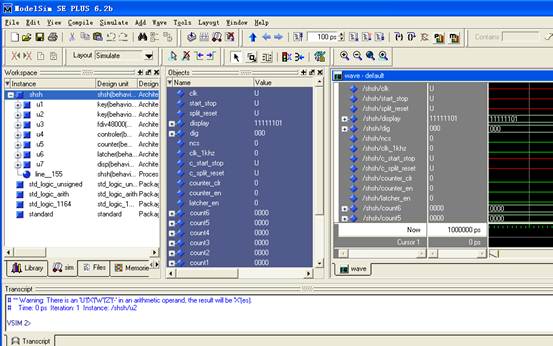

2..Modelsim软件,界面如下:

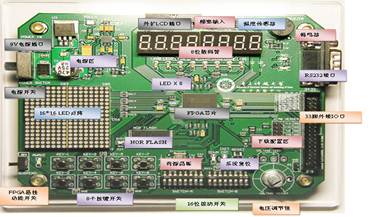

3.FPGA实验电路板:

五、 实验过程:

1. 程序编写

该程序采用采用嵌套结构编写,先设计一个主程序,然后再分步写出分频器、按键消抖、按键控制、计数器、锁存器、扫描显示几个子模块。首先设置了clk,start_stop,split_reset三个输入变量,分别表示时钟信号、开始停止控制以及分段复位控制;另设置了display,dig,ncs三个输出变量,分别表示显示输出,位选和接地。

2. 显示电路部分:

七段显示译码器中小数点位由于都设置为‘1’,所以都不亮,按键控制由于管脚设置的约束,kye-1代表开始停止,key-2代表分段复位。

六、 实验结果

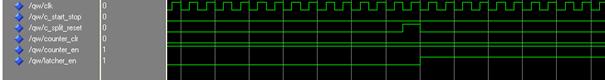

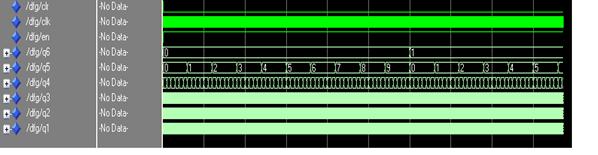

1.分频器的作用是把48Mhz的晶振信号分频为1khz的标准时钟信号,分给按键消抖、 计数器、锁存器和扫描显示部分作为时钟输入。

分频器仿真:

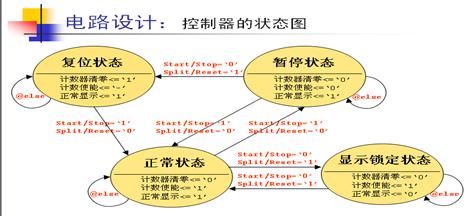

2.按键控制电路的作用是由按键输入信号,输出计数器的使能、清零信号,和锁存器的使能信号,以此来控制计数器的运行、停止和清零,还有锁存器的运行和停止。用case语句将3个输出的初始状态state按照输入的不同,转换到下个状态new_state。然后写另一个进程,当标准时钟信号到来时,把处理完的信号new_state赋给state作为输出。状态图如下:

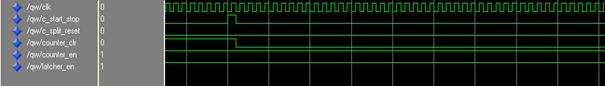

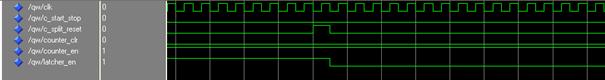

按下开始停止键,将开始停止控制键设置为‘1‘,开始计时,保持1000ns后松开开始键,计时仍在进行中,延续1ms。

再次按下开始停止键,保持1000ns后松开,此时暂停计时,保持1ms。

再按下分段复位键复位,保持1000ns后松开,此时处于复位状态,延续1ms。

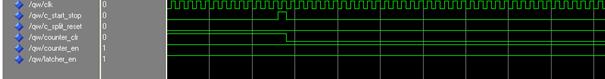

最后再开始计时,1ms后按下分段复位键分段,保持1000ns后松开,此时仍在计时只是在数码显示管上不显示走秒,1ms后再按下此键,则正常计时。

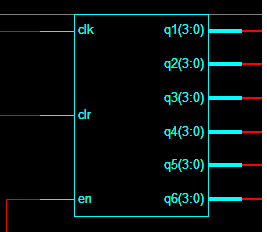

3.计数器是秒表的核心部分,作用是对时钟信号进行计数,输出各位的计数结果,从而完成计时功能。计数器有3个输入:100hz的时钟信号、清零、使能,6个结果输出q1,q2,q3,q4,q5,q6。由于共需要输出的计数结果为6个:十毫秒、百毫秒、秒、十秒、分、十分,而其中十秒和十分为6进制,其他为10进制,故需4个10进制计数器和2个6进制计数器按顺序级联。计数器部分电路图如下:

10进制计数器是由模10的加法器和触发器组成,原理同分频器,只是在加法器中用if语句设定了只有当进位输入信号为‘1’时,加法器才进行加1的工作,否则不加1而直接把state赋给new_state。在触发器中还设置了清零输入clr的功能,即在clr=‘1’时,将state的所有位全变0。最后对进位输出进行定义:只有当进位输入carry_in=‘1’而且state=9的时候,进位输出carry_out=‘1’,由此把6个计数器级联起来。6进制计数器的设计只需把10进制计数器的模10改为模6即可,但输出的计数结果信号必须仍为4位,将输出位数统一起来,减少后面的麻烦。

10进制计数器是由模10的加法器和触发器组成,原理同分频器,只是在加法器中用if语句设定了只有当进位输入信号为‘1’时,加法器才进行加1的工作,否则不加1而直接把state赋给new_state。在触发器中还设置了清零输入clr的功能,即在clr=‘1’时,将state的所有位全变0。最后对进位输出进行定义:只有当进位输入carry_in=‘1’而且state=9的时候,进位输出carry_out=‘1’,由此把6个计数器级联起来。6进制计数器的设计只需把10进制计数器的模10改为模6即可,但输出的计数结果信号必须仍为4位,将输出位数统一起来,减少后面的麻烦。

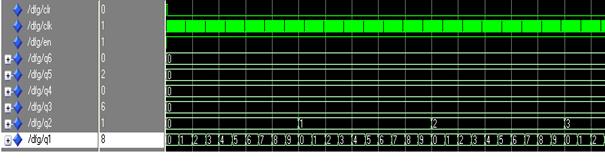

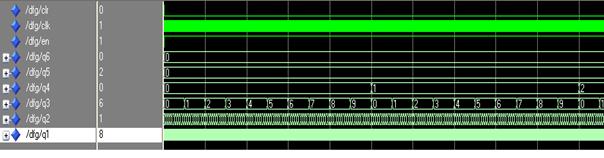

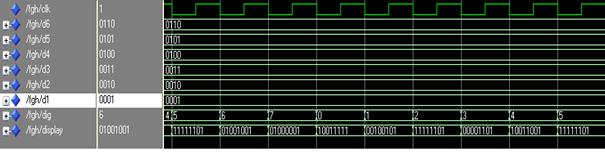

仿真结果如下:

q1代表10ms位,当q1计数到9时进一位。

q2代表100ms位,当q2计数到9时进一位。

q3代表秒个位,当q3计数到9时进一位。

q4代表秒十位,当q4计数到5时进一位。

q5代表个分位,当q5计数到9时进一位。

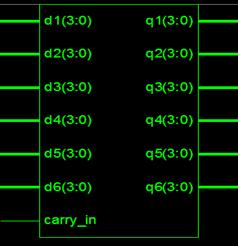

4.锁存器的作用是把数据锁存使显示保持暂停。有6个由计数器出来的输入,和6个输出,还有一个使能端。其原理很简单,就是一个触发器,当使能信号=‘1’时,触发器工作,把计数器的6个输出d1-d6赋给另外6个变量q1-q6,作为显示部分的输入;而当使能信号=‘0’时,不作任何赋值,也就是使显示部分的输入信号保持不变,产生显示保持暂停的效果。结构如右图:

4.锁存器的作用是把数据锁存使显示保持暂停。有6个由计数器出来的输入,和6个输出,还有一个使能端。其原理很简单,就是一个触发器,当使能信号=‘1’时,触发器工作,把计数器的6个输出d1-d6赋给另外6个变量q1-q6,作为显示部分的输入;而当使能信号=‘0’时,不作任何赋值,也就是使显示部分的输入信号保持不变,产生显示保持暂停的效果。结构如右图:

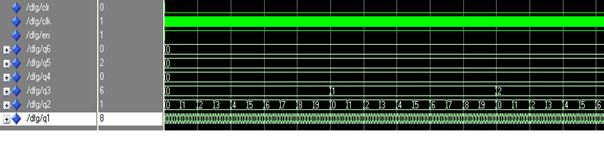

5.显示译码部分的作用是控制8个数码管以扫描的方式显示计数输出结果。由6个由锁存器出来的输入,2个输出,一个时钟输入组成。扫描计数器是一个模8计数器,产生扫描信号,同时也是选择8个数码管的信号。数据选择器根据扫描信号来控制6个计数结果的轮流输出,另外还有两个输出为横杠。七段译码器是将输入的bcd码转换成控制数码管中的7段LED的信号,显示数字0-9以及横杠。

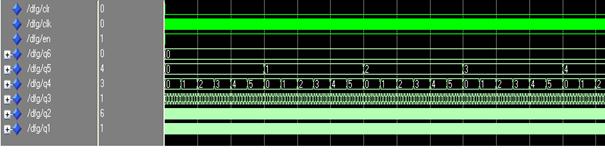

先将d1—d6分别设为1,2,3,4,5,6。由下面的仿真结果,dig为2,5时,表示横杠位,对应七段译码管显示为“11111101”; dig为0时,选择d1输出,输出结果“10011111”,同设置的d1为1一致;dig为1时,选择d2输出,输出结果“00100101”,同设置的d2为2一致;dig为3时,选择d3输出,输出结果“00001101”,同设置的d3为3一致;dig为4时,选择d4输出,输出结果“10011001”,同设置的d4为4一致;dig为6时,选择d5输出,输出结果“01001001”,同设置的d5为5一致;dig为7时,选择d6输出,输出结果“01000001”,同设置的d1为1一致。

七、实验结论

本实验通过用VHDL程序编写,在ise软件中综合,并用modelsim软件仿真,最后下载到FPGA实验板上实现了秒表的功能,测试了程序的正确性。

八、实验心得

通过本次试验,收获良多,学会了如何运用VHDL语言编写程序,基本掌握了运用modelsim软件进行仿真,以及设计组合和时序电路的方法,进一步丰富了自己编程方面的知识,为以后的工作打下了基础。

第二篇:60s电子秒表综合性实验报告

重庆交通大学

信息科学与工程学院

综合性实验报告

姓 名: X X 学 号XXXXXXXXXX

班 级:

实验项目名称: 60s电子秒表

实验项目性质: 设计性实验

实验所属课程: 数字电子技术基础

实验室(中心): XXXX

指 导 教 师 : XXX

实验完成时间: 2011 年 12 月 01 日

一、实验目的

1.熟悉计数器的工作原理及特点;

2.学习设计N进制加法计数器的方法;

3.掌握电子秒表的设计方法。

二、实验内容及要求

1.实验内容:

用两片74161芯片和一些门电路设计一个60秒的电子秒表,熟悉计数器的工作和特点,并观察实际电路工作情况。

2.实验要求:

1)自己设计一个60秒的电子秒表;

2)完成实验报告,附上电路图及仿真结果;

3)总结数字电路设计的一般方法,掌握常见的数字电路设计的软件;

4)总结电子秒表的设计方法。

三、实验原理

1、 原理:

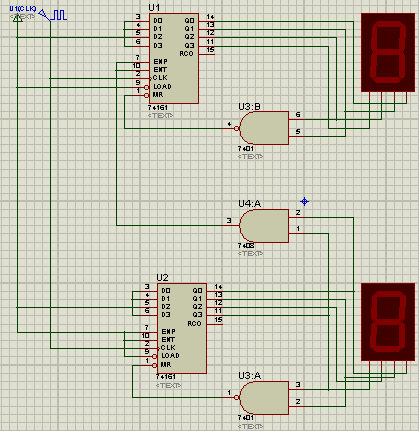

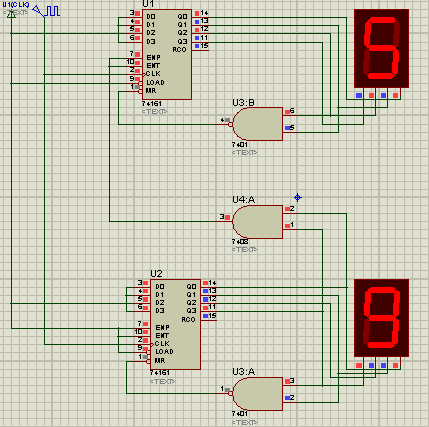

根据实验要求可知,秒表的低位是10进制,高位是6进制,使74161处于计数状态,分别用与非门反馈到74161中的RD'端,当低位达到1001的时候,低位显示9,下一个状态为0,而向高位进1,则通过与门将低位输出端为1001的信号反馈到控制高位的74161的EP.ET端,使得芯片2(控制高位的)的状态翻转一次,最终在显示译码器上观察到60的秒表。

2、 原理图:

四、实验仪器、材料

1、数字逻辑电路实验箱 1个

2、74161芯片 2片

3、7401、7408芯片 各1片

五.实验过程及原始记录(含原理图及必要的计算)

1、 实验仿真图:

如图电子秒表低位每次计数到9秒,与非门便有效使74161置零,所以下一个脉冲就会从0开始重新计数;当然此时与门也生效,使高位74161处于计数状态,下一个脉冲就会开始计数,由于高位74161只在与门电路生效时才处于计数状态,所以高位只在低位处于9之后有机会计数;当然高位已经将0110之后的状态置零使其为六进制,这样一来电路就会合作完成60s的循环以完成实验的要求。

2、 实验结果及分析

1) 实验结果:

当电路接入脉冲时,电路开始工作,电子秒表开始工作,开始计数。从00开始,低位每经过10s便置零,高位每经过6s便置零,直到59秒结束,等到下一个脉冲到来的时候,电子秒表又从00开始到59秒,以此循环。

2) 实验分析:

从00开始计时,低位的开始实现计数器功能,当达到9时,即1001的时候,将输出为1的端口通过与非门和与门分别反馈给芯片1的LD'端和芯片2的EP.ET端,使得高位进1,当高位ET.EP端为1的时候,高位实现计数器功能,最后使得秒表显示59,等到下一个CP到来,计数器归零,秒表开始从新计数。

六、实验体会

通过此次实验

1、 学会了电子秒表的设计方法及N进制计数器的设计方法;

2、 熟悉了计数器的工作原理及特点;

3、 更加熟悉了protues仿真软件的应用;

4、 激发了对数字电路的学习兴趣。

-

电子秒表实验报告

电子技术设计性实训报告学号211002146姓名邱富烨同组人夏文彬班级指导老师林雪健日期20xx0907目录一实训目的3二设计功能…

-

电子科技大学电子技术综合实验秒表实验报告

130现代电子技术综合实验电子秒表设计学生姓名学号指导老师学院提交时间摘要本文介绍了使用VHDL开发FPGA的一般流程重点介绍了电…

-

FPGA电子秒表综合实验报告

现代电子综合实验报告课题名称电子秒表程序设计一实验名称用VHDL实现基于FPGA的电子秒表二实验目的1掌握基本的VHDL语言可以实…

-

电子秒表实验报告

课程设计综合实验报告20xx20xx年度第1学期名称VHDL语言与系统设计题院系电气与电子工程学院班级信息10011002班学号学…

-

电子秒表设计实验报告

淮阴工学院数字电子技术课程实验期末考核20xx20xx学年第2学期实验名称电子秒表电路的设计班级学号姓名学院专业系别指导教师成绩2…

-

场营销综合模拟实验小组实验报告(终极版)

市场营销模拟实验实验报告公司名称第二组组员姓名班级指导老师报告成绩实验日期NEO公司学号年月日至负责的任务年月日一实验目的10分通…

-

电子综合实验实验报告-13(光照强度检测仪)

电子电路实验3综合设计总结报告题目数字式光照强度检测仪的设计实现班级20xx0824学号20xx082427姓名张希希成绩日期一摘…

-

电子技术综合实验报告模板

中南民族大学电子信息工程学院电子技术综合实验报告题目指导教师充电器原理年级专业学号姓名年月日电子技术综合实验报告1功能与技术指标1…

-

20xx电子电路综合实验实验报告范例

电子电路综合实验题目班级学号姓名成绩日期总结报告说明格式按照给定模板蓝字部分是说明可删掉红字部分是示例供参考一摘要归纳总结实验内容…

-

电子电路与综合实验报告模板

电子电路与综合实验报告模板按电子电路与综合实验教学大纲要求本实验共有11个其中14为虚拟EDA实验511为实物实验每位同学请提交1…

-

电子秒表实验报告

电子技术设计性实训报告学号211002146姓名邱富烨同组人夏文彬班级指导老师林雪健日期20xx0907目录一实训目的3二设计功能…