计算机组成原理实验报告(系统总线和具有基本输入输出功能的总线接口实验)

池州学院数学计算机科学系实验报告

专业: 计算机科学与技术 班级: 实验课程: 计算机组成原理

姓名: 学号: 实验室: 硬件实验室

同组同学:

实验时间: 20##年5月29日 指导教师签字: 成绩:

系统总线和具有基本输入输出功能的总线接口实验

一 实验目的和要求

1.理解总线的概念及其特性。

2.掌握控制总线的功能和应用。

二 实验环境

PC机一台,TD-CMA 实验系统一套

三 实验步骤及实验记录

按图连接电路

首先将时序与操作台单元的开关KK1、KK3置为‘运行’档,开关KK2置为‘单拍’档, 按动CON单元的总清按钮CLR,并执行下述操作。

① 对MEM进行读操作(WR=0,RD=1,IOM=0),此时E0灭,表示存储器读功能信号有效。

② 对MEM进行写操作(WR=1,RD=0,IOM=0),连续按动开关ST,观察扩展单元数据指示灯,指示灯显示为T3时刻时,E1灭,表示存储器写功能信号有效。

③ 对I/O进行读操作(WR=0,RD=1,IOM=1),此时E2灭,表示I/O读功能信号有效。

④ 对I/O进行写操作(WR=1,RD=0,IOM=1),连续按动开关ST,观察扩展单元数据指示灯,指示灯显示为T3时刻时,E3灭,表示I/O写功能信号有效。

四 实验结果与分析

第二篇:计算机组成原理实验4.2_实验报告

学生实验报告

学 院:软 件 学 院

专 业:软 件 工 程

年 级:2010级

学 号: 24320102202460

学生 姓名:高伟

同组学生姓名:何建明

实验课程名称:计算机组成原理实验

实验 名称:具有中断控制功能的总线接口实验

指导 教师:曾文华、蔡艺军、廖凌宇

实验 时间: 2012.4.9 19:00--21:00

实验 地点:漳州校区生化楼603

20##年4月18日

一、 实验目的与要求[ZWH1] 1.11111

1.掌握中断控制信号线的功能和应用

2.掌握在系统总线上设计中断控制信号线的方法

二、 实验设备

1、TD-CMA教学实验系统1台(通过USB串行接口与PC微机相连)

2、PC微机1台

三、 实验原理[a2]

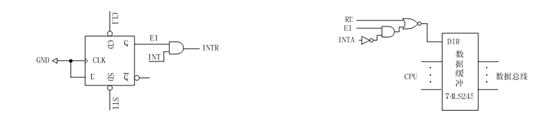

为了实现中断控制,CPU 必须有一个中断使能寄存器,并且可以通过指令对该寄存器进行 操作.设计下述中断使能寄存器,其原理如图 4-2-1 所示.其中 EI 为中断允许信号,CPU 开中 断指令 STI 对其置 1,而 CPU 关中断指令 CLI 对其置 0.每条指令执行完时,若允许中断,CPU 给出开中断使能标志 STI,打开中断使能寄存器,EI 有效.EI 再和外部给出的中断请求信号一 起参与指令译码,使程序进入中断处理流程.

本实验要求设计的系统总线具备有类 X86 的中断功能,当外部中断请求有效,CPU 允许响 应中断,在当前指令执行完时,CPU 将响应中断.当 CPU 响应中断时,将会向 8259 发送两个 连续的 INTA 信号,请注意,8259 是在接收到第一个 INTA 信号后锁住向 CPU 的中断请求信号 INTR(高电平有效) ,并且在第二个 INTA 信号到达后将其变为低电平(自动 EOI 方式) ,所以, 中断请求信号 IR0 应该维持一段时间,直到 CPU 发送出第一个 INTA 信号,这才是一个有效的 中断请求.8259 在收到第二个 INTA 信号后,就会将中断向量号发送到数据总线,CPU 读取中 断向量号,并转入相应的中断处理程序中.在读取中断向量时,需要从数据总线向 CPU 内总线 传送数据.所以需要设计数据缓冲控制逻辑,在 INTA 信号有效时,允许数据从数据总线流向 CPU 内总线.其原理图如图 4-2-2 所示.其中 RD 为 CPU 从外部读取数据的控制信号.

图 4-2-1 中断使能寄存器原理图 图 4-2-2 数据缓冲控制原理图

在控制总线部分表现为当 CPU 开中断允许信号 STI 有效,关中断允许信号 CLI 无效时,中 断标志 EI 有效,当 CPU 开中断允许信号 STI 无效,关中断允许信号 CLI 有效时,中断标志 EI 无效.EI 无效时,外部的中断请求信号不能发送给 CPU.

四、 实验步骤[ZWH3]

1、实验接线:

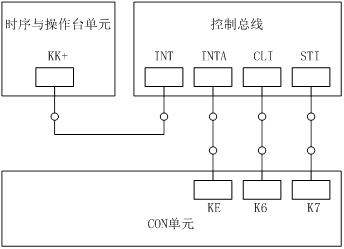

图 实验接线图

(时序与操作台单元)KK+-------INT(控制单元)

(控制单元)INTA’-----------K5(CON单元)

(控制单元)CLI---------------K6(CON单元)

(控制单元)STI---------------K7(CON单元)

2、实验步骤:

(1)对总线进行置中断操作(K6=1,K7=0),观察控制总线部分的中断允许指示灯EI,此时EI亮,表示允许响应外部中断。按时序与操作台单元的开关KK,观察控制总线单元的指示灯INTR,发现当开关KK按下时INTR变亮,表示总线将外部的中断请求送到CPU。

(2)对总线进行清中断操作(K6=0,K7=1),观察控制总线部分的中断允许指示灯EI,此时EI灯灭,表示禁止响应外部中断。按时序与操作台单元的开关KK,观察控制总线单元的指示灯INTR,发现当开关KK按下时INTR不变,仍然为灭,表示总线锁死了外部的中断请求。

(3)对总线进行置中断操作(K6=1,K7=0),当CPU给出的中断应答信号INTA‘(K5=0)有效时,使用电压表测量数据缓冲74LS245的DIR(第1脚),显示为低,表示CPU允许外部送中断向量号。

五、 实验结果[ZWH4] 与讨论

实验结果符合预期。

主要说明本实验要达到的目的和具体的要求(实验将实现的功能)

描述本实验的基本原理

给出实验过程中的详细步骤,其中实验接线请列出本实验所接的所有线

给出本实验得到的有关结果和结论,并对有关实验现象进行讨论

-

计算机组成原理实验报告

计算机组成原理实验报告软件学院计算机组成原理实验报告专业班级学号日期学生姓名指导教师计算机组成原理实验报告运算器组成实验一实验目的…

-

计算机组成原理 电子科大技大学 实验报告

课程名称计算机组成原理学院计算机科学与工程专业计算机科学与技术指导教师王学生姓名郭学号实验成绩日期实验报告勇小明20xx06010…

- 计算机组成原理实验报告-存储器

-

计算机组成原理实验报告1

计算机组成原理实验报告1姓名学号教师时间地点机位实验名称数据传送实验一实验目的1理解自然语言形式命令的人工译码过程2学习系统部件和…

-

《计算机组成原理》运算器实验报告

《计算机组成原理》实验报告学院:专业:班级学号:AP0804114学生姓名:实验日期:指导老师:成绩评定:五邑大学信息学院计算机组…

-

农林大学计算机组成原理课程实习报告模板(新)

福建农林大学金山学院课程名称实习题目姓名系专业年级学号指导教师职称课程实习报告计算机组成原理普通的加减法指令柳继曾机电与信息工程系…

- 计算机组成原理实验报告 存储器

-

存储器试验 《计算机组成原理》实验报告

计算机组成原理实验报告计算机组成原理实验报告正文用纸页数可随意扩充标题使用黑体不加粗字号小二段前段后为自动行间距15倍正文中文使用…

-

存储器和IO扩展实验,计算机组成原理

科技学院课程设计实验报告20xx20xx年度第一学期名称计算机组成原理综合实验题目院系信息工程系班级学号学生姓名指导教师李梅王晓霞…

- 计算机组成原理实验报告-存储器

-

《计算机组成原理》运算器实验报告

《计算机组成原理》实验报告学院:专业:班级学号:AP0804114学生姓名:实验日期:指导老师:成绩评定:五邑大学信息学院计算机组…