组成原理总线实验报告

计算机科学与技术系

实 验 报 告

专业名称 计算机科学与技术

课程名称 计算机组成原理

项目名称 具有基本输入输出功能的总线接口实验 班 级 15计科专升本

学 号 1504081001 姓 名 胡宇帆

同组人员 无

实验日期 2015/10/22

一、实验目的与要求

1、理解总线的概念及其特性。

2、掌握控制总线的功能及应用。

二、实验逻辑原理图与分析

2.1 画实验逻辑原理图

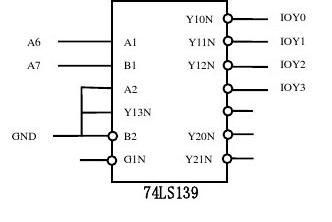

图 1-1 I/O 地址译码原理图

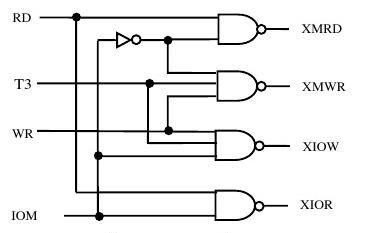

图 1-2 读写控制逻辑

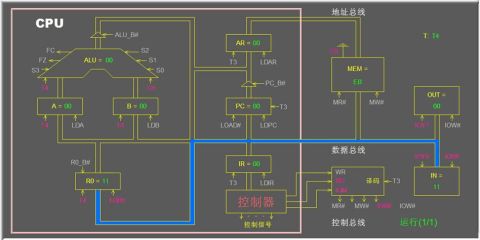

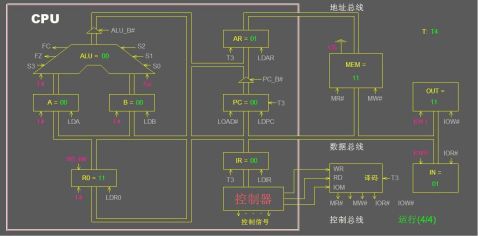

图1-3 总线传输实验框图

2.2 逻辑原理图分析 由于存储器和输入、输出设备最终是要挂接到外部总线上,所以需要外部总线提供数据信号、地址信号以及控制信号。在该实验平台中,外部总线分为数据总线、地址总线、和控制总线,分别为外设提供上述信号。外部总线和CPU 内总线之间通过三态门连接,同时实现了内外总线的分离和对于数据流向的控制。地址总线可以为外部设备提供地址信号和片选信号。由地址总线的高位进行译码,系统的I/O地址译码原理见图1-1(在地址总线单元)。由于使用A6、A7进行译码,I/O地址空间被分为四个区,如表1-1所示。

为了实现对于MEM和外设的读写操作,还需要一个读写控制逻辑,使得CPU能控制MEM和I/O设备的读写,实验中的读写控制逻辑如图1-2 所示,由于T3的参与,可以保证写脉宽与T3一致,T3由时序单元的TS3给出。IOM用来选择是对I/O设备还是对MEM进行读写操作,IOM=1时对I/O设备进行读写操作,IOM=0时对MEM进行读写操作。RD=1时为读,WR=1时为写。

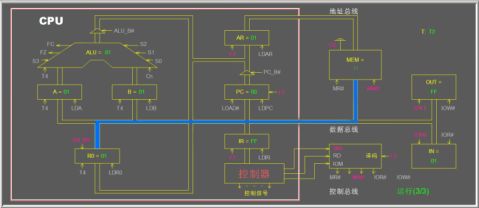

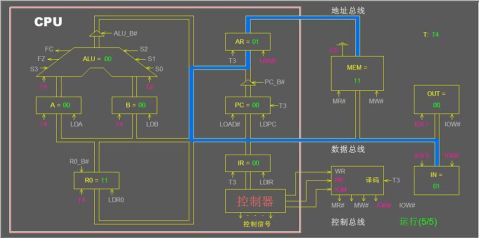

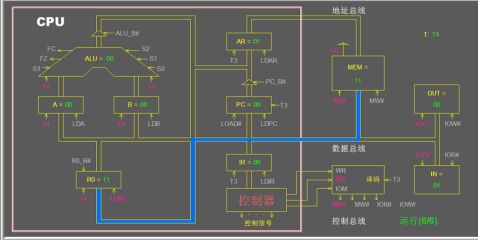

三、 数据通路图及分析 (画出数据通路图并作出分析)

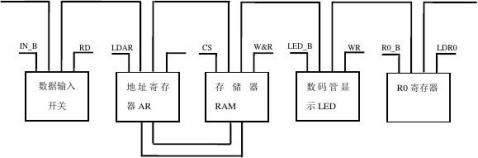

1、输入设备将11H打入R0寄存器

2、将R0中的数据11H打入存储器01H单元

3、将当前地址的存储器中的数据写入到R0寄存器中

4、将R0寄存器中的数用LED数码管显示

四、实验数据和结果分析

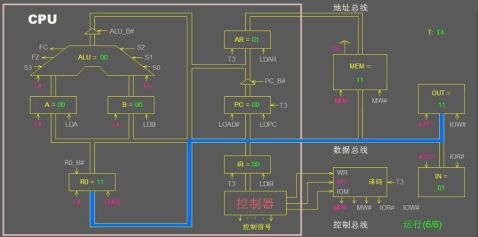

4.1 实验结果数据如图所示

4.2 结果数据分析

1.将IN单元数据写入RO IN 00010001

K7=1

K6=1

WR\RD\IOM=011

LDAR=0

2.将IN单元数据写入AR

IN 00000001

K7=1

K6=0

WR\RD\IOM=011

LDAR=1

3.将RO中的数据写入MEM

K7=0

K6=0

WR\RD\IOM=100

LDAR=0

4.将IN单元数据写入AR

IN 00000001

K7=1

K6=0

WR\RD\IOM=011

LDAR=1

5.将MEM中的数据写入RO

K7=1

K6=1

WR\RD\IOM=010

LDAR=0

6.将RO中的数据写入OUT单元

K7=0

K6=0

WR\RD\IOM=101

LDAR=0

五、实验问题分析、思考题与小结

1、 存储器和输入、输出设备最终是要挂接到外部总线上,因此需要外部总线提供数据信 号、地址信号 以及控制信号。

2、外部总线和 CPU 内总线之间通过三态门连接,同时实现了内外总线的分离和对于数据流向的控制。 而地址总线可以为外部设备提供地址信号和片选信号。

3、为了实现对于 MEM 和外设的读写操作,还需要一个读写控制逻辑,使得 CPU 能控制 MEM和 I/O 设备的读写

4、WR=0,RD=1,IOM=0时,表示存储器读功能信号有效。 WR=1,RD=0,IOM=0 连续按动开关ST,当指示灯显示为 T3 时刻时,表示存储器写功能信号有效。 WR=0,RD=1,IOM=1时,表示 I/O 读功能信号有效。 WR=1,RD=0,IOM=1时,观察扩展单元数据指示灯,指示灯显示为 T3 时刻时,表示 I/O 写功能信号有效

5、在接线时为了方便,可将管脚接到 CON 单元闲置的开关上,若开关打到 1,等效于接到VCC;若开关打到0,等效于接到GND。

六、其它

得分(百分制)

实验报告分析评价

第二篇:《组成原理》实验报告-2

贵州大学 计算机科学与信息学院

计算机科学与技术系 实验报告纸

-

计算机组成原理课程设计报告

西安科技大学课程设计报告课程名称计算机组成原理课题名称复杂模型计算机的设计专业计算机科学与技术班级计科1001班姓名李用维念文洪吴…

-

计算机组成原理实验报告

计算机组成原理实验报告软件学院计算机组成原理实验报告专业班级学号日期学生姓名指导教师计算机组成原理实验报告运算器组成实验一实验目的…

-

计算机组成原理实验报告

上海大学计算机学院计算机组成原理实验报告5姓名盛俊学号11121763教师王雪娟时间周一57机位11报告成绩实验名称综合应用1一实…

-

计算机组成原理 电子科大技大学 实验报告

课程名称计算机组成原理学院计算机科学与工程专业计算机科学与技术指导教师王学生姓名郭学号实验成绩日期实验报告勇小明20xx06010…

-

组成原理实验报告

计算机组成理实验报告院系计算机科学与技术专业计算机科学与工程班级计科111学号090511101姓名指导教师谢从华设计地点N620…

-

现场总线实验报告-基于PROFIBUS-DP的彩灯控制

现场总线课程设计报告书院部别班级学号姓名指导教师时间现场总线课程设计任务书题目基于PROFIBUSDP的彩灯控制系部专业班级学生姓…

- 现场总线实验报告

-

现场总线实验报告

现场总线技术实验报告学校成都理工大学学院核技术与自动化工程学院专业电气工程及其自动化姓名班级学号指导老师黄洪全实验一KeilC51…

- 现场总线实验报告

-

计算机组成原理实验报告 存储器和总线实验

西华大学数学与计算机学院实验报告课程名称计算机组成原理指导教师祝昌宇实验名称存储器和总线实验年级20xx级姓名蒋俊学号3120xx…

-

《计算机组成原理》运算器实验报告

《计算机组成原理》实验报告学院:专业:班级学号:AP0804114学生姓名:实验日期:指导老师:成绩评定:五邑大学信息学院计算机组…