计算机组成原理设计实验报告

计算机组成原理设计实验报告

学院:计算机科学与工程学院

专业:网络工程

班级:

学号:

姓名:

评分:

20##年 5月 31日

试验一 验证74LS181运算和逻辑功能

实验目的

(1)掌握算术逻辑单元(ALU)的工作原理;

(2)熟悉简单运算器的数据传送通路;

(3)画出逻辑电路图及布出美观整齐的电路连接图;

(4)验证4位运算功能发生器(74LS181)组合功能;

实验原理

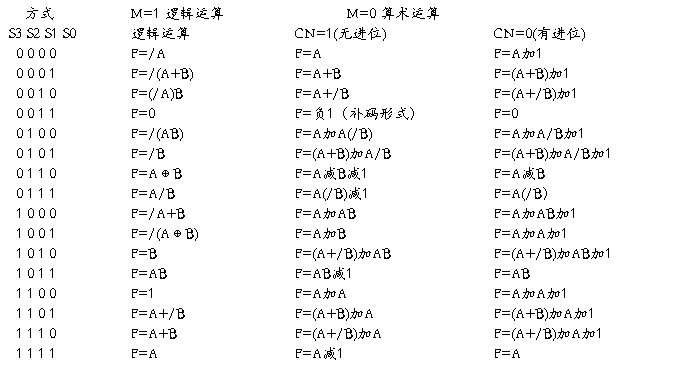

ALU能进行多种算术运算和逻辑运算。4位ALU-74LS181能进行16种算术运算和逻 辑运算。功能如下:

实验内容

实验电路图:见附录1。

ALU-74LS181引脚说明:M=1 逻辑运算,M=0 算数运算。

验证74LS181型4位ALU的逻辑算术功能,填写下表:

说明:HGFEDCBA八个为操作数,LKJI四个开关为操符。

总结及心得体会:

掌握了算数逻辑单元的工作原理,熟悉了简单运算器的数据传送通路,学会画逻辑电路图和初步美化接线图,熟悉了74LS181的组合功能。

在初学画电路图的时候,主要的问题就是找不到元件,后来经过同学们的互相讨论,最终弄清楚了各个元件所在的分类,和启用帮助文件,将英文板式改为中文等多种功能。

对于实验开始只知道傻傻的连线,连完后做习题时才逐渐将整个电路原理弄清楚。通过老师的悉心指导,我们还复习有关数字电子电路的知识。使我们受益匪浅,激发了我的学习兴趣。

当做完第一个试验后,我还因为没有对连线布局好特意重做了一遍。填表的时候由于实验经验不足,总是将数据的输入混淆,以至于重做了许多次实验。这方面还是应该在试验中提高。

实验二 运算器(2)

1、 实验目的

(1) 熟练掌握算术逻辑单元(ALU)的应用方法;

(2) 进一步熟练简单运算器的数据传送原理;

(3) 画出逻辑电路图及布出美观整齐的接线图;

(4) 熟练掌握有关数字原件的功能的使用方法

(5) 熟练掌握子电路的创建及使用

2、 实验原理

本实验仿真单线总线结构的运算器,原理如图2-2所示。相应的电路如图2-3所示。

电路图中,上右下三方的8条线模拟8位数据总线;k8产生所需数据;74244层次块为三态门电路,将部件与总线连接或断开,切记总线上只能有一个输入;两个74273层次块作为暂存工作寄存器DR1和DR2;两个74374层次块作为通用寄存器组(鉴于电路排列情况,只画出两个通用寄存器GR1和GR2,如果可能更的话可以设计4个或8个通用寄存器);众多的开关作为控制电平或打入脉冲;众多的8段代码管显示相应位置的数据信息;核心为8位ALU层次块。

3、 实验内容

在multisim画出电路图并仿真,完成如下操作。

(1) 说明整个电路工作原理。

答: K8产生所需数据,通过74244层次块,将产生数据输入总线,将数据存入由74LS374层次块构成的通用寄存器组GR1和GR2;通过其他 74LS244的开关,将通用寄存器里的数据放到74LS273层次块作为的暂存工作寄存器DR1和DR2中;将DR1和DR2中的数据通过核心8位ALU层次块运算,将结果又保存到GR1或者GR2中。众多的开关作为控制电平或打入脉冲;众多的8段代码管显示相应位置的数据信息;

(2) 说明74LS244N的功能及其在电路中作用,及输入信号G有何作用;

答:74LS244层次块为三态门电路,在电路中将部件与总线连接或断开,起开关作用,当G为低电平时,部件连接,G为高电平时,部件断开。

(3) 说明74LS273N的功能及其在电路中作用,及输入信号CLK有何作用;

答:74LS273N作为临时工作寄存器,在电路中临时寄存数据,CLK上跳沿触发工作。

(4) 说明74LS374N的功能及其在电路中的作用,及输入信号CLK及OC有何作用;

答:74LS374层次块为通用寄存器组,在电路中寄存数据,同时具有三态门的作用。CLK遇上升沿触发,OC为低电平时,部件连接,OC为高电平时,部件断开。

(5) K8产生任意数据存入通用寄存器GR1.

答:1K8产生数据,将所有的74244层块的G端接1(高电平)X3.G=0,将数据输入总线; 2X8.oc=0,X8.clk=↑(X8的clk端由低电平跳变为高电平),将数据存入了GR1。

(6) K8产生任意数据存入通用寄存器GR2.

答:1K8产生数据,将所有的74244层块的G端接1(高电平),X3.G=0将数据输入总线; 2X11.oc=0,X11.clk=↑(X8的clk端由低电平跳变为高电平),将数据存入了GR2。

(7) 完成GR1+GR2àGR1.

答:1所有74244层块G端接1,X9.G=0,X1.G=0,X2.clk=↑,X9.G=1;X10.G=0,X6.G=0,X7.clk=↑,X10.G=1; 2令S3S2S1S0=1001,M=0,CN=1;X12.G=0,X8.oc=0,X8.clk=↑;

(8) 完成GR1-GR2àGR2。

答:1所有74244层块G端接1,X9.G=0,X1.G=0,X2.clk=↑,X9.G=1;X10.G=0,X6.G=0,X7.clk=↑,X10.G=1; 2令S3S2S1S0=0110,M=0,CN=0;X12.G=0,X11.oc=0,X11.clk=↑;

(9) 完成GR1^GR2àGR1.

答:1所有74244层块G端接1,X9.G=0,X1.G=0,X2.clk=↑,X9.G=1;X10.G=0,X6.G=0,X7.clk=↑,X10.G=1; 2令S3S2S1S0=0001,M=0,CN=1;X12.G=0,X8.oc=0,X8.clk=↑;;

(10) 完成GR1v GR2àGR2.

答:1所有74244层块G端接1,X9.G=0,X1.G=0,X2.clk=↑,X9.G=1;X10.G=0,X6.G=0,X7.clk=↑,X10.G=1; 2令S3S2S1S0=0110,M=0,CN=0;X12.G=0,X11.oc=0,X11.clk=↑;

(11) 完成GR1⊕GR2àGR1.

答:1所有74244层块G端接1,X9.G=0,X1.G=0,X2.clk=↑,X9.G=1;X10.G=0,X6.G=0,X7.clk=↑,X10.G=1; 2令S3S2S1S0=0110,M=1;X12.G=0,X8.oc=0,X8.clk=↑;

(12) ~GR1àGR2.(“~”,表示逻辑非运算)

答:1所有74244层块G端接1,X9.G=0,X1.G=0,X2.clk=↑,X9.G=1;2令S3S2S1S0=0000,M=1,X12.G=0,X11.oc=0,X11.clk=↑;

(13) ~GR2àGR1.

答:1所有74244层块G端接1,X9.G=0,X1.G=0,X2.clk=↑,X9.G=1;2令S3S2S1S0=0110,M=0,CN=0;X12.G=0,X8.oc=0,X8.clk=↑;

实验电路图

K8模块:由8个开关组成。

74_244模块:由两个74LS244集合而成。

74_273

74_374模块

总结及心得体会:

通过实验二,我清楚了算术逻辑运算的原理和方法,明白了简单运算器的数据传输原理。能布美观整齐的接线图。通过单个对单个元件的测试,用F1打开的帮助文件,我弄清楚了74LS244,74LS273,74LS374等数字元件的功能和使用方法。熟练的掌握了子电路的创建和使用方法。

试验中,发现了几个必须重视的问题:1、必须保证只有一组数据输入到总线。与总线相连的起三台门作用的74244层块只能打开一个。2、在设计电路时错误的修改方法,比如开电源时修改,删除子元件管脚,选错元件等都可能导致不能修改或程序损坏。3、在对元件连线前,要学会查资料,确定元件的作用,这样才有利于对整个电路逻辑功能的分析。

实验二是个对我启发很大的实验,是实验仪的延伸,但是他的内容远远高于时验一。布线选元器件时,我们直接参考的实验指导书,在对电路图分析的时候,老师问了一些很细致的问题,加深了我们对电路图的理解。我们也复习了相关的计算机组成原理的相关知识。

通过这两个实验,激发了我的学习兴趣。我的动手能力也得到了锻炼。收获很多。

-

计算机组成原理课程设计的实验报告

长治学院课程设计报告课程名称计算机组成原理课程设计设计题目设计一台性能简单的计算机系别计算机系专业计科1101班组别第三组学生姓名…

-

计算机组成原理课程设计报告

课程设计报告课程设计名称计算机组成原理系别三系学生姓名班级学号成绩指导教师开课时间一设计题目计算机组成原理课程设计简单模型机的微程…

-

计算机组成原理设计实验报告

计算机组成原理设计实验报告学院:计算机科学与工程学院专业:网络工程班级:学号:姓名:评分:20##年5月31日试验一验证74LS1…

-

计算机组成原理课程设计实验报告

计算机组成原理课程设计实验报告学院专业班级学号姓名评分20xx年6月8日实验一一实验名称验证74LS181运算和逻辑功能二实验目的…

-

计算机组成原理课设报告

沈阳工程学院计算机组成原理课程设计设计题目基本模型机的设计与实现第六组系别班级学生姓名学号指导教师职称起止日期20xx年6月25日…

-

计算机组成原理课程设计心得

计算机组成原理课程设计心得计科1004计算机组成原理课程设计是在我们上完计算机组成原理课之后的硬件实践课程,是把组成原理课上的理论…

-

农林大学计算机组成原理课程实习报告模板(新)

福建农林大学金山学院课程名称实习题目姓名系专业年级学号指导教师职称课程实习报告计算机组成原理普通的加减法指令柳继曾机电与信息工程系…

-

计算机组成原理课程设计报告

计算机组成原理课程设计报告课程设计题目计算机组成原理专业名称计算机科学与技术班级20xx240202关童20xx24020xx7张…

-

计算机组成原理课程设计实验报告

计算机组成原理课程设计实验报告学院专业班级学号姓名评分20xx年6月8日实验一一实验名称验证74LS181运算和逻辑功能二实验目的…

-

计算机组成原理课程设计报告

西安科技大学课程设计报告课程名称计算机组成原理课题名称复杂模型计算机的设计专业计算机科学与技术班级计科1001班姓名##指导教师#…

-

《计算机组成原理》运算器实验报告

《计算机组成原理》实验报告学院:专业:班级学号:AP0804114学生姓名:实验日期:指导老师:成绩评定:五邑大学信息学院计算机组…