计算机组成原理一位全加器实验报告

实验二 一位全加器实验

姓名: 钱相州 班级: 网工1201 学号: 1205110707

【实验环境】

1. Windows 20## 或 Windows XP

2. QuartusII、GW48-PK2或DE2-115计算机组成原理教学实验系统一台,排线若干。

【实验目的】

1、熟悉原理图和VHDL语言的编写。

2、验证全加器功能。

【实验原理】

设计一个一位全加器,能完成两个二进制位的加法操作,考虑每种情况下的进位信号,完成8组数据的操作。

【原理图设计】

【实验总结】

通过实验,学会了功能仿真如何做出,并且了解了自己在知识中不足的地方,通过自己动手,解决问题,提高了自己的动手能力。

第二篇:EDA一位全加器

南昌大学实验报告

学生姓名: ## 学 号: ## 专业班级: 中兴101

实验类型:□ 验证 □ 综合 ■ 设计 □ 创新 实验日期:20##、10、12

实验一一位二进制全加器设计实验

一、实验目的

1、学习Quartus II的文本和原理图输入方法设计简单组合电路以熟悉QuartusII的使用;

2、熟悉设备和软件,掌握实验操作。

二、实验内容与要求

(1)在利用VHDL编辑程序实现半加器和或门,在主层中进行应用。熟悉层次设计概念;

(2)给出此项设计的仿真波形;

(3)参照实验板的引脚号,选定和锁定引脚,编程下载,进行硬件测试。

三、设计思路

1 ,一个1位全加器可以用两个1位半加器及一个或门连接而成。而一个1位半加器可由基本门电路组成。半加器的真值表为

其中a为被加数,b为加数,co为本位向高位进位,so为本位和

因而可得表达式为: co=ab 而so= ab+ab =a⊕b

因而可得表达式为: co=ab 而so= ab+ab =a⊕b

其VHDL文本如下

LIBRARY IEEE; --半加器描述(1):布尔方程描述方法

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY h_adder IS

PORT (a, b : IN STD_LOGIC;

co, so : OUT STD_LOGIC);

END ENTITY h_adder;

ARCHITECTURE fh1 OF h_adder is

BEGIN

so <= NOT(a XOR (NOT b)) ; co <= a AND b ;

END ARCHITECTURE fh1;

2,而全加器的真值表如下;

2,而全加器的真值表如下;

其中ain为被加数,bin为加数,cin为低位向本位的进位,count为本位向高位的借位,sum为本位和

所以,一位全加器的表达式如下:

Sum=ain⊕bin⊕cin

count=ainbin+cinain+cinbin

3,或门VHDL文本如下

LIBRARY IEEE ; --或门逻辑描述

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY or2a IS

PORT (a, b :IN STD_LOGIC;

c : OUT STD_LOGIC );

END ENTITY or2a;

ARCHITECTURE one OF or2a IS

BEGIN

c <= a OR b ;

END ARCHITECTURE one;

四、VHDL文本输入法设计

常用的硬件描述语言(HDL)就是VHDL语言,同原理图设计方法类似,首先打开Quartus II 7.2建立工程文件,然后选择菜单File->New,在Device Design Files标签选项框中选择VHDL File。

LIBRARY IEEE; --半加器描述(1):布尔方程描述方法

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY h_adder IS

PORT (a, b : IN STD_LOGIC;

co, so : OUT STD_LOGIC);

END ENTITY h_adder;

ARCHITECTURE fh1 OF h_adder is

BEGIN

so <= NOT(a XOR (NOT b)) ; co <= a AND b ;

END ARCHITECTURE fh1;

LIBRARY IEEE ; --或门逻辑描述

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY or2a IS

PORT (a, b :IN STD_LOGIC;

c : OUT STD_LOGIC );

END ENTITY or2a;

ARCHITECTURE one OF or2a IS

BEGIN

c <= a OR b ;

END ARCHITECTURE one;

LIBRARY IEEE; --1位二进制全加器顶层设计描述

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY f_adder IS

PORT(ain,bin,cin : IN STD_LOGIC;

cout,sum : OUT STD_LOGIC);

END ENTITY f_adder;

ARCHITECTURE fd1 OF f_adder IS

COMPONENT h_adder --调用半加器声明语句

PORT ( a,b : IN STD_LOGIC;

co,so : OUT STD_LOGIC);

END COMPONENT;

COMPONENT or2a

PORT (a,b : IN STD_LOGIC;

c : OUT STD_LOGIC);

END COMPONENT;

SIGNAL d,e,f : STD_LOGIC; --定义3个信号作为内部的连接线。

BEGIN

u1 : h_adder PORT MAP(a=>ain,b=>bin,co=>d,so=>e);--例化语句

u2 : h_adder PORT MAP(a=>e,b=>cin,co=>f,so=>sum);

u3 : or2a PORT MAP(a=>d,b=>f,c=>cout);

END ARCHITECTURE fd1;

六、VHDL文本输入法设计实验步骤

1.新建项目,选择项目文件夹,输入工程名称,添加文件(一般为空),选择芯片型号,选择仿真工具(一般为默认),最后生成项目。

2.新建VHDL文件,输入设计语言,保存时要注意与工程文件名相同。如下图:

图(2)文本输入

3.保存好后,进行综合编译,如果有错误,折回修改。

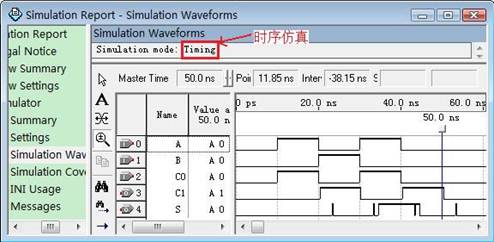

4、建立波形文件,导入结点,并设置好仿真结束时间,保存文件,进行仿真设置,然后进行波形仿真,如下图:

图(4)

六、仿真波形分析

.如下图:

图(5)波形分析

经过分析,可知仿真结果与真值表相同

因此,仿真正确。

七、硬件测试

1.选择菜单Assignment->Assignment Editor->Pin窗口,选择菜单ViewàShow All Known Pin Names,此时编辑器将显示所有的输入输出信号,其中“To”列是信号列,“Location”列是引脚列,“General Function”列显示该引脚的通用功能。对于一个输入输出信号,双击对应的“Location”列,在弹出的下拉列表框内选择需要锁定的引脚号。

2.引脚锁定后,保存,必须重新进行一次全程编译,编译通过后才能编程下载。

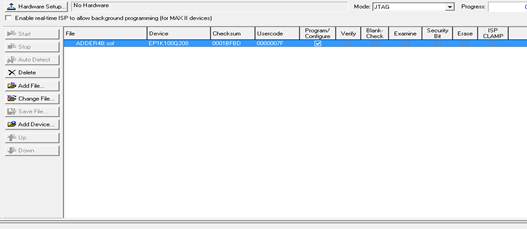

3.编程下载,用下载线将计算机并口和试验箱上的JTAG口接起来,接通电源。

选择Tools—>Programmer菜单,打开programmer窗口。

在mode中选中JTAG,将Program/Configure下的笑方框选中

4在开始编程之前,必须正确设置编程硬件。点击“Hardware Setup”按钮,打开硬件设置口。

3)点击 Add Hardware 按钮,出现 Add Hardware 对话框,如图 1-35 所示。

图 1-35 编程硬件选择对话框

4)在 Add Hardware 对话框中,从 Hardware type 列表中选择所需要硬件类型,如果是 USB 接口的请参照用户使用手册中的 USB 电缆的安装与使用,如果使用的是并口下载线则选取如图 1-35 所示的硬件类型,点击 OK 按钮,完成对硬件类型的设置。回到编程器硬件设置窗口,点击 Close按钮退出设置。则在编程器对话框中的编程硬件类型会出现刚才选取的编程器硬件。

5)如果软件已运行一个工程,则在打开编程器的时候,编程器窗口会自动出现这个工程文件要加载到目标器件的文件,如果要加载其它文件可以从其它地方进行添加更改。选好加载文件后,再点选 Progam/Configure,编程模式选取 JTAG 模式,点击 STRAT 进行文件加载,直到加载进度变为 100%,文件成功加 载完成。

八、硬件测试结果

硬件测试:根据真值表,本次实验中,我的ain bin cin 分别取的是K1.K2.K3而输出count sum取的是LED1和LED2,它们会根据K1.K2.K3的不同而显示亮灭,如输入000 ,由于输出count sum均为低电平,因此LED1和LED2均灭,输入111由于输入count sum均为高电平,因此LED1和LED2均亮,依据全加器真值表依次验证过后,结果与真值表相符合。试验成功。

九、试验心得

1、通过本次实验我基本熟悉了QUARTUSII的使用,分别学会了原理图输入法和VHDL文本输入法,同时也学会了波形仿真,波形仿真要观察到程序所要的结果,应该正确设置仿真时间,否则无法全面显示程序要实现的功能。

2、在QUARTUSII软件使用方面,还是要注意一些细节问题,如原理图输入与VHDl文本输入保存文件时不能保存在同一个文件夹下,否则在文本文件编译时,会提示半加器元件已存在,导致文件编译无法通过。工程名,vhdl文件名一定要与实体名相同等

3、硬件测试方面,要正确添加硬件、正确设置引脚进行引脚锁定,然后一定不要忘记重新全程编译一遍,接下来是下载,有时由于接触不好会下载失败,我把实验箱关掉电源,重新插了下连接线,重新打开后,下载成功。

十、参考资料

《EDA技术实用教程》 《EDA/SOPC系统开发平台》

-

一位全加器实验报告

计算机组成原理课程实验实验题目实验报告正文一律使用A4打印纸打印或手写页眉上标明XXXX课程实验字样页面设置上边距25cm下边距2…

-

一位全加器的实验报告

专业班级20xx级电子2班学号1020xx07姓名周娟EDA技术实验报告实验项目名称在QuartusII中用原理图输入法设计1位加…

-

1位全加器实验报告

浙江万里学院实验报告课程名称可编程逻辑器件应用实验名称全加器的设计专业班级通信姓名黄文龙学号20xx014139实验日期20xx3…

-

计算机实验报告---一位全加器

计算机实验报告一位全加器系别烟大软件工程专业班级学生姓名学生学号20xx25503223指导教师潘庆先一位全加器一实验目的用门电路…

-

全加器实验报告

数电实验报告二组合逻辑电路(半加器、全加器及逻辑运算)一、实验目的1、掌握组合逻辑电路的功能测试。2、验证半加器和全加器的逻辑功能…

-

EDA实验报告(四选一、四位比较器、加法器、计数器、巴克码发生器)

EDA实验报告姓名学号班级实验14选1数据选择器的设计一实验目的1学习EDA软件的基本操作2学习使用原理图进行设计输入3初步掌握器…

-

深圳大学全加器实验报告

深圳大学实验报告实验课程名称数字电路与逻辑设计实验项目名称学院专业软件工程报告人学号班级指导教师实验时间实验报告提交时间教务处制实…

-

一位全加器VHDL的设计实验报告

EDA技术及应用实验报告一位全加器VHDL的设计班级XXX姓名XXX学号XXX一位全加器的VHDL设计一实验目的1学习MAXPLU…

-

全加器实验报告

数电实验报告二组合逻辑电路(半加器、全加器及逻辑运算)一、实验目的1、掌握组合逻辑电路的功能测试。2、验证半加器和全加器的逻辑功能…

-

4位全加器实验报告

四位全加器11微电子黄跃1117426021实验目的采用modelsim集成开发环境利用verilog硬件描述语言中行为描述模式结…

-

四位全加器实验报告

武汉轻工大学数学与计算机学院计算机组成原理实验报告题目4位二进制计数器实验专业软件工程班级130X班学号1305110XXX姓名X…