VHDL实验报告--宁剑

硬件描述语言期末实验报告

题

目:姓 名 宁剑 学 号 xxxxxxxxxxx 年级专业 指导教师 xxxxx

20xx年6月20日

河北大学xxxx届本科生VHDL硬件实验论文(设计)

河北大学本科生VHDL硬件实验论文(设计)

硬件描述语言实现秒表功能

摘 要

应用VHDL语言设计数字系统,很多设计工作可以在计算机上完成,从而缩短了数字系统的开发时间。我们尝试利用VHDL为开发工具设计数字秒表。

秒表的逻辑结构较简单,它主要由十进制计数器、六进制计数器、数据选择器、和显示译码器等组成。在整个秒表中最关键的是如何获得一个精确的100HZ计时脉冲,除此之外整个秒表还需有一个启动信号,暂停信号和一个清零信号,以便秒表能随意停止及启动。

关键词:VHDL语言 数字秒表 时序仿真图

2

河北大学xxxx届本科生VHDL硬件实验论文(设计)

目 录

一、实验目的…………………………………………………………1

二、硬件要求…………………………………………………………1

三、引脚说明…………………………………………………………1

四、模块介绍…………………………………………………………2

4.1.计数器(六、十进制)…………………………………………2

4.2.蜂鸣器……………………………………………………………2

4.3.译码器……………………………………………………………3

4.4.控制器……………………………………………………………4

五、整体连接图………………………………………………………5

六、实验结果…………………………………………………………6

七、实验总结…………………………………………………………6

八、谢辞………………………………………………………………7

九、附录………………………………………………………………7

3

河北大学xxxx届本科生VHDL硬件实验论文(设计)

一 实验目的

学习使用VHDL语言,以及EDA芯片的下载仿真。

二 硬件要求

(1)主芯片EPF10K10LC84-4。 (2)蜂鸣器。

(3)8位八段扫描共阴极数码显示管。 (4)二个按键(暂停,开关)。

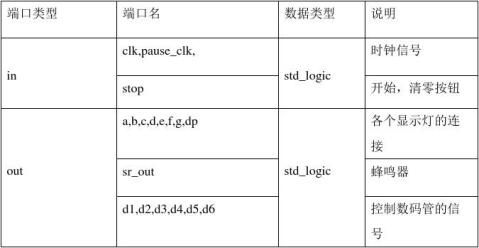

三 引脚说明

3.1引脚设置

3.2信号说明

signal q:std_logic_vector(3 downto 0); --q是用于分频的信号。

signal state: std_logic_vector(3 downto 0);

--state为状态信号,state为1时为暂停记录状态,为0时为正常显示计数状态。 signal led: std_logic_vector(3 downto 0);

--led为数码管扫描信号,通过对d1~d6的选择使数码管发光。

1

河北大学xxxx届本科生VHDL硬件实验论文(设计)

signal data,data1,data2,data3,data4,data5,data6,data7,data8:std_logic_vector(3 downto 0);

--data1~data8这些信号为计数器所记录的数值,data为传入译码器的变化值。

signal pause1,pause2,pause3,pause4,pause5,pause6:std_logic_vector(3 downto 0); --这些信号为实现暂停功能寄存信号。

signal output:std_logic_vector(6 downto 0);

--output为译码输出的信号总线。

signal sound:std_logic_vector(3 downto 0)

--sound为蜂鸣器的输入分频器。

signal sound_sout:std_logic_vector(15 downto 0);

--data1~data4的总线。

signal sound_star:std_logic;

--为蜂鸣器输入频率的开关。

四 模块介绍

时钟的设计共化分为5个模块:六进制计数电路,报时电路,扫描电路,译码电路。下面具体分析各个模块的原理、内容和功能。

4.1计数器

if(count=X)then --‘X’为进制数,为5即为6进制,为9就是10进制。

count<="0000";

next_count_clk<='1';--为下一个计数器的时钟信号输入。

else

count<=count+'1'; --实现计数功能。

next_count_clk<='0';

end if;

4.2蜂鸣器

process(data6,data5,data4,data3,data2,data1)

begin

sound_sout<=data4&data3&data2&data1; --实现整点报时的标识。

if(sound_sout=0)then

if(data5>=1)then

sound_star<='1'; --开始报时的信号

elsif(data6>=1)then

2

河北大学xxxx届本科生VHDL硬件实验论文(设计)

if(data3=5)then

sound_star<='0'; --结束报时的信号 end if;

end process;

sound_star<='1'; end if; end if; if(sound_star='1')then if(sound=1)then sr_out<='1'; else sr_out<='0'; end if; end if;

4.3译码器

process (data)

begin

case (data) is --低电平有效

when "0000" => output <= "0000001";--显示0 when "0001" => output <= "1001111";--显示1 when "0010" => output <= "0010010";--显示2 when "0011" => output <= "0000110";--显示3 when "0100" => output <= "1001100";--显示4 when "0101" => output <= "0100100";--显示5 when "0110" => output <= "0100000";--显示6 when "0111" => output <= "0001111";--显示7 when "1000" => output <= "0000000";--显示8 when "1001" => output <= "0000100";--显示9 when others => output <= "0000110"; end case;

end process;

a <= output(6);

b <= output(5);

3

河北大学xxxx届本科生VHDL硬件实验论文(设计)

c <= output(4); d <= output(3); e <= output(2); f <= output(1); g <= output(0);

4.4控制器

--输出控制器

case (led) is

when "0000" => data <=data1;--将百分秒位赋值于data。

d1<='0';d2<='1';d3<='1';d4<='1';d5<='1';d6<='1';dp<='1';--(从右到左)选择第一个数码管。

pause1<=data1;--寄存现在的数值。

when "0001" => data <=data2;--十分秒位

d1<='1';d2<='0';d3<='1';d4<='1';d5<='1';d6<='1';dp<='1';--第二个数码管 pause2<=data2;--寄存

when "0010" => data <=data3;--秒低位

d1<='1';d2<='1';d3<='0';d4<='1';d5<='1';d6<='1';dp<='0';--第三个数码管 pause3<=data3;--寄存

when "0011" => data <=data4;--秒高位

d1<='1';d2<='1';d3<='1';d4<='0';d5<='1';d6<='1';dp<='1';--第四个数码管 pause4<=data4;--寄存

when "0100" => data <=data5;--分低位

d1<='1';d2<='1';d3<='1';d4<='1';d5<='0';d6<='1';dp<='0';--第五个数码管 pause5<=data5;--寄存

when "0101" => data <=data6;--分高位

d1<='1';d2<='1';d3<='1';d4<='1';d5<='1';d6<='0';dp<='1';--第六个数码管 pause6<=data6;--寄存

when others => data <="1000";

end case;

process(pause_clk,stop) --状态控制器

begin

if(pause_clk'event and pause_clk='1')then

4

河北大学xxxx届本科生VHDL硬件实验论文(设计)

if(state="0001")then

state<="0000"; --计时显示状态 else

state<=state+1; --暂停状态 end if;

end if;

end process;

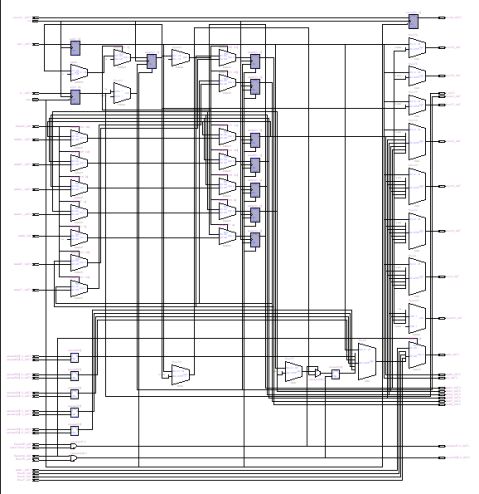

五 整体连接图

5

河北大学xxxx届本科生VHDL硬件实验论文(设计)

六 实验结果

器件上六个数码管上各自显示这一个数值,当左侧第一个开关为1时便清零停止,为0时便开始计数,从00.00.00开始,记录到59.59.99时会变为01.00.00,此时记录为时位、分位和秒位,直到23.59.59时才会自动清零,又从头开始计数。

另外该器件上还有另一个按钮,为暂停记录按钮,该按钮的作用是对正在计数显示的秒表进行数值显示上的暂停功能,再暂停之后再按这个按钮时,则是继续进行显示,其中计数功能并没有终断,只是在输出显示上暂停而已。另外,当分位为整时本秒表会进行报时蜂鸣。充分满足了老师的要求。

七 实验总结

本次VHDL课程设计历时一个学期,从开始接触到现在结束已经经历了一个学期的日子,因为很多东西都不了解,可以说是苦多于甜,但是后来我学到了很多东西,而且通过实验我还学到了很多在书本上所没有学到过的知识。这次设计,是对这一学期来所学知识的检验,也是进一步加深对VHDL的了解,我对它有浓厚的兴趣。但是在编调试程序时,也遇到了不少问题,特别是各元件之间的连接,以及各种语法,总是有错误,在细心的检查下,终于找出了错误,排除困难后,程序编译就通过了。在硬件实验时,也遇到了一点困难:想要的结果不能在数码管上得到正确的显示;在设定输入的时钟信号后,数字秒表开始计数,但是始终是乱码等。后来,经过多次调试之后,才发现是因为输入的时钟信号出了问题。经过屡次调试,终于找到了比较合适的输入脉冲,时钟周期设置在100hz秒左右比较合适。

通过这次课程设计使我懂得了理论与实际相结合是很重要的,只有理论知识是远远不够的,只有把所学的理论知识与实践相结合起来,从理论中得出结论,才能真正为社会服务,从而提高自己的实际动手能力和独立思考的能力。在设计的过程中遇到问题,可以说得是困难重重,这毕竟第一次做的,难免会遇到过各种各样的问题,同时在设计的过程中发现了自己的不足之处,对以前所学过的知识理解得不够深刻,掌握得不够牢固。

总的来说,这次设计的数字秒表还是比较成功的,虽然在实际的过程中曾经遇到了大量的问题,但是经过自己的努力,都给妥善解决了,这样的积累对于现在大学生来说是十分宝贵的。希望以后能有更多的动手实践机会,在硬件中发现自己的不足,弥补自己的不足,最终成为一个合格的大学生。最后,特别感谢老师对我的帮助。

6

河北大学xxxx届本科生VHDL硬件实验论文(设计)

附 录

-- Quartus II VHDL Template

-- Basic Shift Register

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity minute_clock is

architecture rtl of minute_clock is

signal q:std_logic_vector(3 downto 0);

signal state,led,data: std_logic_vector(3 downto 0);

signal data1,data2,data3,data4,data5,data6,data7,data8 : std_logic_vector(3 downto 0);

signal pause1,pause2,pause3,pause4,pause5,pause6,sound : std_logic_vector(3 downto 0);

signal output : std_logic_vector(6 downto 0);

signal sound_sout:std_logic_vector(15 downto 0);

signal sound_star:std_logic;

begin

process(pause_clk,stop) begin if(sound=1)then sound<="0000";

7

port ( ); clk,pause_clk,stop : in std_logic; a,b,c,d,e,f,g,dp,sr_out : out std_logic; d1,d2,d3,d4,d5,d6 : out std_logic end entity;

河北大学xxxx届本科生VHDL硬件实验论文(设计)

else sound<=sound+'1'; end if; if(pause_clk'event and pause_clk='1')then if(state="0001")then state<="0000"; state<=state+1; else end if; end if; end process; process (clk,stop) begin if(stop='1')then data1<="0000"; data2<="0000"; data3<="0000"; data4<="0000"; data5<="0000"; data6<="0000"; data7<="0000"; data8<="0000"; if(clk'event and clk='1')then if(q=6)then q<="0000"; if(data1="1001")then data1<="0000"; if(data2="1001")then

8

else data2<="0000";

河北大学xxxx届本科生VHDL硬件实验论文(设计)

if(data3="1001")then

if(data8="0010")then

data8<="0000"; data8<=data8+'1'; else end if; data7<="0000"; data8<="0000"; data7<=data7+'1';

if(data7="1001")then

data7<="0000";

if(data6="0101")then

data6<="0000";

data3<="0000"; if(data4="0101")then

data4<="0000";

if(data5="1001")then

data5<="0000";

elsif(data8="0010" and data7="0011")then

else end if;

data6<=data6+'1';

else end if;

data5<=data5+'1';

else end if;

data4<=data4+'1';

else end if;

9

河北大学xxxx届本科生VHDL硬件实验论文(设计)

else data3<=data3+'1'; end if; data2<=data2+'1'; else end if; data1<=data1+'1'; else end if; else end if; q<=q+'1'; end if; end if; end process; process(data6,data5,data4,data3,data2,data1) begin sound_sout<=data4&data3&data2&data1; if(sound_sout=0)then if(data5>=1)then sound_star<='1'; sound_star<='1'; elsif(data6>=1)then end if; end if; if(sound_star='1')then if(sound=1)then sr_out<='1'; sr_out<='0'; else end if; end if;

10

河北大学xxxx届本科生VHDL硬件实验论文(设计)

if(data3=5)then sound_star<='0'; end if; end process; process(clk) begin process(led,data7) begin if(state="0001")then case (led) is when "0000" => data when "0001" => data when "0010" => data when "0011" => data when "0100" => data when "0101" => data when others => data <="1000"; if(clk'event and clk='1')then if(led="0101")then led<="0000"; led<=led+1; else end if; end if; end process; <=pause1;d1<='0';d2<='1';d3<='1';d4<='1';d5<='1';d6<='1';dp<='1'; <=pause2;d1<='1';d2<='0';d3<='1';d4<='1';d5<='1';d6<='1';dp<='1'; <=pause3;d1<='1';d2<='1';d3<='0';d4<='1';d5<='1';d6<='1';dp<='0'; <=pause4;d1<='1';d2<='1';d3<='1';d4<='0';d5<='1';d6<='1';dp<='1'; <=pause5;d1<='1';d2<='1';d3<='1';d4<='1';d5<='0';d6<='1';dp<='0'; <=pause6;d1<='1';d2<='1';d3<='1';d4<='1';d5<='1';d6<='0';dp<='1'; end case; else

11

河北大学xxxx届本科生VHDL硬件实验论文(设计)

;

;

;

;

;

;

;

;

;

if(data7="0000" and data8<="0000")then case (led) is when "0000" => data <=data1;d1<='0';d2<='1';d3<='1';d4<='1';d5<='1';d6<='1';dp<='1';pause1<=data1 when "0001" => data <=data2;d1<='1';d2<='0';d3<='1';d4<='1';d5<='1';d6<='1';dp<='1';pause2<=data2 when "0010" => data <=data3;d1<='1';d2<='1';d3<='0';d4<='1';d5<='1';d6<='1';dp<='0';pause3<=data3 when "0011" => data <=data4;d1<='1';d2<='1';d3<='1';d4<='0';d5<='1';d6<='1';dp<='1';pause4<=data4 when "0100" => data <=data5;d1<='1';d2<='1';d3<='1';d4<='1';d5<='0';d6<='1';dp<='0';pause5<=data5 when "0101" => data <=data6;d1<='1';d2<='1';d3<='1';d4<='1';d5<='1';d6<='0';dp<='1';pause6<=data6 when others => data <="1000"; end case; case (led) is when "0000" => data else <=data3;d1<='0';d2<='1';d3<='1';d4<='1';d5<='1';d6<='1';dp<='1';pause1<=data3 when "0001" => data <=data4;d1<='1';d2<='0';d3<='1';d4<='1';d5<='1';d6<='1';dp<='1';pause2<=data4 when "0010" => data <=data5;d1<='1';d2<='1';d3<='0';d4<='1';d5<='1';d6<='1';dp<='0';pause3<=data5 when "0011" => data

<=data6;d1<='1';d2<='1';d3<='1';d4<='0';d5<='1';d6<='1';dp<='1';pause4<=data6

12

河北大学xxxx届本科生VHDL硬件实验论文(设计)

;

;

;

process (data) begin a <= output(6); b <= output(5); c <= output(4); d <= output(3); e <= output(2);

13

when "0100" => data <=data7;d1<='1';d2<='1';d3<='1';d4<='1';d5<='0';d6<='1';dp<='0';pause5<=data7 when "0101" => data <=data8;d1<='1';d2<='1';d3<='1';d4<='1';d5<='1';d6<='0';dp<='1';pause6<=data8 when others => data <="1000"; end case; end if; end if; end process; case (data) is when "0000" => output <= "0000001"; when "0001" => output <= "1001111"; when "0010" => output <= "0010010"; when "0011" => output <= "0000110"; when "0100" => output <= "1001100"; when "0101" => output <= "0100100"; when "0110" => output <= "0100000"; when "0111" => output <= "0001111"; when "1000" => output <= "0000000"; when "1001" => output <= "0000100"; when others => output <= "0000110"; end case; end process;

河北大学xxxx届本科生VHDL硬件实验论文(设计)

f <= output(1); g <= output(0); end rtl;

14

-

3d实验报告

实验报告实验报告院系信息科学与技术学院课程名称三维动画设计日期实验报告九江学院实验报告实验报告实验报告实验报告实验报告实验报告院系…

-

3D实验报告

景德镇陶瓷学院设计艺术学院实验报告课程名称计算机辅助设计三维设计姓名戈瑞琪教师董翠专业班级08陶设4班成绩日期实验项目名称1基础工…

-

3d实习报告

前言所谓三维设计就是利用电脑进行设计与创作以产生真实的立体场景与动画虽然在这个学期对3DSMAX的接触才知道3DSMAX是一个广泛…

-

unity 3d实验报告

江南大学Unity3D实验报告实验题目班级姓名学号日期一目的与要求1理解使用Unity3D制作游戏的基本过程和方法2理解Unity…

-

3D打印实验报告

姓名:学号:指导教师:20xx年x月x日一、技术介绍3D打印是一种通过材料逐层添加制造三维物体的变革性、数字化增材制造技术,它将信…

-

作风建设年活动个人总结

按照组织的分工,本人立足岗位实际,认真履行岗位职责,扎实工作,努力拼搏、务求实效,廉洁自律,时刻牢记自己是干什么的,是为谁工作,要…

-

幼儿教师远程培训总结

这个假期,我有幸参加了幼儿教师远程培训,这次网络培训学习是一次难得的学习机会,我很珍惜这次学习的机会。在这次培训中,我积极参加各种…

-

工作总结

机械20xx工作总结会议记录付红杰副主任:1、一体化教师竞赛中王翠宝、陈艳君获奖2、电气工程系一体化课演示3、技能大赛、创新大赛、…

-

大学生团员个人总结

大学生个人总结尊敬的团支部:又是一年过去了,如今的我回顾自己的学习生活,在团组织的培育下深感自己懂了不少,也学到了不少,同时也为了…

-

大学团组织生活总结

昨日辉煌今依旧——“展我素拓风采”特色团组织生活有感至此,“展我素拓风采”特色团组织生活落下了帷幕。一个月的坚持,一个的辛酸与疲惫…