实验二 组合逻辑电路分析与设计

实验二 组合逻辑电路分析与设计

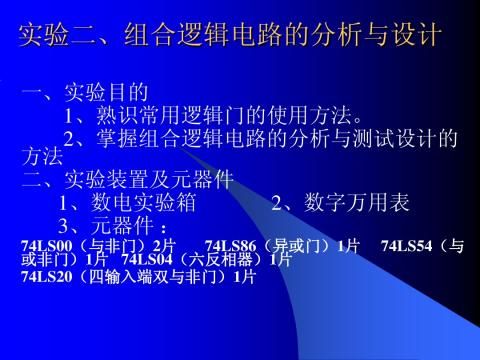

一、 实验目的

1.掌握组合逻辑电路的分析方法与测试方法;

2.掌握组合逻辑电路的设计方法。

二、实验预习要求

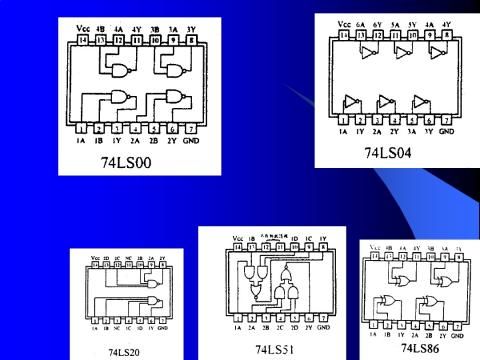

1.熟悉门电路工作原理及相应的逻辑表达式;

2.熟悉数字集成电路的引脚位置及引脚用途;

3.预习组合逻辑电路的分析与设计步骤。

三、实验原理

通常,逻辑电路可分为组合逻辑电路和时序逻辑电路两大类。电路在任何时刻,输出状态只决定于同一时刻各输入状态的组合,而与先前的状态无关的逻辑电路称为组合逻辑电路。

1.组合逻辑电路的分析过程,一般分为如下三步进行:

(1)由逻辑图写出输出端的逻辑表达式;

(2)画出真值表;

(3)根据对真值表进行分析,确定电路功能。

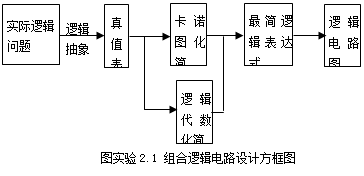

2.组合逻辑电路的一般设计过程为图实验2.1所示。

设计过程中,“最简”是指电路所用器件最少,器件的种类最少,而且器件之间的连线也最少。

四、实验仪器设备

1.TPE-AD实验箱(+5V电源,单脉冲源,连续脉冲源,逻辑电平开关,LED显示,面包板数码管等)1台;

2. 四两输入集成与非门74LS00 2片;

3. 四两输入集成异或门74LS86 1片;

4. 两四输入集成与非门74LS20 2片。

五、实验内容及方法

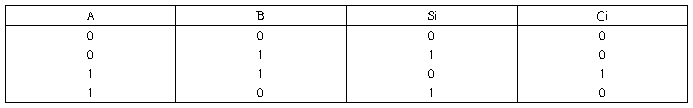

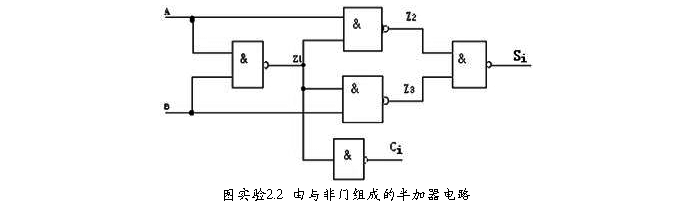

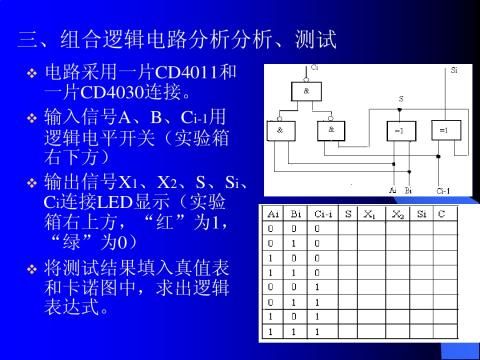

1.分析、测试74LS00组成的半加器的逻辑功能。

(1)用74LS00组成半加器,如图实验2.2所示电路,写出逻辑表达式并化简,验证逻辑关系。

(2)列出真值表。

(3)分析、测试用异或门74LS86与74LS00组成的半加器的逻辑功能,自己画出电路,将测试结果填入自拟表格中,并验证逻辑关系。

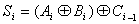

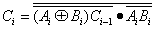

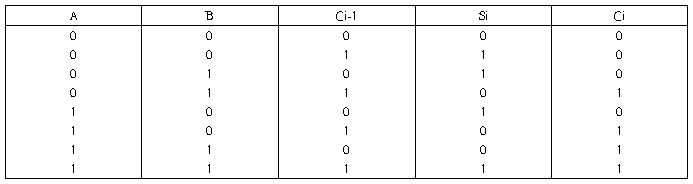

2.分析、测试全加器电路,设计用74LS86和74LS00组成全加器电路,用异或门、与门和或门组成的全加器如图实验2.3所示,将测试结果填于真值表内,验证其逻辑关系。

全加和:

进 位:

真值表如下:

逻辑电路图:

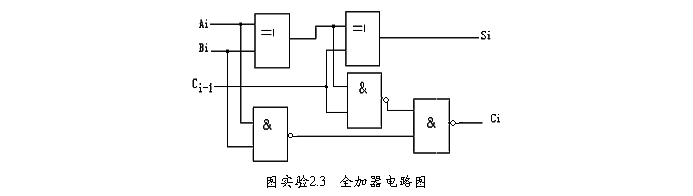

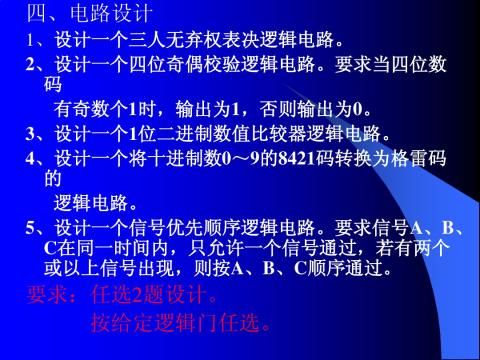

3.设计:用“与非门”设计一个表决电路。当四个输入端中有3个或4个“1”时输出为“1”

(1) 写出真值表。

表 实验2.1 真值表

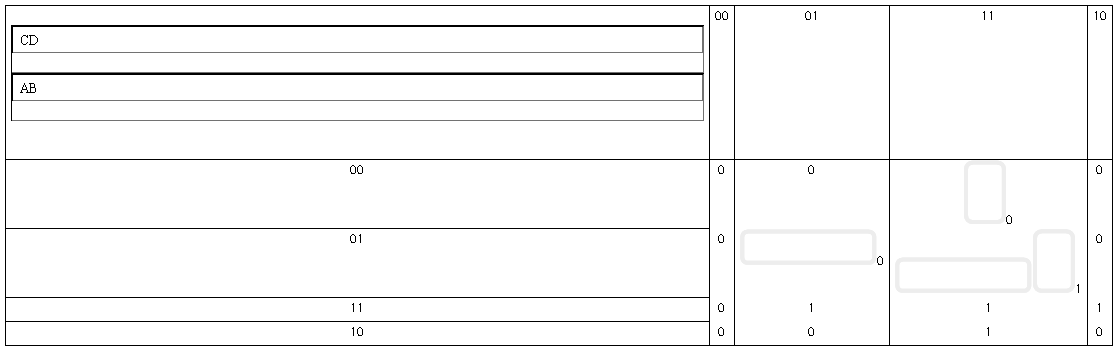

(2) 用卡诺图化简。

(3) 写出逻辑表达式,Z=ABC+BCD+ACD+ABD。

(4) 用“与非门”构成的逻辑电路图。

六、实验报告

1.整理实验数据并填表,对实验结果进行分析。

2.总结组合逻辑电路的分析与设计方法。

(1)基本分析方法

分析:给定逻辑电路→逻辑功能。

步骤:

a.给定逻辑电路→输出逻辑函数式

一般从输入端向输出端逐级写出各个门输出对其输入的逻辑表达式,从而写出整个逻辑电路的输出对输入变量的逻辑函数式。必要时,可进行化简,求出最简输出逻辑函数式。

b.列真值表

将输入变量的状态以自然二进制数顺序的各种取值组合代入输出逻辑函数式,求出相应的输出状态,并填入表中,即得真值表。

c.分析逻辑功能

通常通过分析真值表的特点来说明电路的逻辑功能。

(2),基本设计方法

设计:设计要求→逻辑图。

步骤(与分析相反):

a.分析设计要求→列真值表

根据题意设输入变量和输出函数并逻辑赋值,确定它们相互间的关系,

然后将输入变量以自然二进制数顺序的各种取值组合排列,列出真值表。

b.根据真值表→写出输出逻辑函数表达式

c.对输出逻辑函数进行化简

代数法或卡诺图法

d.根据最简输出逻辑函数式→画逻辑图。

最简与一或表达式、与非表达式、或非表达式、与或非表达式、其它表达式

第二篇:实验2:组合逻辑电路的分析设计

- 电子技术实验报告4—组合逻辑电路的设计与测试

-

实验二 组合逻辑电路分析与设计实验报告

实验二组合逻辑电路分析与设计实验报告姓名李凌峰班级13级电子1班学号13348060一实验数据与相应原理图1复习组合逻辑电路的分析…

-

组合逻辑电路的设计实验报告

广西大学实验报告纸实验内容指导老师实验名称组合逻辑电路的设计实验目的学习组合逻辑电路的设计与测试方法设计任务用四二输入与非门设计一…

-

实验十五 组合逻辑电路的分析和设计

实验十五组合逻辑电路的分析和设计一实验目的1234掌握基本逻辑门电路进行组合逻辑电路的设计方法掌握用中规模集成电路设计组合逻辑电路…

-

组合逻辑电路实验报告

实验报告课程名称:数字电子技术基础实验指导老师:樊**成绩:实验名称:组合逻辑电路实验实验类型:设计类同组学生姓名:一、实验目的和…

-

实验1 门电路功能测试及组合逻辑电路设计

实验1门电路功能测试及组合逻辑电路设计1实验目的1掌握常用门电路的逻辑功能及测试方法2掌握用小规模集成电路设计组合逻辑电路的方法2…

-

实验二 组合逻辑电路分析与设计

信息工程学院数字逻辑与数字系统实验实习报告学院信息工程学院班级信息111姓名朱伟定学号20xx013259成绩实验二组合逻辑电路分…

-

实验二 组合逻辑电路分析与设计.

实验一实验目的组合逻辑电路分析与设计1掌握组合逻辑电路的分析方法与测试方法2掌握组合逻辑电路的设计方法二实验预习要求1熟悉门电路工…

- 电子技术实验报告4—组合逻辑电路的设计与测试

-

组合逻辑电路的分析与设计-实验报告

组合逻辑电路的分析与设计实验报告院系电子与信息工程学院班级电信132班组员姓名盖兵134xxxxxxxx邢帅成134xxxxxxx…

-

组合逻辑电路实验报告

实验报告课程名称:数字电子技术基础实验指导老师:樊**成绩:实验名称:组合逻辑电路实验实验类型:设计类同组学生姓名:一、实验目的和…