实验十五 组合逻辑电路的分析和设计

实验十五 组合逻辑电路的分析和设计

一、实验目的:

1. 掌握基本逻辑门电路进行组合逻辑电路的设计方法;

2. 掌握用中规模集成电路设计组合逻辑电路的方法;

3. 通过实验,论证设计的正确性;

4. 观察组合电路中的竞争冒险现象;

二、实验原理:

1. 组合逻辑电路的分析:

所谓组合逻辑电路分析,即通过分析电路,说明电路的逻辑功能。

通常采用的分析方法是从电路的输入到输出,根据逻辑符号的功能逐级写出逻辑函数表达式,最后得到表示输出与输入之间的关系的逻辑函数式。然后利用公式化简法或卡诺图化简法得到函数化简或变换,以使逻辑关系简单明了。为了使电路的逻辑功能更加直观,有时还可以把逻辑函数式转换为真值表的形式。

2. 组合逻辑电路的设计:

根据给出的实际逻辑问题,求出实现这一逻辑功能的最简单逻辑电路,称为组合逻辑电路的设计。通常分为SSI设计和MSI设计。

(1)SSI设计:SSI设计通常采用如下步骤:

逻辑抽象:分析事件的因果关系,确定输入和输出变量。一般把引起事件的原因定为输入变量,而把事件的结果作为输出变量。

1.定义逻辑状态的含义:以二值逻辑的0、1两种状态分别代表输入变量和输出变量的两种不同状态。

2.根据给定的因果关系列出逻辑真值表。

3.写出逻辑表达式,利用化简的方法进行化简,并根据选定器件进行适当转换;

4.根据化简、变换后的逻辑表达式,画出逻辑电路的连接图;

5.实验仿真,验证结果。

(2)MSI设计:MSI设计通常采用如下步骤:

1.2 .3步骤同SSI设计步骤:

4.写出逻辑表达式;

5.根据表达式查找合适的MSI器件;

6.通过比较表达式或真值表,利用适当的设计实现所需功能;

7.画出逻辑电路的连接图;

8.实验仿真,结果验证。

三.实验仪器:

1.多功能电路实验箱 1台

2.数字万用表 1台

四.实验内容:

1.联锁器电路分析并用中规模集成电路(MSI)设计实现其功能:

所谓联锁器即为电子锁电路如图1所示,其输入为S1、S2、S2开关,报警和解锁输出分别为F1、F2。其中S1、S2、S3为单刀双掷开关,根据拨动可分别置“1”或“0”。当F1=“1”,表示不报警,否则报警。当F2=“1”,表示解锁,否则安锁。现要求:

(1)当联锁器处于始态(S1=S2=S3=“1”),则L5=“1”、L6=“0”即:安锁且不报警。

(2)试利用所学知识分析电路,找出解锁并不报警的开关拨动顺序:

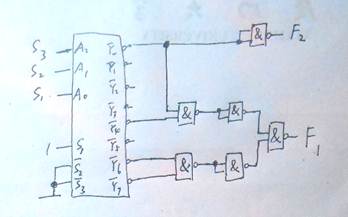

(3)试用74LS138设计代替该电路;

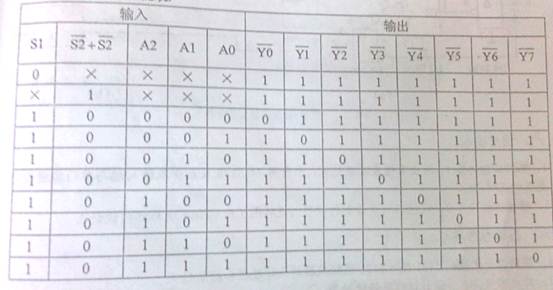

74LS138(三线~八线译码器):其惯用符号及管脚如图2所示,表2为其功能表:

74LS138功能表:

2.码制转换器[用基本逻辑门电路设计]:

(1)设计一个5421BCD码~8421BCD码转换器

1. 写出原函数的最简与或表达式;

2. 写出用与非门实现的最简逻辑表达式;

3. 写出用双输入与或门组成的逻辑图;

(2)用7400双输入端四与非门搭接电路:

用逻辑开关S4~S1作5421bcd码的DCBA(或D~C~B~A~)的输入,将8421BCD码的输出dcba接实验箱的二~十进制译码显示器Y8Y4Y2Y1(或接发光二极管L8L7L6L5)。按表1顺序输入5421码,观察数码转换的结果。验证所涉及电路的正确性。

3.组合逻辑电路的竞争冒险

当逻辑门店了处于实际的复杂数字系统中时,若信号电达门店了输入端时,由于在涉及时难于准确知道信号到达顺序的先后,以及它们在上升时间和下降时间上的细微差异。因此,当门电路的两个输入信号同时向相反的逻辑电平跳变时,称此电路存在竞争现象,而由于电路存在竞争时,输出端可能产生出现违背稳态下逻辑关系的尖峰脉冲的现象称为竞争——冒险现象。

按图2(a)所示,用7400和7476搭接电路,信号源用TTL方波作A端输入信号,f>1MHz,用示波器观察并记录A,Q,Y端的工作波形。并与图2(b)的理想波形进行比较,注意观察竞争—冒险现象。若在Q端接上一个几百PF的电容,则竞争—冒险现象更加明显。

五.预习要求:

1、根据实验内容1,写出真值表及表达式,画出用74LS138及最少双输入端与非门实现设计要求的逻辑图:

2、根据实验内容2,设计二~十进制转换器的逻辑图(用双输入端与非门设计)。

六.实验报告要求:

1、写出二~十进制5421码~8421码转换器的设计过程和检测结果。

2、写出预习要求2设计过程及检验结果。

设计1:

F1=S1’S2’+S1’S2’+S2S3;

F2=S1’S2’S3’;

A0,A1,A2分别对应S1,S2,S3;图如下:

设计2:

d=D;

c=D’C;

b=D’B;

a=D’A+DC=[(D’A)’(DC)’]’;

设计图如下:

3、说明组合逻辑电路中竞争—冒险产生原因及消除措施。

组合逻辑电路中竞争—冒险产生原因:

对于同一个门电路来说,当有两个输入信号同时向两个相反的逻辑状态变化时,由于两个输入信号到达开门、关门电平的时间不同,就有可能在电路的输出端产生干扰脉冲$可见,门电路存在平均延迟时间是组合逻辑电路产生竞争冒险现象的根本原因。

消除措施:

1、修改逻辑设计

(1)消除互补变量;

(2)增加冗余项;

2、加封锁脉冲信号:

如果在门电路的输入端加一封锁脉冲,要求封锁脉冲与输入信号的状态转换同步,且封锁脉冲的宽度大于或等于电路从一个稳定状态到另一个稳定所需要的时间"那么,在信号状态转换的时间内,将可能产生尖峰脉冲输出的门封锁,电路的输出就不会出现竞争冒险现象。

3、引入取样脉冲:

在电路的输入端引入一个取样脉冲,由于取样脉冲的作用时间取在电路达到新的稳定状态之后,使电路的输出端不会出现尖峰脉冲。

第二篇:实验二组合逻辑电路分析与设计

一.实验目的

1.掌握小规模(SSI)组合逻辑电路的分析与设计方法。

2.熟悉常用中规模(MSI)组合逻辑部件的功能及其应用。

*3.观察组合电路的竞争-冒险现象,了解消除冒险现象的方法。

二.实验设备与器件

双踪示波器:DS1062C 函数信号发生器:SG1651

数字实验箱:THD-4 数字万用表:MS8222D

实验器件: 74LS00、74LS02、74LS20、74LS54、74LS83、

74LS86、74LS138、74LS151

三.实验内容

(一) 组合逻辑电路的分析

1.分析图16-1所示“一位数值比较器”电路的逻辑功能,说明其逻辑关系与实际意义,并将验证测试结果填入表16-1。

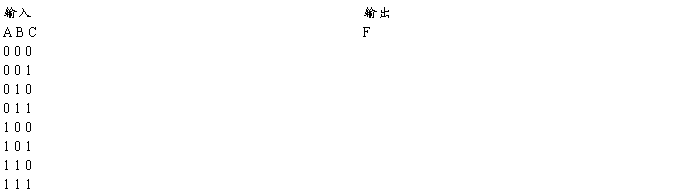

表16-1

*2.分析图16-2所示“四位二进制原码/反码转换”电路的逻辑功能,按照表16-2选取其中一位作出分析,并记录测试结果。

表16-2

表16-2

3.分析图16-3采用MSI芯片(3-8译码器)构成的组合逻辑电路,正确连接各引脚并供电,然后测试电路功能,结果填入表16-3。

表16-3

表16-3

注:当  、

、  时,译码器输入输出逻辑关系为:

时,译码器输入输出逻辑关系为:

m i 系 A 2 A 1 A 0 的最小项(参见附录Ⅳ中 74LS138真值表)。

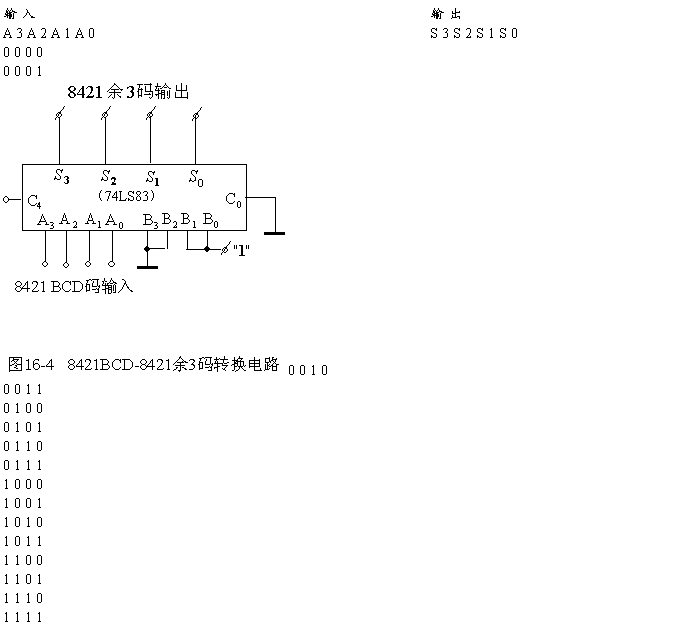

*4.分析图16-4“8421BCD码-8421余3码转换电路”的逻辑功能,将测试结果填入表16-4。

注: 74LS83资料见附录Ⅳ。

表16-4

(二) 组合逻辑电路的设计与测试

1.逻辑函数为:  ,试用一片74LS54(四组输入与或非门)设计其组合逻辑电路。并将测试结果列表记录。

,试用一片74LS54(四组输入与或非门)设计其组合逻辑电路。并将测试结果列表记录。

注:测试中,应考虑TTL门多余输入端的处理。

2.用最少的异或门(74LS86)设计一个“三位二进制码的奇校验器”:当三位数码中出现奇数个“1”时,输出为“1”,否则输出为“0”。

*3.试用最少的异或门和与非门设计一个反映泵房水泵工作情况的控制电路,要求:三台水泵中若有一台水泵出现故障时,黄灯亮;二台水泵故障时,红灯亮;并三台水泵同时发生故障的情况不出现。

4.设计一个电机启动逻辑控制器:A、B、C三个开关符合如下条件时电机启动:A与B闭合,或A与C闭合,或A、B、C同时闭合;否则电机不启动。

阅读教材及 附录 中数据选择器有关内容,用 MSI芯片74LS151(8选1数据选择器)设计该控制器,并将验证测试结果列表记录。

注: 74LS151选通端  时,输出

时,输出  。

。

其中 m i 系A 2 A 1 A 0 地址码的最小项。

四.预习要求

1.复习教材中组合逻辑电路的分析与设计方法。

2.了解实验中所用SSI/MSI芯片引脚的功能与使用方法。

3.设计实验电路及记录表格。

4.简答思考题。

五.实验报告

1.写出有关实验内容的设计过程,注明变量条件。

2.记录各项实验测试数据与波形,并加以分析。

3.简答思考题。

六.思考题

1.与门、与非门多余输入端应如何处理?

2.或门、或非门的多余输入应如何处理?

3.比较用SSI门电路和用MSI部件进行组合逻辑电路设计时,各有何优缺点?

- 电子技术实验报告4—组合逻辑电路的设计与测试

-

实验二 组合逻辑电路分析与设计实验报告

实验二组合逻辑电路分析与设计实验报告姓名李凌峰班级13级电子1班学号13348060一实验数据与相应原理图1复习组合逻辑电路的分析…

-

组合逻辑电路的设计实验报告

广西大学实验报告纸实验内容指导老师实验名称组合逻辑电路的设计实验目的学习组合逻辑电路的设计与测试方法设计任务用四二输入与非门设计一…

-

实验十五 组合逻辑电路的分析和设计

实验十五组合逻辑电路的分析和设计一实验目的1234掌握基本逻辑门电路进行组合逻辑电路的设计方法掌握用中规模集成电路设计组合逻辑电路…

-

组合逻辑电路实验报告

实验报告课程名称:数字电子技术基础实验指导老师:樊**成绩:实验名称:组合逻辑电路实验实验类型:设计类同组学生姓名:一、实验目的和…

-

组合逻辑电路实验报告

实验报告课程名称:数字电子技术基础实验指导老师:樊**成绩:实验名称:组合逻辑电路实验实验类型:设计类同组学生姓名:一、实验目的和…

-

实验二 组合逻辑电路分析与设计.

实验一实验目的组合逻辑电路分析与设计1掌握组合逻辑电路的分析方法与测试方法2掌握组合逻辑电路的设计方法二实验预习要求1熟悉门电路工…

- 电子技术实验报告4—组合逻辑电路的设计与测试

-

数字实验二 组合逻辑电路的分析及设计

实验二组合逻辑电路的分析与设计一实验目的1掌握组合逻辑电路的分析与设计方法2加深对基本门电路使用的理解二实验设备与器件1数字逻辑实…

-

组合逻辑电路的分析与设计-实验报告

组合逻辑电路的分析与设计实验报告院系电子与信息工程学院班级电信132班组员姓名盖兵134xxxxxxxx邢帅成134xxxxxxx…

-

实验二 组合逻辑电路分析与设计

信息工程学院数字逻辑与数字系统实验实习报告学院信息工程学院班级信息111姓名朱伟定学号20xx013259成绩实验二组合逻辑电路分…