计算机组成原理实验报告

昆明理工大学信息工程与自动化学院学生实验报告

( 2011 —2012 学年第二学期)

课程名称:计算机组成原理 (含数字逻辑)

开课实验室:信自楼504 2012 年 4月 12 日

目 录

实验一:LED显示……………………………………………………..2 页

实验二:运算器…………………….………………………. …………4 页

实验三:存储器……………………………………………………… ..9 页

实验四:总线传输…………………….….……………………………13页

实验一:LED显示

一、实验目的

1.了解数据输出输入

2.理解数码显示译码器的作用

3.掌握七段数码显示译码器的设计

4了解可编程外围接口芯片8255

5.学会使用8255芯片

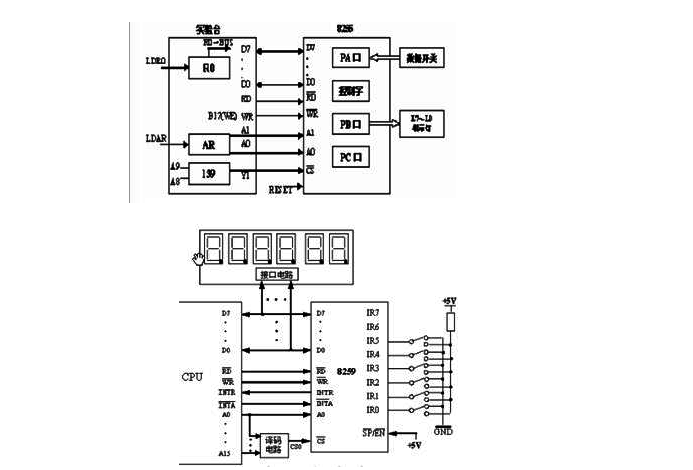

二、实验原理及基本技术路线图(方框原理图)

三、所用仪器、材料(设备名称、型号、规格等)

TDN-CM+或TDN-CM++教学实验系统一台。

四、实验方法、步骤

(1)按实验原理电路图连接好电路,确认无误后打开电源。

(2)打开数据开关三态门(SW-B=0),在输入部分单元中输入对应的二进制数据,打开LED片选(LED-B=0),拨动LED的W/R控制信号做1→0→1动作,产生一个上升沿将总线上的数据打入到LED中,这时在output device单元中数码管上显示的数据即为相应的十六进制形式。

五、实验过程原始记录(数据、图表、计算等)

在输入单元输入二进制数据11110001,然后打开数据开关三态门(SW-B=0),打开LED片选(LED-B=0),拨动LED的W/R控制信号做1→0→1动作,产生一个上升沿,这时数码管上会显示对应的十进制数,即F1。

六、实验结果、分析和结论

在本次实验中,开始的时候由于对实验的机器不是很了解,在连线、机器掌握方面出现了很多错误,但是在老师同学的帮助下,纠正了自己的错误,顺利的完成了此次实验。

通过本次实验,我对整个机器有了一定的了解与认知,对以后的组成原理实验有了奠定了一定的基础,对以后的计算机组成原理学习也有了很大的帮助。

实验二:运算器

一、实验目的

(1)了解运算器的组成结构。

(2)掌握运算器的工作原理。

(3)学习运算器的设计方法。

(4)掌握简单运算器的数据传输通路。

(5)验证运算功能发生器74LS181的组合功能。

二、实验原理及基本技术路线图(方框原理图)

实验中所用到的运算器数据通路图如图,图中所示的是由两片74LS181新片以并串形式构成的8位字长的运算器。右方为低四位运算芯片,左方为高4位运算芯片。低位芯片的进位输出端C(n+4)与高位芯片的进位输入端Cn相连,高位芯片的进位输出引至外部。两个芯片的控制端SO—S3和M各自相连。

为进行双操作数运算,运算器的两个数据输入端分别由两个数据暂存器DR1,DR2来所存数据。要将内总线上的数据所存到DR1或DR2中,则锁存器74LS273的控制端LDDR1或LDDR2需为高电平。当T4脉冲到来时,总线上的数据就被锁存进DR1或DR2中了。

为控制运算器向内总线上输出运算结果,在其输出端连接了一个三态门。若要将运算结果输出到总线上,则要将三态门74LS245的控制端ALU—B置低电平。否则输出高阻态。

数据输入单元用以给出参与运算的数据,其中,输入开关经过一个三态门和内总线相连,该三态门的控制信号SW-B取低电平时,开关上的数据就通过三态门而送入总线上。

总线数据显示灯与美总线相连,用来显示内总线上的数据。控制信号中除T4为脉冲信号外,其他均为电平信号。

由于实验电路中的时序信号均已连至W/R NUIT单元中的相对应时序信号引出端,因此,需要将单元中的T4接至START NUIT 单元中的微动开关KK2的输出端。在进行实验时,按动微动开关,即可获得实验所需的单脉冲。

对于单总线数据通路,做实验时就要分时控制总线,即当向DR1、DR2工作暂存器打入数据时,数据开关三态门打开,这时应保证运算器输出三态门关闭,同样,当运算器输出结果至总线时也应保证数据输入三态门是关闭状态。

三、所用仪器、材料(设备名称、型号、规格等)

TDN-CM+或TDN-CM++教学实验系统一套

四、实验方法、步骤

(1)按图所示连接实验电路并检查无误。

(2)打开电源开关。

(3)用输入开关项暂存器DR1置数。

1)拨动输入开关形成二进制数01100101。(数据显示:灯亮为0,灭为1)

2)使SWITCH NUIT 单元中的开关SW-B=0、ALU-B=1、LDDR1=1、LDDR2=0。

3)按动微动开关KK2,则将二进制数01100101置入DR1中。

(4)用输入开关向暂存器DR2置数。

1)拨动数输入开关形成二进制数10100111

2)SW-B=0、ALU-B=1保持不变,改变LDDR1、LDDR2、使LDDR1=0、LDDR2=1。

3)拨动微动开关KK2,则将二进制数10100111置入DR2中。

(5)检验DR1和DR2中的数是否正确。

1)关闭数据输入三态门,打开ALU 输出三态门,并使LDDR1=0、LDDR2=0,关闭寄存器。

2)置S3、S2、S1、S0、M为1、1、1、1、1,总线显示灯显示DR1 中的数。

3)置S3、S2、S1、S0、M 为1、0、1、0、1,总线显示灯显示DR2中的数。

(6)改变运算器的功能设置,观察运算器的输出。

1)SW-B=1、ALU-B=0保持不变。

2)按表置S3、S2、S1、S0、M、CN的数,并观察总线显示灯显示的结果。

例如:

置S3、S2、S1、S0、M、CN为1、0、0、1、0、1,运算器进行加法运算。

置S3、S2、S1、S0、M、CN为0、1、1、0、0、0,运算器进行减法运算。

(7)验证74LS181的算术运算和逻辑运算功能。

五、实验过程原始记录(数据、图表、计算等)

六、实验结果、分析和结论

运算器可以实现加、减、乘、除四则运算,还可以实现与、或、非、异或等逻辑操作,以及移位、求补等操作,运算器处理的数据来自存储器,处理后的结果数据通常送回存储器,或者暂时存在运算器中。

根据输入的指令,我们可以从设备上读出静态随即存储器RAM中我们已有的数据,且可以看书有如与读出数据是否相同。

通过本次试验我懂得了用进位控制运算器进行简单的算术运算,掌握了进位控制运算器的工作特性及使用方法。由于在对逻辑运算器实验的时间的把握不是很好和对实验的仪器的不熟悉,从而导致进位控制运算器的实验要在很短的时间内完成,虽然时间仓促,经过努力还是进本完成了实验的要求。

注意事项:

(1)在存入数据时,必须先写入数据,形成一一对应,避免数据错误出现。

(2)写地址完成后,在写入数据时再关闭LDAR,因为LDAR是地址寄存器的存数控制信号;

(3)在连接线路后,要查看是否将连线的孔差错或插孔的错位。

实验三:存储器

一、 实验目的

掌握静态随机存储器RAM工作特性及数据的读/写方法。

二、实验原理及基本技术路线图(方框原理图)

(1)TND-CM+或TND-CM++ 教学实验系统一台。

(2)PC机(或示波器)一台。

三、所用仪器、材料(设备名称、型号、规格等)

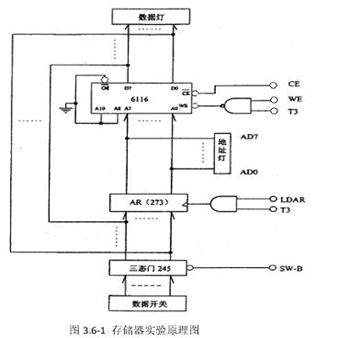

实验所用的半导体静态存储电路原理如图3.6-1所示,实验中的静态存储器由一片6116(2k×8)芯片构成,其数据线接之数据总线,地址线由地质锁存器(74LS273)给出。地址灯AD0~AD7与地址线相接,显示地址线状况。数据开关经一个三态门(74LS273)连至数据总线,分时给出地址和数据。

因为地址寄存器为8位,所以接入6116芯片的地址为A7~A0,而高3位A8~A10接地,所以其实际容量只有256字节。6116芯片有三个控制线:CE(片选线)、OE(读线)、WE(写线)。当片选有效(CE=0)、OE=0时进行读写操作,WE=0时进行写操作,CE=0、WE=1时进行写操作,其写时间与T3脉冲的宽度一致。

实验时将T3脉冲接至实验板上时序电路模块的TS3相应插孔中,其脉冲宽度可调,其他电平控制信号由“SWITCH UNIT”单元的二进制开关模拟,其中SW-B为低电平有效,LDAR为高电平有效。

实验时将T3脉冲接至实验板上时序电路模块的TS3相应插孔中,其脉冲宽度可调,其他电平控制信号由“SWITCH UNIT”单元的二进制开关模拟,其中SW-B为低电平有效,LDAR为高电平有效。

四、实验方法、步骤

(1)形成时钟脉冲信号T3。具体接线方法和操作步骤如下:

?接通电源,用示波器接到方波信号源的输出插孔H23调节电位器W1及W2,使H23端输出实验所期望的频率和占空比的方波。

?将时序电路模块(STATE UNIT)单元中的F和信号单元(SIGNAL UNIT)中的H23排针相连。

?在时序电路模块中有两个二进制开关“STOP”和“STEP”,将“STOP”开关置为“RUN”状态,“STEP”开关置为“EXEC”状态时,按动微开关START,则TS3端输出连续的方波信号,此时调节电位器W1,用示波器观察,使T3输出实验要求的脉冲信号。当“STOP”开关置为“RUN”状态时,每按动一次微开关START,则T3输出一个单脉冲,其脉冲宽度与连续方式相同。用PC联机软件中的示波器功能也能看到波形。这样可以代替真实示波器。

(2)按图3.6-2连接实验线路,仔细查线无误后接通电源。

(3)写存储器。给存储器的00、01、02、03、04地址单元中分别写入数据11H、12H、13H、14H、15H。

由上面的存储实验原理图(图3.6-2)看出,由于数据和地址全由一个数据开关给出,因此要分时的给出。下面的写存储器要分两个步骤:第一步写入地址,先关掉存储器的片选(CE=1),打开地址锁存器门控信号(LDAR=0),打开数据开关三态门(SW-B=0),由开关给出要写入的存储单元地址,按动START产生T3脉冲将地址打入到地址锁存器;第二步写数据,关掉地址锁存器门控信号(LDAR=0),打开存储器片选,使之处于写状态(CE=0,WE=1),由开关给出此单元要写入的数据,按动START产生T3脉冲将数据写入到当前的地址单元中,写其他单元依次循环上述步骤。

写存储器流程如图3.6-3所示(以向00号单元写入11H为例)。

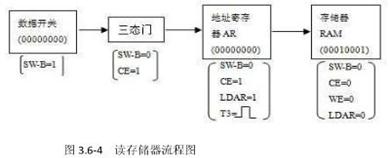

(4)读存储器。

依次读出第00、01、02、03、04号单元中的内容,观察上述各单元中的内容是否与前面写入的一致。同写操作类似,读每个单元也需要两步:第一步写地址,先关掉存储器的片选(CE=1),打开地址锁存器门控制信号(LDAR=1),打开数据开关三态门(SW-B=0),由开关给出要写存储单元的地址,按动START产生T3脉冲将地址打入到地址锁存器;第二步读存储器,关掉地址锁存器门控信号(LDAR=0),关掉数据开关三态门(SW-B=1),片选存储器,使它处于读状态(CE=0、WE=0),此时数据总线上显示的数据即为从存储器当前地址中读出的数据内容。读其他单元依次循环上述步骤。

读存储器操作流程如下图3.6-4所示(以从00号单元读出11H数据为例)。

读存储器操作流程如下图3.6-4所示(以从00号单元读出11H数据为例)。

五、实验过程原始记录(数据、图表、计算等)

写入第一个一个地址时,在输入单元给出二进制地址00000000,打开地址锁存器,便可把地址打入地址锁存器,地址灯显示为00000000,然后输入该单元存入的数据00010001(11H),总线数据显示灯应显示为00010001,打开存储器片选,使之处于写操作,这样11H便存入00号单元,依此类推,可将12H、13H、14H、15H分别存入01、02、03、04地址单元,地址灯和总线数据显示灯都分别显示出结果。读存储器时,当用开关给出存储单元地址时,地址灯会显示,这时,打开存储器片选,使之处于读状态,此时数据总线上显示的数据即为从存储器当前地址中读出的数据内容。

六、实验结果、分析和结论

存储中最小的存储单位就是一个双稳态的半导体电路或一个CMOS晶体管或磁性材料的存储元,它可存储一个二进制代码。由若干个存储元组成一个存储单元,然后再由许多存储单元组成一个存储器。一个存储器包括许多存储单元,每个存储单元可存放一个字节,每个存储单元的位置都有一个编号,即地址,一般用十六进制表示。一个存储器中所有单元可存放数据的总和称为它的存储容量,给出地址指令,就可以讲数据存入指定的地质单元。

实验四:总线传输

一、 实验目的

(1)理解总线的概念及其特性

(2)掌握总线传输控制特性

二、实验原理及基本技术路线图(方框原理图)

总线传输框如图5.4-1所示,他将几种不同的设备挂至总线上,有存储器、输入设备、输出设备、寄存器。这些设备都需要三态输出控制,按照传输要求恰当有序的控制它们,就可实现总线信息传输。

基本实验要求如下:

根据挂起在总线上的几个基本条件,设计一个简单的流程;

1) 输入设备将一个数打入R0寄存器。

2) 输入设备将另一个数打入地址寄存器。

3) 将R0寄存器中的数写入带当前的地址的寄存器中。

4) 将当前地址的寄存器中的数用LE数码管显示。

三、所用仪器、材料(设备名称、型号、规格等)

TDN-CM+或TDN-CM++教学实验系统一台

四、实验方法、步骤

1) 按照图5.4-2试验接线图进行连线。

(2)实验的具体操作步骤图如图5.4-3所示。

首先应关闭所有三态门(SW-B=1,R0-B=1,LED-B=1),并将关联的信号置为LDAR=0,LDR0=0,W/R(LED)=1,W/R(LED)=1.然后参照如下操作流程,先将数据开关打入到R0中;然后继续给开关置数,拨动LDR0控制信号做0→1→0动作,产生一个上升沿将数据打入到R0中;然后继续给数据开关置数,拨动LDAR控制信号做0→1→0动作产生一个上升沿将数据打入到AR中;关闭数据开关三态门,打开R0寄存器输出控制,使寄存器输出,使寄存器处于写状态(W/R=0,CS=0),将R0中的数写到存储器中;关闭存储器片选,关闭R0寄存器输出,使存储器处于读状态(W/R=1,CS=0),打开LED片选,拨动LED的W/R控制信号1→0→1动作,产生一个上升沿将数据打入到LED中。

五、实验过程原始记录(数据、图表、计算等)

打开输出三态门,在输入单元由开关给出要保存的数据00110111(37H),拨动控制信号LDR0,可将数据打入到寄存器R0中,继续给数据开关置数,这时给出地址00000010(02H),拨动LDAR控制信号,变将数据打入了地址寄存器AR中,之后打开R0的输出开关,将寄存器中的数据写入到02单元的存储器中,使存储器处于读状态,已读出该存储器中的数据,打开LED片选,拨动W/R信号,这时数码显示管上会显示出37,即输入到存储器02单元保持的数据,

六、实验结果、分析和结论

总线是CPU、内存、输入、输出设备传递信息的公用通道,主机的各个部件通过总线相连接,外部设备通过相应的接口电路再与总线相连接,从而形成了计算机硬件系统,总线包含三个基本结构:地址总线、数据总线、控制总线。传输数据的过程是先寻址,再传输数据。即先送一个地址信息,由寄存器根据这个地址,把微处理器读取的数据写到总线上,微处理器再读取这个数据。整个过程由控制总线控制。写数据时也是一样,先寻址,再写数据,数据就写入刚才寻址时的地址对应的那个寄存器里了。当总线空闲且一个器件要与目的器件通信时,发起通信的器件驱动总线,发出地址和数据。其他以高阻态形式连接在总线的器件如果收到与自己相符的地址信息后,即接受总线上的数据。发送器件完成通信,将总线让出。采用总结构不仅简化了硬件的设计、简化了系统结构,还使系统扩充性、更新性更好。

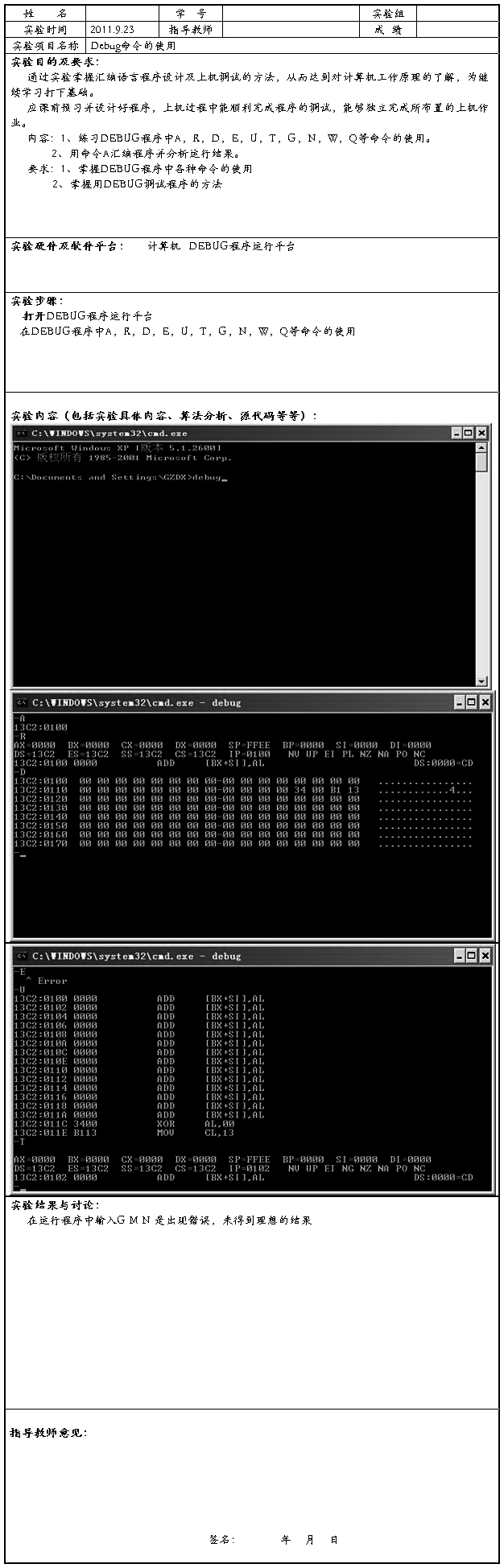

第二篇:计算机组成原理实验报告一

实 验 报 告

实验课程名称 计算机组成原理

实验项目名称 DEBUG命令的使用

年 级

专 业

学生姓名

学 号

实验时间: 2011 年 9 月 23 日

学生所在学院: 专业: 班级:

-

计算机组成原理实验报告

计算机组成原理实验报告软件学院计算机组成原理实验报告专业班级学号日期学生姓名指导教师计算机组成原理实验报告运算器组成实验一实验目的…

-

计算机组成原理 电子科大技大学 实验报告

课程名称计算机组成原理学院计算机科学与工程专业计算机科学与技术指导教师王学生姓名郭学号实验成绩日期实验报告勇小明20xx06010…

- 计算机组成原理实验报告-存储器

-

计算机组成原理实验报告1

计算机组成原理实验报告1姓名学号教师时间地点机位实验名称数据传送实验一实验目的1理解自然语言形式命令的人工译码过程2学习系统部件和…

-

《计算机组成原理》运算器实验报告

《计算机组成原理》实验报告学院:专业:班级学号:AP0804114学生姓名:实验日期:指导老师:成绩评定:五邑大学信息学院计算机组…

-

农林大学计算机组成原理课程实习报告模板(新)

福建农林大学金山学院课程名称实习题目姓名系专业年级学号指导教师职称课程实习报告计算机组成原理普通的加减法指令柳继曾机电与信息工程系…

- 计算机组成原理实验报告 存储器

-

存储器试验 《计算机组成原理》实验报告

计算机组成原理实验报告计算机组成原理实验报告正文用纸页数可随意扩充标题使用黑体不加粗字号小二段前段后为自动行间距15倍正文中文使用…

-

存储器和IO扩展实验,计算机组成原理

科技学院课程设计实验报告20xx20xx年度第一学期名称计算机组成原理综合实验题目院系信息工程系班级学号学生姓名指导教师李梅王晓霞…

- 计算机组成原理实验报告-存储器

-

《计算机组成原理》运算器实验报告

《计算机组成原理》实验报告学院:专业:班级学号:AP0804114学生姓名:实验日期:指导老师:成绩评定:五邑大学信息学院计算机组…