Proteus与cadence实训(高频正弦波振荡器)

课程设计任务书

学生姓名: 专业班级: 电子1001班

指导教师: 韩屏 工作单位: 信息工程学院

题 目: 高频晶体正弦波振荡器

初始条件:

计算机、Proteus软件、Cadence软件

要求完成的主要任务: (包括课程设计工作量及其技术要求,以及说明书撰写等具体要求)

1、课程设计工作量:2周

2、技术要求:

(1)学习Proteus软件和Cadence软件。

(2)设计一个高频晶体正弦波振荡器电路。

(3)利用Cadence软件对该电路设计原理图并进行PCB制版,用Proteus软件对该电路进行仿真。

3、查阅至少5篇参考文献。按《武汉理工大学课程设计工作规范》要求撰写设计报告书。全文用A4纸打印,图纸应符合绘图规范。

时间安排:

2013.11.11做课设具体实施安排和课设报告格式要求说明。

2013.11.11-11.16学习Proteus软件和Cadence软件,查阅相关资料,复习所设计内容的基本理论知识。

2013.11.17-11.21对高频晶体正弦波振荡器电路进行设计仿真工作,完成课设报告的撰写。

2013.11.22 提交课程设计报告,进行答辩。

指导教师签名: 年 月 日

系主任(或责任教师)签名: 年 月 日

目录

目录... 1

摘要... 2

一、工作原理说明... 3

1.1、振荡器概念... 3

1.2、 静态工作点的确定... 3

1.3、振荡器的起振检查... 4

二、电路设计... 5

2.1、正弦波振荡器的设计... 5

2.2、电路功能的仿真... 7

2.3、Cadence部分原理图设计... 9

三、PCB版图设计... 15

四、心得体会... 18

五、参考文献... 19

摘要:

本次课程设计通过对课本知识的运用,简单介绍了高频正弦波振荡器的设计方法,主要应用LC电容三点式振荡电路产生正弦波。电路应用Candence软件进行的原理图设计及PCB设计,使用Proteus软件进行电路功能仿真,经过反复的调试最终得到满足课题要求的电路。

关键词:正弦波;振荡器;高频功率放大器。

一、工作原理说明

1.1、振荡器概念

振荡器主要分为RC,LC振荡器和晶体振荡器。其中电容器和电感器组成的LC回路,通过电场能和磁场能的相互转换产程自由振荡。要维持振荡还要有具有正反馈的放大电路,LC振荡器又分为变压器耦合式和三点式振荡器,现在很多应用石英晶体的石英晶体振荡器 ,还有用集成运放组成的LC振荡器。

振荡器的作用主要是将直流电变交流电.它有很多用途.在无线电广播和通信设备中产生电磁波.在微机中产生时钟信号.在稳压电路中产生高频交流电.。

题目要求产生高频正弦波,所以选用电容三点式电路,进一步考虑从而选用并联改进型电容三点式振荡器(西勒电路),因为它具有输出波形不易失真,作为可变 振荡器使用非常方便,而且幅度平稳,频率稳定性高,最高振荡频率可达百兆至千兆等特点。

振荡器使用非常方便,而且幅度平稳,频率稳定性高,最高振荡频率可达百兆至千兆等特点。

1.2、 静态工作点的确定

静态工作点的确定直接影响着电路的工作状态和振荡波形的好坏。由于振荡幅度稳定下来后,电路必然工作到非线性区,也就是说,可能进入截止区,也可能进入饱和区,静态工作点偏高,易进入饱和区.实践证明:当晶体管进入饱和区后,晶体管的输出阻抗将急剧下降(由原来的线性工作区几十千欧或几百千欧下降为几百欧姆),使谐振回路Q值大为降低,不仅使振荡波形严重失真,而且频率稳定度大为降低,甚至停振,为了避免上述情况发生,一般小功率振荡器将静态工作点设计得远离饱合区而靠近截止区,所以,c取1~4mA之间(可调整风确定)。

1.3、振荡器的起振检查

(1)用三用表检查

由于本振荡电路采用基极自给偏置,起始工作点在晶体管的放大区,故发射极应有正向偏置,接通电源后,调节电位器R ,使振荡管的静态电流lco=(1~4)nlA(可用测发射极电压Ve来得知,Ico的大小)

若 Vb—Ve<0V可判定电路已起振,工作在丙类状态,而且振荡很强。

若Vb—Ve=0.4V,可断定已起振,工作在甲乙类状态,振荡比较强。

若Vb—Ve=0.4-0.8V,工作状态可能在甲类,但不能判定是否起振,需进一步检查。

(2)用高频毫伏表检查

用高频毫伏表接在振荡器的输出端,有读数即有高频电压输出,则起振,否则未起振。

(3)用示波器检查

用示波器接于振荡器的输出端,如有高频振荡波形显示,说明起振,否则未起振。

在实验室条件下,可应用示波器检查起振,因为示波器不但能判定是否起振,还能观察波形结构,是否有失真及间歇振荡现象,以致还可判断是否有寄生振荡产生。

若用上述方法检查时,发现振荡器未起振,可从两方面着手解决:

(1)检查 是否过小,难以满足起振条件。(2)调整反馈系数的大小。

二、电路设计

2.1、正弦波振荡器的设计

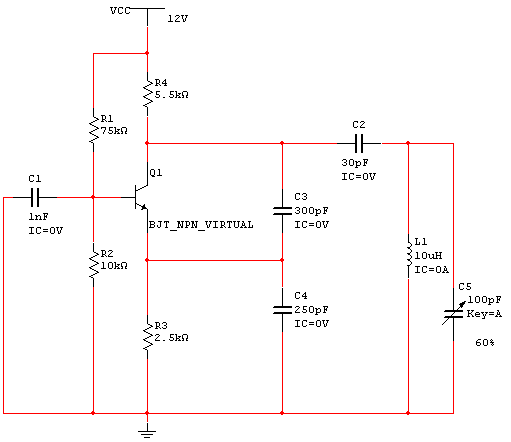

(1)、正弦波振荡器电路如图2所示。

图2 正弦波振荡器电路图

LC振荡部分是由晶体管组成的电容三点式振荡器,所用改进型电路既西勒电路, 对交流短路,因此是基极接地(共集)电路。对于振荡电路选择共集组态主要考虑电容

对交流短路,因此是基极接地(共集)电路。对于振荡电路选择共集组态主要考虑电容 的改变来调节频率,因为变容二极管加反向偏置电压和调制电压,需要有公共接地点,通常选用共基电路在电路连接上比较方便,晶体管的静态工作点由

的改变来调节频率,因为变容二极管加反向偏置电压和调制电压,需要有公共接地点,通常选用共基电路在电路连接上比较方便,晶体管的静态工作点由 决定。即

决定。即

综上所述,可以取振荡器的静态工作点 =1.4

=1.4 ,

, ,设三极管

,设三极管 60。得

60。得

为了提高电路的稳定性, 的值可适当增大,取

的值可适当增大,取 =

= ,则

,则 。

。

所以

若取流过 的电流

的电流

0.23

0.23

则

所以

即

振荡器的静态工作电流通常选在(1~4)mA, 偏大可使输出电压幅度增加,但波形失真加重。频率稳定度差,

偏大可使输出电压幅度增加,但波形失真加重。频率稳定度差, 过小会使

过小会使 较小,起振困难。

较小,起振困难。

谐振频率的计算, ,

, 为

为 总电容,如果选择

总电容,如果选择 远大于

远大于 ,

, 远大于

远大于 ,则

,则 。根据题目要求振荡器振荡频率变化范围

。根据题目要求振荡器振荡频率变化范围 =2~4MHz,所以取

=2~4MHz,所以取 uH,

uH, pF,

pF, 变化范围是5~30pF.。

变化范围是5~30pF.。

2.2、电路功能的仿真

本次电路需要使用Proteus软件进行电路功能的仿真,打开软件,按照电路图绘制好仿真电路,最后画好的仿真电路如下图3中所示。

图3 proteus仿真电路

由于振荡器的起振原理是通过在输入端接收空间中的电磁波作为扰动信号来使电路起振,但在Proteus环境中无法实现这种扰动信号,所以电路在设计好之后无法实现振荡器的功能,因此此次的仿真是通过Multisim软件进行的。其仿真结果如下图4中所示。

图4 电路仿真结果

由仿真结果我们可以看到,最后电路工作正常,能够产生预期的正弦波,所以电路的设计达到了预定的效果。

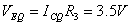

2.3、Cadence部分原理图设计

仿真之后开始用Cadence软件进行原理图以及PCB图部分的设计,开始打开Cadence中的OrCAD Capture CIS软件,新建一个原理图工程,然后按照电路图绘制好电路原理图,最后制作好的电路原理图如下图5中所示。

图5 振荡器原理图

绘制好原理图之后再依次点击各个元件,打开元件的参数信息栏,在每个元件参数栏的PCB Footprint栏中填好每个元件的封装信息,为之后的制作PCB板做好准备,在本次设计中,所有的定值电阻和电容都是使用的cap0805封装,三极管使用的是to18封装,可变电容使用的是cap196封装。设置好所有的封装之后点击Tools/Design Rules Check命令进行DRC检查,最后的检查结果如下图6所示

图6 DRC检查结果

检查结果无错误之后便可以创建网表文件,点击Tools/Create Netlist命令调出网表创建设置界面,如下图7所示。

图7 网表创建设置界面

设置好网表创建类型和保存路径之后点击确定就能开始创建网表,最后创建完成的网表内容如下:

FILE_TYPE = EXPANDEDNETLIST;

{ Using PSTWRITER 16.5.0 p001Jan-02-2014 at 14:15:16 }

NET_NAME

'N00174'

'@ZHENDANGQI.SCHEMATIC1(SCH_1):N00174':

C_SIGNAL='@zhendangqi.schematic1(sch_1):n00174';

NODE_NAME R2 1

'@ZHENDANGQI.SCHEMATIC1(SCH_1):INS158@ANALOG.R.NORMAL(CHIPS)':

'1':;

NODE_NAME C1 1

'@ZHENDANGQI.SCHEMATIC1(SCH_1):INS191@ANALOG.C.NORMAL(CHIPS)':

'1':;

NODE_NAME Q1 1

'@ZHENDANGQI.SCHEMATIC1(SCH_1):INS1442@ZHENDANGQI.NPN_0.NORMAL(CHIPS)':

'1':;

NODE_NAME C3 2

'@ZHENDANGQI.SCHEMATIC1(SCH_1):INS207@ANALOG.C.NORMAL(CHIPS)':

'2':;

NET_NAME

'N00178'

'@ZHENDANGQI.SCHEMATIC1(SCH_1):N00178':

C_SIGNAL='@zhendangqi.schematic1(sch_1):n00178';

NODE_NAME Q1 3

'@ZHENDANGQI.SCHEMATIC1(SCH_1):INS1442@ZHENDANGQI.NPN_0.NORMAL(CHIPS)':

'3':;

NODE_NAME C3 1

'@ZHENDANGQI.SCHEMATIC1(SCH_1):INS207@ANALOG.C.NORMAL(CHIPS)':

'1':;

NODE_NAME R4 2

'@ZHENDANGQI.SCHEMATIC1(SCH_1):INS142@ANALOG.R.NORMAL(CHIPS)':

'2':;

NODE_NAME C5 2

'@ZHENDANGQI.SCHEMATIC1(SCH_1):INS223@ANALOG.C.NORMAL(CHIPS)':

'2':;

NET_NAME

'N00309'

'@ZHENDANGQI.SCHEMATIC1(SCH_1):N00309':

C_SIGNAL='@zhendangqi.schematic1(sch_1):n00309';

NODE_NAME C1 2

'@ZHENDANGQI.SCHEMATIC1(SCH_1):INS191@ANALOG.C.NORMAL(CHIPS)':

'2':;

NODE_NAME L1 2

'@ZHENDANGQI.SCHEMATIC1(SCH_1):INS293@ANALOG.L.NORMAL(CHIPS)':

'2':;

NODE_NAME C4 2

'@ZHENDANGQI.SCHEMATIC1(SCH_1):INS360@ANALOG.C_VAR.NORMAL(CHIPS)':

'2':;

NET_NAME

'N00565'

'@ZHENDANGQI.SCHEMATIC1(SCH_1):N00565':

C_SIGNAL='@zhendangqi.schematic1(sch_1):n00565';

NODE_NAME R1 2

'@ZHENDANGQI.SCHEMATIC1(SCH_1):INS80@ANALOG.R.NORMAL(CHIPS)':

'2':;

NODE_NAME R2 2

'@ZHENDANGQI.SCHEMATIC1(SCH_1):INS158@ANALOG.R.NORMAL(CHIPS)':

'2':;

NET_NAME

'0'

'@ZHENDANGQI.SCHEMATIC1(SCH_1):0':

C_SIGNAL='@zhendangqi.schematic1(sch_1):\0\';

NODE_NAME C2 1

'@ZHENDANGQI.SCHEMATIC1(SCH_1):INS26@ANALOG.C.NORMAL(CHIPS)':

'1':;

NODE_NAME R3 1

'@ZHENDANGQI.SCHEMATIC1(SCH_1):INS96@ANALOG.R.NORMAL(CHIPS)':

'1':;

NODE_NAME R4 1

'@ZHENDANGQI.SCHEMATIC1(SCH_1):INS142@ANALOG.R.NORMAL(CHIPS)':

'1':;

NODE_NAME C5 1

'@ZHENDANGQI.SCHEMATIC1(SCH_1):INS223@ANALOG.C.NORMAL(CHIPS)':

'1':;

NODE_NAME L1 1

'@ZHENDANGQI.SCHEMATIC1(SCH_1):INS293@ANALOG.L.NORMAL(CHIPS)':

'1':;

NODE_NAME C4 1

'@ZHENDANGQI.SCHEMATIC1(SCH_1):INS360@ANALOG.C_VAR.NORMAL(CHIPS)':

'1':;

NET_NAME

'N00116'

'@ZHENDANGQI.SCHEMATIC1(SCH_1):N00116':

C_SIGNAL='@zhendangqi.schematic1(sch_1):n00116';

NODE_NAME R3 2

'@ZHENDANGQI.SCHEMATIC1(SCH_1):INS96@ANALOG.R.NORMAL(CHIPS)':

'2':;

NODE_NAME C2 2

'@ZHENDANGQI.SCHEMATIC1(SCH_1):INS26@ANALOG.C.NORMAL(CHIPS)':

'2':;

NODE_NAME R1 1

'@ZHENDANGQI.SCHEMATIC1(SCH_1):INS80@ANALOG.R.NORMAL(CHIPS)':

'1':;

NODE_NAME Q1 2

'@ZHENDANGQI.SCHEMATIC1(SCH_1):INS1442@ZHENDANGQI.NPN_0.NORMAL(CHIPS)':

'2':;

END.

三、PCB版图设计

在网表文件创建好之后接下来就能导入PCB Editor软件中进行相应PCB版图的制作。打开Cadence软件下的PCB Editor子软件,选择其中的Allegro PCB Design XL(legacy)进入版图编辑界面,如下图8所示。

图8 PCB Editor工作界面

点击File/New命令新建工程文件,选择好工作模式以及文件名称之后点击OK进入工作界面,然后绘制好边框、布线区和元件摆放区之后就能开始导入网表。点击File/Import/Logic命令进入导入网表的设置界面,如下图9所示。

图9 导入网表设置界面

如图9中所示设置好导入的网表格式和网表文件的路径之后点击右侧的Import Cadence,软件将自动将之前创建好的网表信息导入到PCB Editor软件中。导入成功之后点击Place/Manually就能看到导入进来的所有元件,然后将元件一一摆放到元件摆放区的合适位置,最后点击Route/PCB Router/Route Automatic命令进行自动布线,最后布线完成之后的版图如图10所示。

图10 布线完成后的PCB图

四、心得体会

时光飞逝,为期一周的课程设计已经结束了。经历了这一周的励练,自己无论在知识上、实践上还是在心理上都受到了很好的锻炼,感觉这一周的每天过的都很充实而紧凑。

虽然说我们已经在课堂上学习了高频电路,可真正动手设计还根本没有尝试过。初次拿到设计的题目时心里既激动又惆怅。激动的是我终于可以把自己所学的知识应用到实践中来了,惆怅的是看着题目心里一片茫然。

为了很好的做好这次课程设计,之前我就在图书馆查找相关资料,并且去网上搜索了解更全面的相关信息。有了这前期的准备后心里逐渐有了底。

设计开始后,在与同组同学的讨论下,我有了自己的设计思路,然后就是围绕思路绘出设计的方框图,方框图仅仅只是设计思路一个体现。在与同组人的讨论中,我们都意识到了自己的不足,突然之间明白了书到用时方恨少这句话的含义。所以在原理图的绘制中,教材几乎都被我翻烂了,最后在和大家的探讨中,我的设计思路基本完善了,也指出的我原理图中的缺点和不足。最后按照原理图我终于完成了PCB图。想想自己从懵懂到彻底弄明白整个设计图的过程,望着那错综复杂的接线,终于感受到了知识的力量,也明白了理论与实践的结合是多么不易。“学,然后知不足”,古人的话语此刻足以说明我的心境。

经历了这一周近乎涅磐般的洗礼,从电子设计到计算机操作,从理论分析到实际绘图,从懵懂到大悟…

困境不言弃,逆境求生存!这是我最深的体会。在一次次的橡皮与纸的摩擦声中,似乎在说“没有吃不了的苦,只有享不了的福”;在一次次的线条与器件的连接以及同组的相互讨论中,仿佛听到了“ 一根筷子轻轻折就断,十根筷子折也折不断”的声音。这周的课设似乎让我突然之间又成长了许多、许多…

五、参考文献

1. 谢沅清,邓钢.通信电子线路. [M]北京:电子工业出版社,20##年。

2. 李秀人.电子技术实训指导. [M]北京:国防工业出版社,20##年。

3. 铃木雅臣.晶体管电路设计. [M]北京:科学出版社,20##年。

4. 张肃文,高频电子线路(第四版),北京:高等教育出版社,2004

5. 高吉祥,易凡,丁文霞,电子技术基础实验与课程设计,北京:电子工业出版社,2002

本科生课程设计成绩评定表

指导教师签字:

年 月 日

-

Personal Statement范文

PersonalStatementAsaseniormajoringinEconomicsatXXXoneofthetopfouruniversiti…

-

personal_statement模板50篇

IamkeenonsportsandoutdoorpursuitsIhaveenjoyedarangeofactivitiesfromcountrys…

-

Personal Statement个人陈述

IamathinkerbutnotonetothinkoutloudIlovemyselfbutamnotinlovewiththesoundofmy…

-

怎样写一份成功的personal statement~

转以下是第三方论点里面对PS很有帮助本人一直认为硕士申请过程中两个主观方面的努力是最重要的1根据自己的情况实事求是因人制宜选择适合…

-

如何写Personal Statement(个人陈述)

一步步教你怎么写PS一PS是PersonalStatement的简称是我们申请美国研究生院的重要材料之一一份完美的PS有可能使你申…

-

高频电子线路实验报告正弦振荡试验

太原理工大学现代科技学院高频电子线路课程实验报告专业班级测控1001班学号姓名指导教师实验二正弦振荡实验一实验目的1掌握晶体管振荡…

-

三点式正弦波振荡器实验报告

三点式正弦波振荡器一实验目的1掌握三点式正弦波振荡器电路的基本原理起振条件振荡电路设计及电路参数计算2通过实验掌握晶体管静态工作点…

-

LC正弦波振荡器报告

LC正弦波振荡虚拟实验LC正弦波振荡虚拟实验04008307郭佩1电容三点式1C1100nFC2400nFL110mH示波器频谱仪…

-

电子电路综合实验-LC正弦波振荡器报告

LC正弦波振荡虚拟实验LC正弦波振荡虚拟实验1电容三点式1C1100nFC2400nFL110mH示波器频谱仪1LC正弦波振荡虚拟…

-

高频电容三点式正弦波振荡器课程设计报告

课程设计任务书学生姓名专业班级电子指导教师吴皓莹工作单位信息工程学院题目高频电容三点式正弦波振荡器初始条件具较扎实的电子电路的理论…

-

高频电子线路实验报告正弦振荡试验

课程名称实验项目实验地点专业班级学生姓名指导教师本科实验报告正弦波振荡器信号与系统及高频电子线路实验室电科1201班学号20xx0…