数电课程设计报告

《电子技术基础(数字部分)》

课程设计

姓名:

学号:

班级: 11电气1班

专业:电气工程及其自动化

学院:电气与信息工程学院

20##年3月

目录

一、设计任务··················································································· 1

二、设计要求··················································································· 1

三、工作原理和电路分析··································································· 1

1、秒脉冲信号发生器································································· 2

(1)振荡器········································································ 2

(2)分频电路···································································· 3

2、 计数器··············································································· 4

(1) 六十进制计数器························································· 4

(2) 二十四进制计数器······················································ 5

3、 校时电路············································································ 5

4、 数字钟原理总图··································································· 6

四、 仪器与工具·············································································· 6

五、元器件清单················································································ 7

数字钟的设计与制作

一、设计任务

数字钟是数字集成电路构成的、用数码显示的一种现代计时器,与传统的机械钟相比,它具有走时准确、显示直观、无需机械传动等特点。因而广泛用于车站、码头、机场、商店等公共场所。在控制系统中,也常用来作为定时控制的时钟源。

本次课程设计要求以中规模集成电路为主,利用所学知识,设计一个数字钟。通过本次课程设计,进一步加强数字电路综合应用能力,掌握数字电路的设计技巧,增强实践能力,以及熟练掌握数字钟的系统设计、组装、调试及故障排除的方法。

设计过程针对简易数字钟的设计要求,先定义和规定各个模块的结构,再对模块内部进行详细设计。详细设计的时候又根据给定的芯片,分析各芯片是否适合本次设计,选择较合适的芯片进行设计,并将设计好的模块组合调试,在Multisim下仿真通过。完成仿真后,对给定的实验器材进行必要的检测,并按照仿真后的设计进行实际电路图的搭建与调试,并最终完成电路图的设计与制作。

二、设计要求

1、设计一台可以显示时、分、秒的数字钟;

2、具有校时功能,可以对小时和分单独校时;

3、要求电路主要采用74系列中小规模集成电路来实现。

三、工作原理和电路分析

数字电子钟由信号发生器、“时、分、秒”计数器、译码器及显示器、校时电路等组成。秒信号产生器是整个系统的时基信号,它直接决定计时系统的精度,一般用振荡器加分频器来实现。将标准秒脉冲信号送入“秒计数器”,该计数器采用六十进制计数器,每累计60秒发出一个“分脉冲”信号,该信号将作为“分计数器”的时钟脉冲。“分计数器”也采用六十进制计数器,每累计60分,发出一个“时脉冲”信号,该信号将被送到“时计数器”。“时计数器”将采用二十四进制计数器,可以实现一天24小时的累计。

“时、分、秒”计数器的输出状态通过六位带译码功能的LED显示器显示出来。其原理框图如图1示。

图1 数字钟工作原理方框图

1、秒脉冲信号发生器

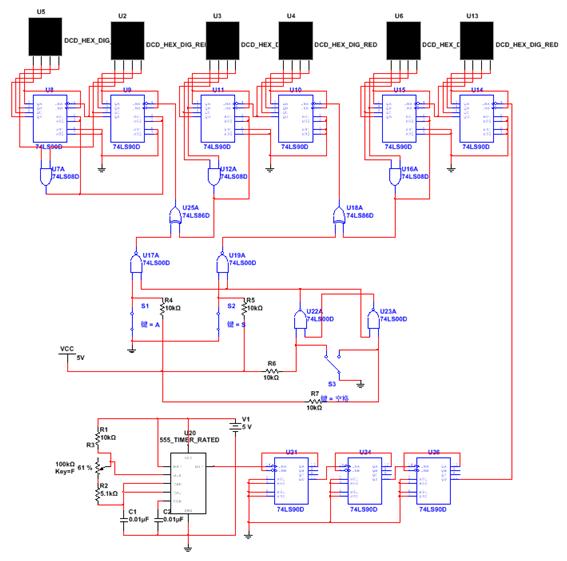

秒脉冲信号发生器是数字电子钟的核心部分,他的精度和稳定度决定了数字钟的质量。该发生器由555定时器构成的振荡器与74LS90构成的分频器组合产生秒脉冲信号。

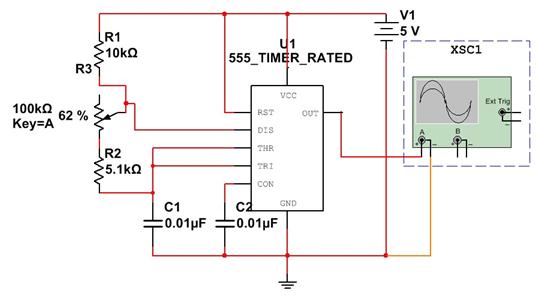

(1)振荡器

一般来说,振荡器的频率越高,计时器的精度就越高,但耗电量将增大。通常我们用555定时器与RC构成的多谐振荡器,经过调整输出1000Hz脉冲。构成的多谐振荡器及使用Multisim仿真的波形分别如图2、图3所示。

图2 555构成的多谐振荡器

图3 多谐振荡器仿真波形

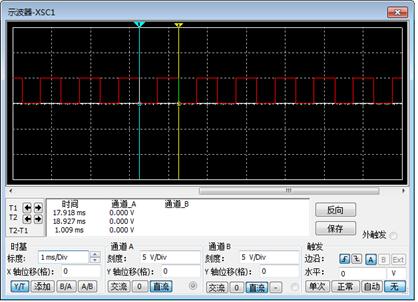

(2)分频电路

分频电路功能主要有两个,一是产生标准秒脉冲信号,一是提供功能扩展电路所需的信号。分频电路主要由二-五-十进制计数器74LS90组成。因为振荡器产生的是1000Hz的脉冲,而时基信号要求为1Hz,因此,利用10分频的电路比较好。将1000Hz的振荡信号作为第一级74LS90的输入脉冲信号,经过第一级分频后f1=100Hz。以此类推1Hz的时基信号需要三次分频。分频电路及分频仿真波形如图4和图5所示。

分频电路功能主要有两个,一是产生标准秒脉冲信号,一是提供功能扩展电路所需的信号。分频电路主要由二-五-十进制计数器74LS90组成。因为振荡器产生的是1000Hz的脉冲,而时基信号要求为1Hz,因此,利用10分频的电路比较好。将1000Hz的振荡信号作为第一级74LS90的输入脉冲信号,经过第一级分频后f1=100Hz。以此类推1Hz的时基信号需要三次分频。分频电路及分频仿真波形如图4和图5所示。

图4 分频电路

图5 分频后仿真波形

2、计数器

数字钟是以“时、分、秒”的十进制数字显示的,分钟和秒钟都是六十进制的计数器,而小时是二十四进制的计数器。这里还是采用74LS90为计数芯片。

(1)六十进制计数器

74LS90是集成异步计数器,而数字钟的时、分、秒的个位是逢十进位,故它们的进位可直接由低位QD向高位CP输出。秒十位和分十位是逢六进位的,它们的进位要用BCD码输出,并使用具有两个输入端的与门来控制进位,如分十位的BCD码为0110(即计数器数值达到6)时,与门输出低电平,这个低电平一方面向高位进位,另一方面输送给秒十位的清零端R01和R02使其清零,由于秒个位是十进制计数器,只要自动回零就可以了。这样就完成了60秒钟的计时任务;分钟工作原理和秒钟工作原理是一样的。如图6所示。

74LS90是集成异步计数器,而数字钟的时、分、秒的个位是逢十进位,故它们的进位可直接由低位QD向高位CP输出。秒十位和分十位是逢六进位的,它们的进位要用BCD码输出,并使用具有两个输入端的与门来控制进位,如分十位的BCD码为0110(即计数器数值达到6)时,与门输出低电平,这个低电平一方面向高位进位,另一方面输送给秒十位的清零端R01和R02使其清零,由于秒个位是十进制计数器,只要自动回零就可以了。这样就完成了60秒钟的计时任务;分钟工作原理和秒钟工作原理是一样的。如图6所示。

图6 六十进制计数器

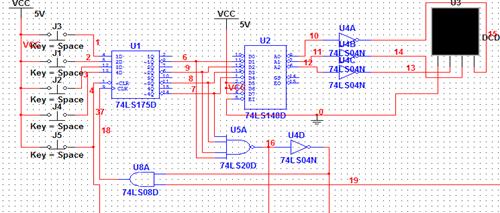

(2)二十四进制计数器

对于时钟,时位要实现二十四进位,与门的两个输入信号分别来自时十位代码输出QB(0010)和时个位代码QC(0100),即只有计时到二十四小时的那一刻,与门才输出一个低电平。此低电平连接到时十位和时个位清零端R01和R02,实现二十四小时的清零目的,如图7所示。

对于时钟,时位要实现二十四进位,与门的两个输入信号分别来自时十位代码输出QB(0010)和时个位代码QC(0100),即只有计时到二十四小时的那一刻,与门才输出一个低电平。此低电平连接到时十位和时个位清零端R01和R02,实现二十四小时的清零目的,如图7所示。

图7 二十四进制计数器

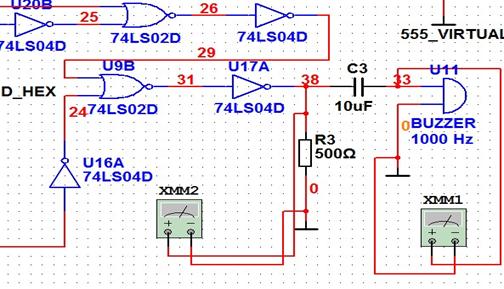

3、校时电路

当接通电源或计时出现误差时,都需要对时间进行校正。校正电路如图8所示。S1、S2分别是时校正和分校正开关,S3为校正轻触开关。不校正时,S1和S2都闭合;当断开S1,闭合S2时,拨动S3对时进行调时;当闭合S1,断开S2时,拨动S3对分进行调时。

图8 校时电路

4、数字钟原理总图

将之前的各个模块电路,通过对应的门电路连接起来,其原理总图如图9所示。

图9 原理图总图

四、仪器与工具

1、试验箱1台;

2、数字示波器1台;

3、万用表1个;

4、镊子1把;

5、剥线钳1把。

五、元器件清单

六、困难与解决办法

1、仿真部分

(1)芯片认知

对芯片的不熟悉在仿真前期是个很大的困难,但是却也是最好解决的。在参考了相关资料以及网络查询以后,对555定时器和74LS90有了简单的了解,通过功能表与实例说明,仿照相关连接方式,设计出符合要求的电路。

(2)校时电路设计

模块单独设计的时候,按照设计要求上提供的校时电路连接时,发现无论S1与S2的状态如何,都可以进行调时,与要求不符,于是找到几处可能的问题,通过多次尝试改动,将校时电路完成。初时设计时将S3一端与秒脉冲信号端通过与门连接到秒信号输入端,实现在调时时时钟停止走动的功能。但后来在与人交流中发现,电子表在调时时,秒钟依然在走动,因此将这一功能去掉。

(3)显示电路

在仿真时,电路连接基本上没问题,但是发现在数码管的选择上会有不同,起初选择DCD_HEX,结果发现电路会有抖动,以及显示不流畅现象,在换成DCD_HEX_DIG后显示就正常了。

(4)总图连接

在将各模块连接的时候出现的问题比较多,特别是在与校时电路连接的时候,起初因为没有用异或门连接,导致校时出现错误,在不断的改动中还出现不走时、不进位等现象。最后是通过在图书馆找资料解决的,模仿别人的连接,发现了问题所在。

(5)仿真时间与现实时间不符

仿真时间过慢的问题导致许多要的数据出不来,网上的方法是调节步长,但是在总图进行仿真时发现效果不明显,在示波器现实时发现信号失真。因此在通过多次尝试以后,发现了比较好的方法。在总图仿真的时候,可以将秒信号输入端与振荡器的输出端直接相连,或者与第一分频器输出端相连,这样就可以快速仿真,而且在分和时还可以单独连接一个信号,这样就能更快的确定个位和十位之间的进位是否可行。如果另外接函数信号发生器的话,效果不是很明显,所以没有采用。在示波器显示的时候可以稍微调节一下步长,这样失真不会很明显。

2、实际电路连接部分

(1)校时电路

在实际电路连接时,手动开关改用了电平开关,轻触开关S3改用了手动脉冲信号按钮,在连接时,因为试验箱上的开关自带电源、接地和电阻,因此,连接时这三部分可以不用连接。在接手动脉冲时注意A和 不能接反,否则校时时会出现不稳定现象。

不能接反,否则校时时会出现不稳定现象。

(2)电路连接连线

在电路连接完成后,发现部分数码管不能正常显示,也不能进行调时。在经过仔细检查时发现74LS00、74LS08和74LS86的接地端被接到了电源上,且时和分的清零端没有接,以后接线时注意是否连完全,先是否在面包板上插偏的问题。

(3)调时

调时过程中,经常出现时和分在调时时会相互不规则影响。起初以为之前的接线问题把芯片烧坏了,在换了新的芯片后问题依然存在。仔细校对电路也没有发现问题,开关测试也一切正常,在排查了所有问题之后,发现是试验箱的问题。

七、心得体会

实验结束了,在实验过程中发现了许多问题,也学会了很多。在我们对未知的活着一知半解的东西进行操作时,我们应该积极学会寻找资料或相关人士的帮助,做好充分的准备再动手,这样可以节省很多时间。我们要勇于尝试,有了好的想法就应该去实现,虽然不一定有用,但可以学到更多。在仿真过程中,凭着已有的基础,尝试了多种不同连接,最终确定比较好的方案,使得电路仿真时更准确、更方便。实际电路连接时必须要仔细,尽量不要出现错误,因为在复杂的连线中检查是比较困难的,因此前期的电路分布是很重要的环节,好的分布可以使得电路看起来更清晰,检查时更方便。我们不但要学习别人的好的地方,更要有自己的大胆想象,并且努力去尝试。

第二篇:数电课程设计报告模板

华南理工大学广州学院

数字电路课程设计报告

题目:四人智力竞赛抢答器

专业: 通信工程

班级: 2

姓名: 戴汉沛

学号: 201038787161

序号: 12

日期: 20##年12月

一. 设计目的

为了巩固课本所学知识,培养动手能力和实际解决问题的能力,加深对课堂知识的理解和运用,进一步学习和熟悉各种常用芯片的规格和使用,能掌握电路的组装和基本问题的排除。…………

二. 设计指标:

设计一台可供4名选手参加比赛的智力竞赛抢答器。 用数字显示抢答倒计时间,由“9”倒计到“0”时,无人抢答,蜂鸣器连续响1秒。选手抢答时,数码显示选手组号,同时蜂鸣器响1秒,倒计时停止。

三. 总体框图设计

四. 功能模块设计和原理说明

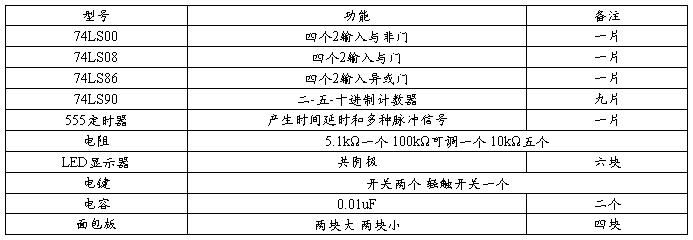

1)以锁存器为中心的编码显示电路

抢答信号的判断和锁存可采用触发器或锁存器。若以四D触发器74LS175为中心构成编码锁存系统,编码的作用是把锁存器的输出转化成8421BCD码,进而送给7段显示译码器。其真值表3:

表3锁存编码真值表

工作原理:

D触发器74LS175的输出Q非控制显示模块显示组号。

当无人抢答时,4个D触发器的输出Q非相与,为“1”时,脉冲能够进入触发器,有一人抢答时,与门中有一个变为“0”,使脉冲不能进入触发器,从而防止其他人抢答。并停止计时。

将与非后的信号用于控制声音模块报警。

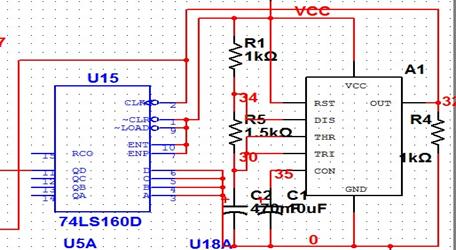

2)脉冲产生电路:

工作原理:该模块为由555定时器构成的多谐振荡器。并以74LS160做10分频,产生10Hz和1Hz的脉冲信号。

3)倒计时显示电路:

该电路可采用十进制同步减计数器74LS190,主持人宣布开始时,按下按钮,同时使计数器置数为“9”,并在脉冲作用下开始倒计时并在显示器上显示,到零时停止。

工作原理:由74LS190十进制计数器计数,其输出端驱动BCD数码器。160的进位输出反相信号

进位信号和抢答信号控制1HzCP信号的输入,即计数到0时不会倒回9再计时,也控制计数到时抢答模块不许再抢答同时声音模块块报警。190的MR接收抢答模块的信号,当抢答模块复位时190也复位。

4)音响电路:

由主持人、选手、倒计时共同控制它的输入,使其在主持人开始、选手抢答、倒计时到零时都能鸣叫。

(5)元件选择。

五. 总电路图说明

(1)4名选手编号为:1,2,3,4。各有一个抢答按钮,按钮的编号与选手的编号对应,也分别为1,2,3,4。

(2)给主持人设置一个控制按钮,用来控制系统清零(抢答显示数码管灭灯)和抢答的开始。

(3)抢答器具有数据锁存和显示的功能。抢答开始后,若有选手按动抢答按钮,该选手编号立即锁存,并在抢答显示器上显示该编号,同时扬声器给出音响提示,封锁输入编码电路,禁止其他选手抢答。抢答选手的编号一直保持到主持人将系统清零为止。

(4)抢答器具有定时(9秒)抢答的功能。当主持人按下开始按钮后,定时器开始倒计时,定时显示器显示倒计时间,若无人抢答,倒计时结束时,扬声器响,音响持续1秒。参赛选手在设定时间(9秒)内抢答有效,抢答成功,扬声器响,音响持续1秒,同时定时器停止倒计时,抢答显示器上显示选手的编号,定时显示器上显示剩余抢答时间,并保持到主持人将系统清零为止。

(5)如果抢答定时已到,却没有选手抢答时,本次抢答无效。系统扬声器报警(音响持续1秒),并封锁输入编码电路,禁止选手超时后抢答,时间显示器显示0。

(6)可用石英晶体振荡器或者555定时器产生频率为1Hz的脉冲信号,作为定时计数器的CP信号。

六.总结(感想和心得等)

本次设计我选择的是数字智力竞赛抢答器的设计,这个课题用到了数字电路方面的知识,通过这次课程设计,使我对与非门以及集成电路有了一定的了解,对课本上的知识有了近一步的掌握。完成本次课程设计的过程,是一个从无到有的过程,因为以前没有过类似的课程设计,所以起初不知该从何下手,后来仔细阅读设计的题目和要求,阅读设计指导书,再到图书馆和网上查找资料,总算是有点眉目了。通过这次课程设计,使我对与非门以及集成电路有了一定的了解,对课本上的知识有了近一步的掌握。

-

数 字 电 路 课 程 设 计 报 告

数字电路课程设计报告课题名称:篮球竞赛30秒计时器姓名:学号:专业班级:通信工程1指导教师:设计日期:20##年1月5日摘要:随着…

-

数电课程设计报告

数电课程设计说明题目数字电子钟的设计部班级名号书系专业姓学指导教师起止日期摘要这次课程设计采用的课题是数字电子钟的设计数字钟是一种…

-

数电课程设计报告

电子技术基础数字部分课程设计电子技术基础数字部分课程设计姓名学号班级专业学院20xx年3月电子技术基础数字部分课程设计目录一设计任…

-

数电课程设计报告

五邑大学数字电路课程设计报告题目两位十进制计数显示器院系信息工程学院专业通信工程学号学生姓名张国辉指导教师陈鹏报告日期20xx年4…

-

数电课程设计报告

《数字逻辑电路设计》课程设计总结报告题目:汽车尾灯控制器设计指导教师:设计人员(学号):班级:电信111日期:20##年5月一、设…

-

数字电路课程设计总结报告

《数字电路》课程设计总结报告题目:数字钟设计专业班级学生姓名学号指导教师日期20##年12月11目录一、设计任务...1(一)设计…

-

武汉纺织大学数电课程设计实验报告

武汉纺织大学数字电子课程设计实验报告设计题目多路智力竞赛抢答器姓名班级学号指导教师陶恒齐20xx年7月1日摘要课程教学的要求对学生…

-

数字电路课程设计总结报告

数字电路课程设计总结报告题目:交通灯控制器1、设计背景2、设计任务书3、设计框图及总体描述4、各单元设计电路设计方案与原理说明5、…

-

江苏大学09级数字逻辑课程设计报告

数字逻辑课程设计多功能数字钟学院名称计算机科学与通信工程专业班级通信0902学生学号指导老师赵念强完成日期20xx年7月2日多功能…

-

江苏大学09级数字逻辑课程设计报告

数字逻辑课程设计多功能数字钟学院名称计算机科学与通信工程专业班级通信0902学生学号指导老师赵念强完成日期20xx年7月2日多功能…

-

数字电路课程设计-多功能数字时钟设计报告

多功能数字时钟设计报告目录一设计任务和要求2二设计的方案的选择与论证21总体电路分析22仿真分析33仿真说明3三电路设计计算与分析…