时序逻辑电路实验报告

二、时序逻辑电路实验题目

1. 试用同步加法计数器74LS161(或74LS160)和二4输入与非门74LS20构成百以内任意进制计数器,并采用LED数码管显示计数进制。采用555定时器构成多谐振荡电路,为同步加法计数器提供时钟输入信号。例如,采用同步加法计数器74LS 161构成60进制加法计数器的参考电路如图2所示。

设计:

(一)设计一个固定进制的加法计数器。

(1)利用555定时器设计一个可以生时钟脉冲的多谐振荡器,使其构成长生脉冲,对同步加法器74LS161输入信号,根据555定时器构成的多谐振荡器的周期可定,由图可的T=T1+T2=0.7(RA+RB)C+0.7 RBC=0.7(RA+2RB)C,通过改变电阻RA,RB和C的大小,可以改变脉冲的周期。所发电阻为2个510kΩ,C=1uF,则T=0.7(RA+2RB)C=0.7x510x3x0.1/1000s=1.071s.

(2)利用十六进制的加法计数器74LS61组成百以内任意进制计数器,可以用清零法和置数法改变计数器的技术进制,由于译码显示器可以显示0.1.2.3….9,所以一片74LS161只可以控制一个显示器,就要将一片74LS161改为十进制,最后再利用级联的74LS161改变数组进制,可以将不同进制的数值用显示姨妈其显示出来,下面以33进制为例进行设计,

a.清零法,异步清零信号为 =

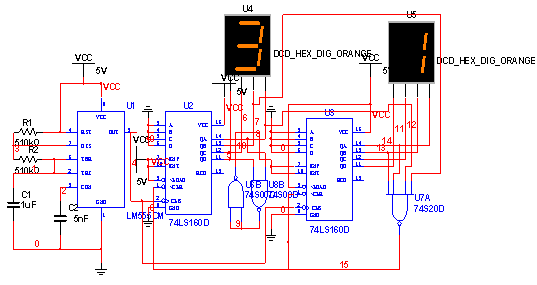

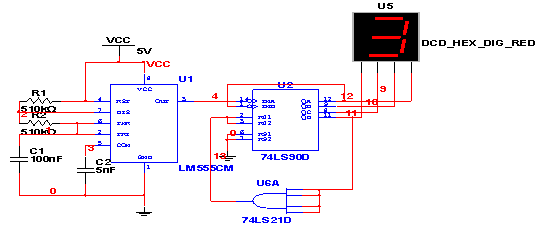

= 计图如下:

计图如下:

上图中两个一码显示,左边是低位显示,右边为高位显示。

(3)状态转换图为:

B,置数法,为了使显示数字范围在0~9,才能使显示译码器显示0~9,则是置数QA1QB1QC1QD1=0000,,在第一个74LS161与第二个之间对进位信号进行改造,将进位信号改为RCO=QAQD=  ,用两个与非门实现该功能。则当

,用两个与非门实现该功能。则当 =1,

=1, =0,且时钟信号来临时,计数器置数QA1QB1QC1QD1=0000,置数信号LD=

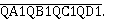

=0,且时钟信号来临时,计数器置数QA1QB1QC1QD1=0000,置数信号LD= 则设计电路为:

则设计电路为:

上图中两个一码显示,左边是低位显示,右边为高位显示。

(二)设计一个进制可以容易改变的加法计数器。

(1)555定时器原理同上书(1)。

(2)同样将低位74LS161片与高位片之间设置成十进制和进位信号和上述一样,

(3)在这里增加设置进制改变控制,可以利用四位BCD8421码比较器74LS85进行比较,利用8个数据选择开关进行设置,用一组四位设置进制的十位数字,另一组的四位设置个位数字,当加法计数器的个位和十位数字和设置进制的十位和个位数字相等时,QA=B=1,再经过与非门的处理实现清零信号。这样就可以实现加法计数器的进制再百以内实现计数。

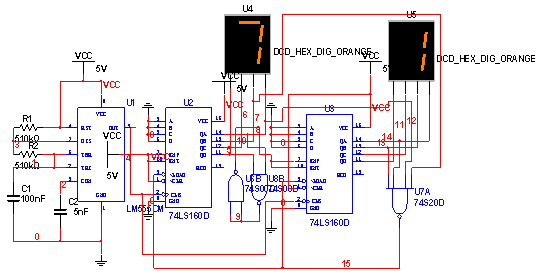

如上图所示:进制设置为31进制,计数计到25.

上图同样左边为低位计数,右边为高位计数,开关左边四位控制计数进制的十位,右边四位控制进制的个位,左边四位二进制比较器(74LS85)为个位比较,右边四位二进制比较器(74LS85)为十位比较。由于实现百以内的进制计数,再加之74LS161之间的连接限制和显示限制(可显示0~9),故开关的两组四位控制设置只能设置范围为0000~1001,计数器才可以正常工作。

分析:

上述第一种方案,局限在于计数器的进制固定不变,只由一种进制计数,但是所用的电子元器件比较少,功耗少,适用于一种固定场合且记住进制不变的计数,几十进制一般不变化,所花费用比较少。

第二种方案,虽然所用电子元器件较多,功耗大,进制可以根据需要进行人工设置,适应环境能力强,可应用不同机制的计数。在市场比较大的和应用场所复杂的环境下,可以大批量生产一降低其制造成本,获得一定的经济效益。

改进:

在对设计电路图进行仿真的时候可以改进,因为时钟脉冲的周期为T=1.071s,进行计数仿真使需要观察计数的变化,但是当进制比较大的时候,等待时间比较长,浪费大量时间,为了使主要精力集中于设计和检测计数的准确与否,可以将放电(也是充电)电容值设置小一点,如上图设置为0.1uF即100nF,则 =0.1T=0.1071s,可以大大减少设计时间。

=0.1T=0.1071s,可以大大减少设计时间。

2. 试用十进制异步加法计数器74LS90和二4输入与门(74LS21)构成百以内任意进制计数器,并采用LED数码管显示。用555定时器设计多谐振荡电路,为同步加法计数器74LS90提供时钟输入信号。例如,采用同步加法计数器74LS90构成26进制加法计数器的参考电路如图3所示。

设计:

(一)计数器进制固定不变

(1)此实验的设计时钟脉冲提供使仍然是由555定时器构成的多谐振荡器产生脉冲,器原理叙述同上体所述。

(2)根据2/5分频异步加法器74LS90,其实有二进制加法计数器和无禁止加法计数器构成成,若时钟从CPA段输入,在外部将QA和CPB连接,就构成了十进制计数器。器功能是:

当R0(1)= R0(2)=1,S9(1)= S9(2)=0时,输出QAQBQCQD=0000,为异步清零。

当R0(1)= R0(2)=0,S9(1)= S9(2)=1时,输出QAQBQCQD=1001,为置数。

当R0(1)R0(2)=0,S9(1) S9(2)=0时,为计数。

(3)74LS90的级联可以扩大计数的进制和容量,可以将低位片的最高位QD连接到高位的CPB段,就可以实现级联。

(4)计数器的进制的确定。利用异步清零法实现进制改变.

A.对于进制M小于片的进制N使,可以将M对应的代码用逻辑信号表示。例如实现8进制,则将8对应的二进制代码1000,则可以用与门实现R0(1)= R0(2)=QD。

设计电路图如下所示:

如图所示,电路图为8进制计数器,左边为低位计数,右边为高位计数,此时计数到3..

B.对于M大于N的进制可以将74LS90进行级联,在进行类似的方法处理。例如设计

52进制的设计,可以将两片进行级联,53对应的代码为01010011,则对应的逻辑为 R01(1)= R01(2)=R02(1)= R02(2)= QA2 QC2 QA1 QB1。

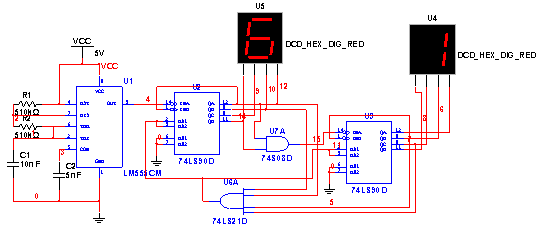

设计的电路图如下:

如图所示,电路图为53进制计数器,左边为低位计数,右边为高位计数,此时计数计到16..

上述电路在仿真使为加快调试速度,减小了电容,使周期大大缩小。如上两幅图中用到的电容值分别为100nF和10nF,使周期为原来的1/10和1/100.

(二)计数器进制固定可变。

其余分析方法均与第一题中的应用比较器74LS85思路一致,和上例中的分析以及级联分析相同,这里不再详细分析。用和上题中的相同方法可以获得技术进制的改变计数,使其功能变得强大。

开关左边四位设置计数进制的十位,右边四位设置进制的个位,左边四位二进制比较器(74LS85)为个位比较,右边四位二进制比较器(74LS85)为十位比较。

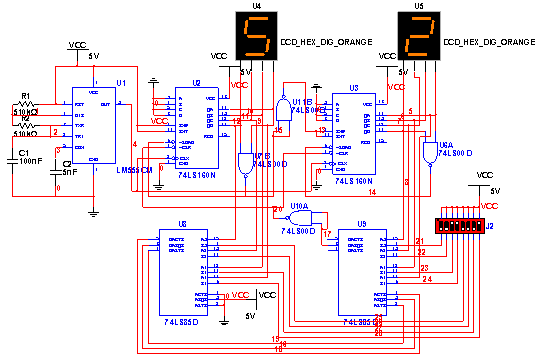

如图所示,电路图为所设置的32进制计数器,左边为低位计数,右边为高位计数,此时计数计到22..

3,附加:设计一个二十四小时的时钟.利用74LS90和555定时器设计。

设计:

(1)由555定时器构成的多谢振荡器,时钟周期是T=T1+T2=0.7(RA+RB)C+0.7 RBC=0.7(RA+2RB)C,为使其其周期为1s,则取C=1uF,RA=400 kΩ, RB =300 kΩ,使其周期T=1s,可以实现适合于实际的简易电子表。

(2)相邻的两片74LS90片之间的级联,根据进制的不同选择用不同的逻辑电路实现,

24小时时钟设计的相邻进制有10和6,

若为10进制,则CPB=QC QD=  ,

,

若为6进制,则CPB=QB QC=  ,

,

上式中,CPB是高位的输入端,QA,QB,QC,QD为低位的输出端。

(3)设计时钟的进制需要改变74LS90的进制,采用清零方法,控制一秒(分,时)的相邻两片之间的因进制不同而用不同的逻辑电路实现。该电路中有60,60,和24,

若为60(秒,分)进制,则清零信号为R01(1)= R01(2)=R02(1)= R02(2)=QB2QC2=  ,

,

若为24(时)进制,则清零信号为R01(1)= R01(2)=R02(1)= R02(2)=QB2QC1=  ,

,

上式中,R01(1), R01(2),R02(1), R02(2)是低位和高位的清零端,QA1,QB1,QC1,QD1为低位的输出端,QA2,QB2,QC2,QD2为低位的输出端。

(4)分别控制秒(分,时)的以两片为一组的控制之间的进位也是不同的,

采用不同的 ,可以轻易发现其秒,分,时之间的进位信号和上一分析之间的清零信号相同,气表述与上相同。

(5)对所组成的秒,分,时的控制组合安杉树进行连接,就可以组成24小时的 时钟设计,并进行仿真。

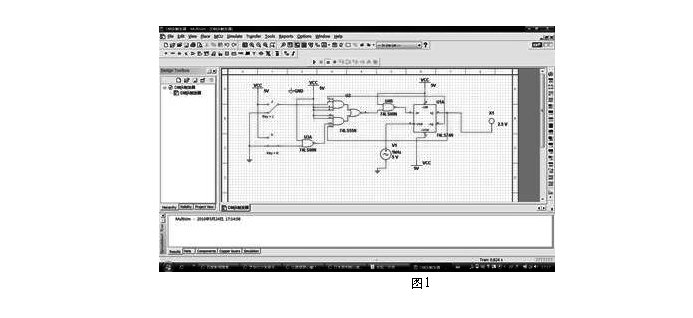

在实际仿真时为了使仿真的速度加快,检验其设计是否正确,故调节其周期大大减小,取C=1nF,RA=RB=510 kΩ,则T为0.001071s.

用multisim进行仿真截图如下:

上图所示为24小时时钟显示,左下角为由555定时器构成的多谢振荡器,左上角为两片74LS90构成的秒计数,右上角两片74LS90构成的分计数,右下角两片74LS90构成的时计数,其进制依次分别是60,60和24.

如上图现实时间是13:44:45

设计不足:

由74LS90和555定时器构成的多谢振荡器组成的电路,因计数开始的时,从低位进行计数,所以高位无信号,会由于随机的开始使高位显示随机数字,有时所显示的数字已经超出设置的技术范围。

通过清零法改变计数进制,有时会出现清零的不可开行问题。因为74LS90内部的四个触发器的清零时间有一定的差异,只要与门中有一个半年为高电平的时间有稍微的提前,则输出为1,清零结束。由此带来的就会出现短暂的高电平。在仿真中就会出现一个窄尖峰。

解决办法:

利用基本RS触发器可以改善,用其低位信号的置数和恢复可以消除该隐患,从而从根本上消除由于每次的重新开始计数其高位现实的任意数字,使其在CP信号低电平时间内,计数器始终清零,因此计数器能够可靠清零。

设计体会心得:

(1)学习课本的理论知识和理解,通过自己的融汇和创新设计,是对课本的理论理解更加深入和透彻,进而更好的掌握所学的知识。

(2)通过利用软件仿真和实物元件实验,是对具体的实物有更好的理解,是动手能力增强,为以后的设计和实验打下坚强的基础。

(3)通过仿真可以发现解体和绘制电路图过程中不易发现的细小错误,有时这些小错误会导致整个设计的崩溃,提醒我们做题和操作过程中一定自习和认真。

(4)有时为实现比较复杂的电路结构时,所发的电子元器件不够时,需要自己购买,这就需要考虑既能实现期望的电路功能,有在经济和实惠的范围之内,必须做到全面的考虑,以达到最优化设计。从而为未来的职业考虑。

(5)在自己一个人的学习理解中不免不了一定的思维局限性。通过电路的设计,加强同同学的交流,收获不同的理解方式和思路,采取更简单和灵活的思维方式,是自己的学习效率提高,昂面加强了同学之间的学习互动力。

第二篇:触发器-时序逻辑电路实验报告

实验报告

实验报告

课程名称:数字电子技术基础实验 指导老师:樊伟敏 成绩:__________________

实验名称:触发器应用实验 实验类型:设计类 同组学生姓名:__________

一、实验目的和要求(必填) 二、实验内容和原理(必填)

三、主要仪器设备(必填) 四、操作方法和实验步骤

五、实验数据记录和处理 六、实验结果与分析(必填)

七、讨论、心得

一、实验目的

1. 加深理解各触发器的逻辑功能,掌握各类触发器功能的转换方法。

2. 熟悉触发器的两种触发方式(电平触发和边沿触发)及其触发特点。

3. 掌握集成J-K触发器和D触发器逻辑功能的测试方法。

4. 学习用J-K触发器和D触发器构成简单的时序电路的方法。

5. 进一步掌握用双踪示波器测量多个波形的方法。

二、主要仪器与设备

实验选用集成电路芯片:74LS00(与非门)、74LS11(与门)、74LS55(与或非门)、74LS74(双D

触发器)、74LS107(双J—K 触发器),GOS-6051 型示波器,导线,SDZ-2 实验箱。

三、实验内容和原理

1、D→J-K的转换实验

①设计过程:J-K 触发器和D触发器的次态方程如下:

J-K 触发器: , D触发器:Qn+1=D

, D触发器:Qn+1=D

若将D 触发器转换为J-K触发器,则有: 。

。

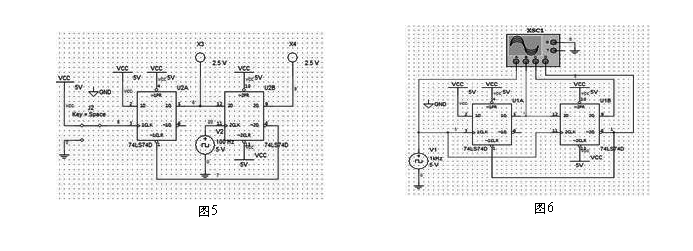

②仿真与实验电路图:仿真电路图如图1所示。操作时时钟接秒信号,便于观察。

③实验结果:

2、D 触发器转换为T’触发器实验

①设计过程:D 触发器和T’触发器的次态方程如下:

D 触发器:Qn+1= D , T’触发器:Qn+1=!Qn

若将D 触发器转换为T’触发器,则二者的次态方程须相等,因此有:D=!Qn。

②仿真与实验电路图:仿真电路图如图2 所示。操作时时钟接秒信号。

③实验结果:发光二极管按时钟频率闪动,状态来回翻转。

3、J-K→D的转换实验。

①设计过程:J-K 触发器和D触发器的次态方程如下:

J-K 触发器: , D触发器:Qn+1=D

, D触发器:Qn+1=D

若将J-K触发器转换为D触发器,则二者的次态方程须相等,因此有:J=D,K=!D。

若将J-K触发器转换为D触发器,则二者的次态方程须相等,因此有:J=D,K=!D。

②仿真与实验电路图:

如图3所示。

③实验结果:符合D触发器的功能,D=1,发光二极管亮,Q=1;D=0,发光二极管不亮,Q=0。

4、J-K→T′的转换实验。

①设计过程:J-K 触发器和T’触发器的次态方程如下:

J-K 触发器: , T’触发器:Qn+1=!Qn

, T’触发器:Qn+1=!Qn

若将J-K 触发器转换为T’触发器,则二者的次态方程须相等,因此有:J=K=1

②仿真与实验电路图:仿真与实验电路图如图4所示。

图4

③实验结果:符合T′触发器的功能,发光二极管按时钟频率闪动,状态来回翻转。

5、用双D触发器设计一个单发脉冲发生器。

(1)手动单次脉冲发生器的测试:手控脉冲接逻辑开关,系列脉冲为秒脉冲信号,两个D 触发器的输出分别接发光二极管。

①实验原理:手动提供一个脉冲,此时第一个D触发器的输出为高电平,经过一个cp脉冲后,由于第二个D触发器的输入是第一个D触发器的输出,所以其输出也为高电平,Q非为低电平,第一个触发器立刻置零,经过一个cp脉冲的时间,第二个触发器的输出也为低电平,数码管熄灭,亮的时间为一个cp脉冲的时间间隔。

②实验电路:实验电路图如图5 所示。

③实验结果:当手控脉冲输出一个脉冲信号时,单次脉冲发生器的输出端的输出一个秒脉冲信号。

(2)用示波器观察单次脉冲发生器工作状态:手控脉冲和系列脉冲都接1kHz 信号,用示波器观察CP、Q1、Q2 的波形。

①实验电路:实验电路图如图6所示。

②用示波器观察得到的实验波形如图7所示。

(a) CP端与Q1端波形图 (b) Q1端与Q2端波形图

整理上述两幅实拍波形图,绘制出CP、Q1、Q2 的波形如下图所示。

6、用D触发器设计一个4位移位寄存器电路并进行实验(移位寄存器要求能实现串行输入,并行输出与串行输出两种方式。

①设计过程:D触发器的输入为前一个触发器的输出,并且所有触发器使用同一个CP脉冲,串行输入的数据是从第一个D触发器输入。

②仿真与实验电路图:仿真与实验电路图如图7所示。

③实验结果:4位数据实现了移位的并行和串行输出。

7、用J-K触发器设计一个双向时钟脉冲产生电路并进行实验

①设计过程:首先把J-K触发器设计成一个T’触发器,输出的结果和结果的非再与cp脉冲求与,就能实现双向时钟脉冲频率相同,相位不同。

②仿真与实验电路图:仿真与实验电路图如图8所示。

③实验结果:得到的双向时钟脉冲波形如图9。

图8

图8

图9

图9

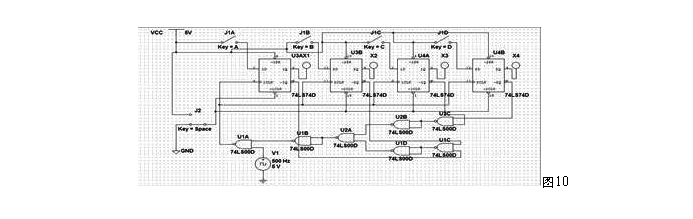

8、用两片74LS74(4个D触发器)实现四路竞赛抢答器电路。输入为四个按钮S4S3S2S1、总清零端、10kHz时钟脉冲。输出为4路分别连接到LED指示灯。

①设计过程:4个D触发器总清零端接在一起,实现同时清零,并且不受cp脉冲的影响,没有抢答时,取4个D触发器输出的非,四个输出求与,得到的结果与cp脉冲求与,由于四个输出都为1,cp脉冲可以顺利加入四个触发器,当一个人抢答时,输出的非是0,四个输出求与为0,阻止了cp脉冲的再次加入,此时改变其他D触发器的状态,都不能改变触发器的输出。实验要求cp脉冲的频率要比较高。

②仿真与实验电路图:仿真与实验电路图如图10所示。

③实验结果:实现了抢答器的功能。

四、实验收获

1. 实验前应检查芯片的逻辑功能。接线时按照引脚功能逐步连接,线的颜色最好有所区分便于识别。

2. 该实验中,应注意触发器不用的清零、置数管脚都要接上相应的电平,防止影响触发器的功能。

3. 测试电路功能时,如果用电平指示器(发光二极管)观察,CP脉冲采用0.5s、1s脉冲信号或用逻辑开关,如果用示波器观察,CP脉冲采用1KHz。

4. 由于实验箱上1Hz、1KHz信号驱动能力有限,可在1KHz信号后接非门以增强驱动能力。

- 时序逻辑电路实验报告

-

时序逻辑电路测试及研究 实验报告(有数据)

实验六时序逻辑电路测试及研究一实验目的1掌握计数器电路分析及测试方法2训练独立进行实验的技能二实验仪器及器件1双踪示波器实验箱2实…

-

时序逻辑电路实验报告

二时序逻辑电路实验题目1试用同步加法计数器74LS161或74LS160和二4输入与非门74LS20构成百以内任意进制计数器并采用…

-

时序逻辑电路实验报告

数字电子技术实验报告实验名称时序逻辑电路班级姓名学号实验日期年月日交报告日期年月日时序逻辑电路一设计要求1设计一个秒脉冲发生器用L…

-

数电实验报告-时序逻辑电路

课程名称数字电子技术基础实验指导老师樊伟敏实验名称时序逻辑电路实验实验类型设计类同组学生姓名一实验目的和要求必填二实验内容和原理必…

-

数字电路 时序逻辑电路——计数器实验实验报告

肇庆学院电子信息与机电工程学院数字电路课实验报告班姓名实验日期实验合作者老师评定实验题目时序逻辑电路计数器实验一实验目的一掌握由集…

-

触发器-时序逻辑电路实验报告

课程名称数字电子技术基础实验指导老师樊伟敏实验名称触发器应用实验实验类型设计类同组学生姓名一实验目的和要求必填二实验内容和原理必填…

-

时序逻辑电路测试及研究 实验报告(有数据)

实验六时序逻辑电路测试及研究一实验目的1掌握计数器电路分析及测试方法2训练独立进行实验的技能二实验仪器及器件1双踪示波器实验箱2实…

-

实验二 组合逻辑电路分析与设计实验报告

实验二组合逻辑电路分析与设计实验报告姓名李凌峰班级13级电子1班学号13348060一实验数据与相应原理图1复习组合逻辑电路的分析…

-

实验一 组合逻辑电路的VHDL设计

组合逻辑电路的VHDL设计学院及班级信工院电子信息工程一班学号20xx550428姓名王尧完成时间20xx年10月11日1实验目的…

-

组合逻辑电路的设计实验报告

基本知识数字电路根据逻辑功能的不同特点可以分成两大类一类叫组合逻辑电路简称组合电路另一类叫做时序逻辑电路简称时序电路组合逻辑电路在…