西工大数字集成电路实验报告 数集实验2(1)

实验二、 反相器(上)

一、 分析电路,解答下面的问题

1. 这个电路是不是反相器,为什么?该门属于有比逻辑,还是无比逻辑,为什么?

是。因为当Vin=1时,下拉网络导通,Vout=0;当Vin=0时,M1截止,Vout经RL充电至1,所以是反相器。

有比逻辑。因为上拉网络始终导通,所以当下拉网络导通时存在竞争,所以是有比逻辑。

2. 计算出这个电路的VOH VOL及VIH VIL。(计算可先排除速度饱和的可能)

Vin=0时,VOH=2.5V

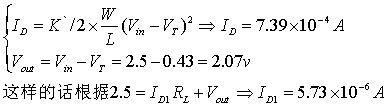

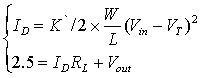

Vin=2.5时,假设NMOS 工作在临界饱和区:

,器件实际工作在线性区

,器件实际工作在线性区

,

,  ,

,

解得:

0.04633V

0.04633V

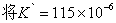

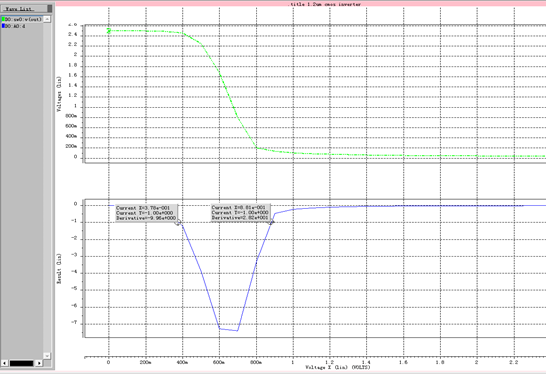

由图得:VOH=2.5V, VOL=0.0356V.

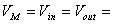

当 时,NMOS 工作在饱和区

时,NMOS 工作在饱和区

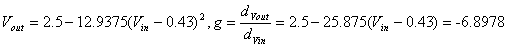

反相器阈值电压 0.7932

0.7932

此时

由图得:VIH=0.881V, VIL=0.0378V.

SP文件:

.TITLE 1.2UM CMOS INVERTER

.options probe

.options tnom=25

.options ingold=2 limpts=30000 method=gear

.options lvltim=2 imax=20 gmindc=1.0e-12

.protect

.lib'C:\synopsys\cmos25_level49.lib' TT

.unprotect

.global vdd

Mn out in 0 0 NMOS W=1.5u L=0.5u *(工艺中要求尺寸最大0.5u)

RL OUT VDD 75k

VDD VDD 0 2.5V

VIN IN 0 0

.DC VIN 0 2.5V 0.1V

.op

.probe dc v(out)

.end

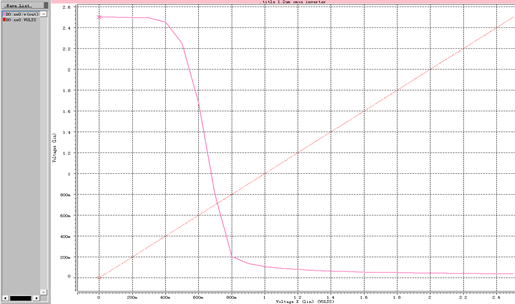

3. 分析电路噪声容限。计算NMH(高电平噪声容限)和NML(低电平噪声容限), 并使用HSPICE画出反相器的VTC曲线。

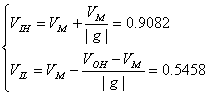

NMH=VOH - VIH=1.619V

NML= VIL- VOL=0.0022V

SP文件:

.TITLE 1.2UM CMOS INVERTER

.options probe

.options tnom=25

.options ingold=2 limpts=30000 method=gear

.options lvltim=2 imax=20 gmindc=1.0e-12

.protect

.lib'C:\synopsys\cmos25_level49.lib' TT

.unprotect

.global vdd

Mn out in 0 0 NMOS W=1.5u L=0.5u *(工艺中要求尺寸最大0.5u)

RL OUT VDD 75k

VDD VDD 0 2.5V

VIN IN 0 0

.DC VIN 0 2.5V 0.1V

.op

.probe dc v(out)

.end

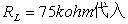

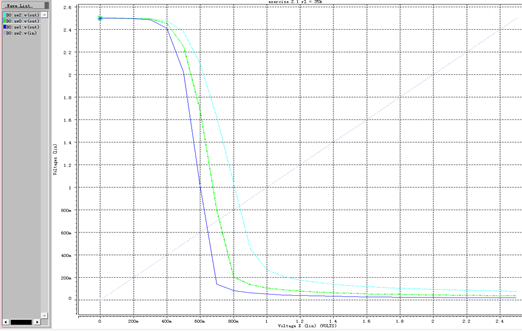

4. 使用HSPICE画出RL=35k,75K,150k三种情况下的VTC。

(从左到右依次为RL=150k,75k, 35k)

SP文件:

.TITLE 1.2UM CMOS INVERTER

.options probe

.options tnom=25

.options ingold=2 limpts=30000 method=gear

.options lvltim=2 imax=20 gmindc=1.0e-12

.protect

.lib'C:\synopsys\cmos25_level49.lib' TT

.unprotect

.global vdd

Mn out in 0 0 NMOS W=1.5u L=0.5u

RL VDD OUT 75k

VDD VDD 0 2.5V

VIN IN 0 0

.DC VIN 0 2.5V 0.1V

.probe V(out)

.probe V(in)

.alter

.TITLE Exercise 2.1 RL = 150k

RL Vdd out 150k

.alter

.TITLE Exercise 2.1 RL = 35k

RL Vdd out 35k

.end

5. 分别计算Vin=0,2.5v时电路消耗的功率。

Vin=0时,P=0

VIN=2.5V时。ID=P=VDD*ID=8.18*10-5W

6. 比较各种RL情况下的VTC, VOH VOL及VIH VIL有怎样的变化。

随着电阻增大, 保持不变,

保持不变, 越来越小。

越来越小。 越来越小,

越来越小, 越来越小

越来越小

7. 高阻抗负载和低阻抗负载所产生的VTC曲线,哪个更理想?

低阻抗负载更理想

二、分析下面电路,并解决问题。

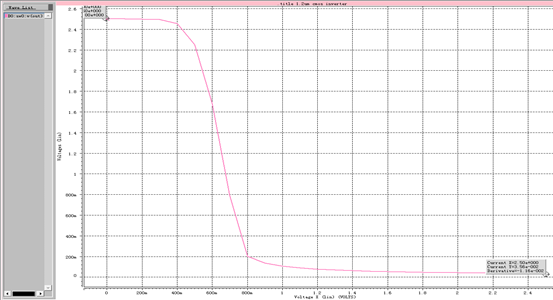

1. 计算tPHL,tPLH及tP。(输入为理想阶跃,考虑速度饱和)

V时,

V时,

=

A

A

=0.69

=0.69 1.17

1.17

3

3

=2.42

=2.42

S

S =0.69

=0.69 75

75

3

3

=1.55

=1.55

S

S

=89.6

=89.6

S

S

2. 上升延迟和下降延迟相同吗?解释为什么有这样的结果。

上升延迟和下降延迟不相同。因为下降沿N管导通与上升沿导通时的电阻相差比较大。N管输出下拉的能力明显更强。

3. 计算电路的静态功耗(Vin=0v,Vin=2.5v)。

当 时,

时,

当 V时,

V时,

=2.5

=2.5 1.417

1.417 =3.541.417

=3.541.417 W

W

4. 计算电路动态功耗,假定门电路的输入信号为合理的最高频率。12.2M,0.225mW

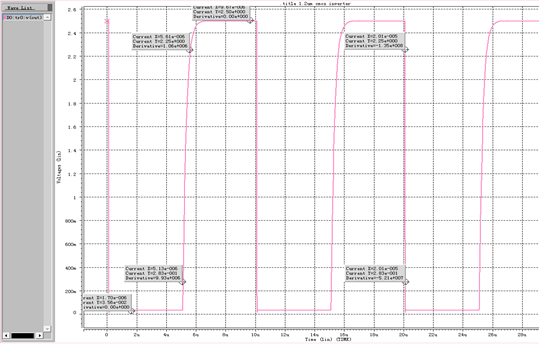

5. 对2的结果进行仿真验证。(tran 仿真;输入加脉冲,上升和下降时间都为5ns)

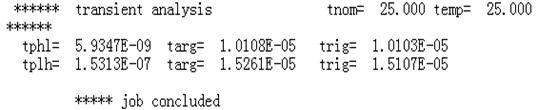

由图得:tPHL= ; tPLH=

; tPLH= s

s

SP文件:

.TITLE 1.2UM CMOS INVERTER

.options probe

.options tnom=25

.options ingold=2 limpts=30000 method=gear

.options lvltim=2 imax=20 gmindc=1.0e-12

.protect

.lib'C:\synopsys\cmos25_level49.lib' TT

.unprotect

.global vdd

Mn out in 0 0 NMOS W=1.5u L=0.5u *(工艺中要求尺寸最大0.5u)

RL OUT VDD 75k

CL OUT 0 3p

VDD VDD 0 2.5V

Vin in 0 PULSE(0 2.5v 100n 5n 5n 5u 10u)

.TRAN 1n 30u

.measure tran TPHL trig v(in) val=1.25 td=1n rise=2 targ v(out)

+val=1.25 td=1n fall=2

.measure tran TPLH trig v(in) val=1.25 td=1n fall=2 targ v(out)

+val=1.25 td=1n rise=2

.probe V(out)

.probe V(in)

.end

附:进行手工计算时可能用到的数据

第二篇:西北工业大学数电实验报告1

实验1 TTL集成逻辑门参数测试

学号: 姓名: 日期:组号:

一、实验目的:

(1)加深了解TTL逻辑门的参数意义。

(2)掌握TTL逻辑门电路的主要参数及测量方法。

(3)认识各种电路及掌握空闲端处理方法。

二、实验设备:

数字电路实验箱,数字双踪示波器,函数信号发生器,数字万用表,74LS00,电位器,电阻。

三、实验原理:

门电路是数字逻辑电路的基本组成单元,目前使用最普遍的双极型数字集成电路是TTL逻辑门电路。

TTL集成电路的使用规则:

(1) 插集成块时,要认清定位标记,不得插反。

(2) 使用电源电压范围为+4.5V~+5.5V。实验中要求使用Vcc=+5V。电源极性不允许接错。

(3) 空闲输入端处理方法。悬空,相当于正逻辑“1”,一般小规模集成电路的数据输入端允许悬空处理。但易受外界干扰,导致电路逻辑功能不正常。因此,对于接有长线的输入端,中规模以上的集成电路和使用集成电路较多的复杂电路,所有控制输入端必须按逻辑要求接入电路,不允许悬空。

(4) 输入端通过电阻接地,电阻值的大小将直接影响电路所处状态。

(5) 输出端不允许并联使用(三态门和OC门除外),否则不仅会使电路逻辑功能混乱,并会导致器件损坏。

(6) 输出端不允许直接接电源Vcc,不允许直接接地,否则会损坏器件。

四、实验内容:

1、 TTL信号的产生

2、 与非门的测试

3、 用74LS00实现逻辑函数:

F=AB

F=A+B

F=A+B

五、实验结果:

F=AB=

F=A+B=

F=A+B=

-

数字电路实验报告模板

组合逻辑电路的设计与调试一、实验目的1、掌握用门电路设计组合逻辑电路的方法。2、掌握组合逻辑电路的调试方法。二、实验器材数字电路实…

-

数电实验报告1

实验一门电路逻辑功能及测试一实验目的1熟悉门电路逻辑功能2熟悉数字电路学习机及示波器使用方法二实验仪器及材料1双踪示波器2器件74…

-

数字电路实验报告

数字电路技术实验报告学号130704002130704010姓名曹兴运丁玉祥组号B8日期20xx1012一实验目的1掌握中规模集成…

-

数字电路实验报告3

暨南大学本科实验报告专用纸课程名称数字逻辑电路实验成绩评定实验项目名称三态门特性研究和典型应用指导教师实验项目编号08060038…

-

数字电路实验报告4

暨南大学本科实验报告专用纸课程名称数字逻辑电路实验成绩评定实验项目名称中规模集成电路功能测试及应用指导教师实验项目编号080600…

-

浙大版电工电子学实验报告12集成运算放大器及应用(一)模拟信号运算电路

课程名称电工电子学实验指导老师实验名称集成运算放大器及应用一模拟信号运算电路实验报告一实验目的1了解集成运算放大器的基本使用方法和…

-

电路实验报告

数字电路实验报告姓名:***学号:***学院:信息学院专业:计算机科学与技术指导教师:***协助指导教师:20XX年12月28日实…

-

数字电路实验报告4

暨南大学本科实验报告专用纸课程名称数字逻辑电路实验成绩评定实验项目名称中规模集成电路功能测试及应用指导教师实验项目编号080600…

-

西工大数电实验报告_实验一TTL集成逻辑门电路参数测试

实验一TTL集成逻辑门电路参数测试姓名同组一实验目的1加深了解TTL逻辑门的参数意义2掌握TTL逻辑门电路的主要参数及测量方法3认…

-

集成门电路功能测试实验报告

集成门电路功能测试实验报告一实验预习1逻辑值与电压值的关系2常用逻辑门电路逻辑功能及其测试方法3硬件电路基础实验箱的结构基本功能和…