verilog电子钟实验报告

深 圳 大 学 实 验 报 告

课程名称:硬件描述语言与逻辑综合

实验项目名称:电子时钟Verilog HDL 的设计与仿真 学院:电子科学与技术学院

专业:微电子科学与工程

指导教师:刘春平

报告人:曾荣学号:2013800527班级:微电2班

实验报告提交时间:

一、实验目的

1、 掌握Quartus ii软件的使用方法以及各种语句使用方法;

2、 学习如何运用verilog HDL设计简单的数字电路

3、 掌握基本时序逻辑仿真的实现,以及上机运行的操作;

4、 掌握Verilog HDL中模块运用的思想,为以后的实践打下基础。 二、实验原理

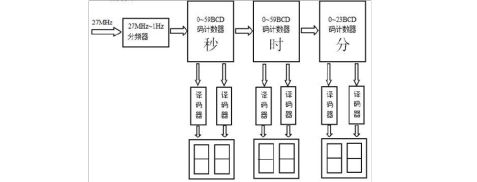

数字时钟模块组织结构如图所示:

数码管

显示模块

分频

模

块

计时模块

实验原理图如上图所示。所谓的时钟,其实本质上就是计数器。以开发板上的晶振时钟27MHZ作为时间基准。然后通过分频模块(计数器)进行分频,得到1Hz的脉冲信号作为1秒的信号脉冲,然后用模60的计数器构成秒的计数单元。每记60下就自动清零且产生进位信号。将这个进位信号作为分的计数器的使能信号,其中,分计数器也是模为60的计数器。这里的计数器都是由模10和模6 组成的BCD码的计数器。个位和十位分别是一个四位的数字。同理,每记满60,分计数器就会产生一个进位信号,这个进位信号作为小时的使能信号。小时的计数器就是模24的BCD计数器。注意,这里的整个电路都是用1HZ的频率作为时间脉冲的,也就是说,这个电路是同步时序的电路。通过使能,来控制各个部分的时序逻辑。当在调时状态的时候,时钟每完成一个周期,无论是分钟还是小时,就向前加1。最后,将分钟和小时通过译码器连接到数码管。将秒直接连接到LED灯,完成整个工程的基本功能。每个计数器要配两个译码器模块,以保证数值能正确的显示到DE2板上。

三、实验过程(附源代码)

本实验需要用到四个模块,分别是27MHz的分频器模块,模为60的加法计数器模块,模为24的加法计数器模块以及七段数码管的译码器模块。由四个模块和主函数构成整个源程序。

源程序所有代码如下:

Module

clock(reset,stop,clk,load_sec,load_min,load_hour,data,de_sec1,de_sec2, de_min1,de_min2,de_hour1,de_hour2);

output[6:0] de_sec1,de_sec2,de_min1,de_min2,de_hour1,de_hour2; input reset,clk,load_sec,load_min,load_hour,stop;

input[7:0] data;

wire[7:0] sec,min,hour;

wire one_second,sec_min,min_hour;//定义变量和数据类型等

divider FP(one_second,stop,clk);//27MHZ分频成1HZ

//计时部分

count60 miao(sec,sec_min,data,load_sec,1,reset,one_second);

count60 fen(min,min_hour,data,load_min,sec_min,reset,one_second); count24 shi(hour,data,load_hour,min_hour,reset,one_second);

//七位数码管显示部分

decode4_7 sec_1(de_sec1,sec[3:0]);

decode4_7 sec_2(de_sec2,sec[7:4]);

decode4_7 min_1(de_min1,min[3:0]);

decode4_7 min_2(de_min2,min[7:4]);

decode4_7 hour_1(de_hour1,hour[3:0]);

decode4_7 hour_2(de_hour2,hour[7:4]);

endmodule

//divider代码,分频器模块

module divider(one_second,reset,clk);

output one_second;

input reset,clk;

reg one_second;

reg[23:0] cnt;

always@(posedge clk)

begin

if(reset)

begin

cnt<=0;

one_second<=0;

end

else if(cnt===13499999)

begin

cnt<=0;

one_second<=~one_second;

end

else

cnt<=cnt+1;

end

endmodule

//代码结束

//count60代码,秒、分计数模块

module count60(qout,cout,data,load,cin,reset,clk);

output[7:0] qout;

output cout;

input[7:0] data;

input load,cin,clk,reset;

reg[7:0] qout;

always @(posedge clk) //clk 上升沿时刻计数

begin

if (reset) qout<=0; //同步复位

else if(load) qout<=data; //同步置数

else if(cin)

begin

if(qout[3:0]==9) //低位是否为9,如果是则

begin

qout[3:0]<=0; //回0,并判断高位是否为5 if (qout[7:4]==5) qout[7:4]<=0;

else

qout[7:4]<=qout[7:4]+1; //高位不为5,则加1 end

else //低位不为9,则加1

qout[3:0]<=qout[3:0]+1;

end

end

assign cout=((qout==8'h59)&cin)?1:0; //产生进位输出信号 endmodule

//代码结束

//count24代码,时计数模块

module count24(qout,data,load,cin,reset,clk);

output[7:0] qout;

input[7:0] data;

input load,cin,clk,reset;

reg[7:0] qout;

always @(posedge clk) //clk 上升沿时刻计数

begin

if (reset) qout<=0; //同步复位

else if(load) qout<=data; //同步置数

else if(cin)

begin

if (qout[7:4]==2)

begin

if(qout[3:0]==3) qout<=0;

else

qout[3:0]<=qout[3:0]+1;

end

else

begin

if(qout[3:0]==9) //低位是否为9,是则

begin

qout[3:0]<=0; //回0

qout[7:4]<=qout[7:4]+1; //高位不为5,则加1 end

else //低位不为9,则加1

qout[3:0]<=qout[3:0]+1;

end

end

end

endmodule

//结

//decode4_7代码开始,七位数码管显示模块 module decode4_7(decodeout,indec);

output[6:0] decodeout;

input[3:0] indec;

reg[6:0] decodeout;

always @(indec)

begin

case(indec) //用case 语句进行译码,共阴

4'd0:decodeout=7'b1000000;

4'd1:decodeout=7'b1111001;

4'd2:decodeout=7'b0100100;

4'd3:decodeout=7'b0110000;

4'd4:decodeout=7'b0011001;

4'd5:decodeout=7'b0010010;

4'd6:decodeout=7'b0000010;

4'd7:decodeout=7'b1111000;

4'd8:decodeout=7'b0000000;

4'd9:decodeout=7'b0010000;

default: decodeout=7'bz;

endcase

end

endmodule

//结束

四、时序仿真结果

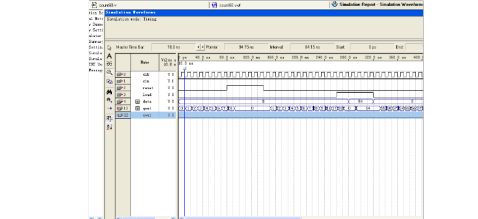

1、分频器时序仿真

源代码:

module divider(one_second,reset,clk);

output one_second;

input reset,clk;

reg one_second;

reg[23:0] cnt;

always@(posedge clk)

begin

if(reset)

begin

cnt<=0;

one_second<=0;

end

else if(cnt===5)//13499999改成5,为了使波形能够在时序仿真中顺利出现

begin

cnt<=0;

one_second<=~one_second;

end

else

cnt<=cnt+1;

end

endmodule

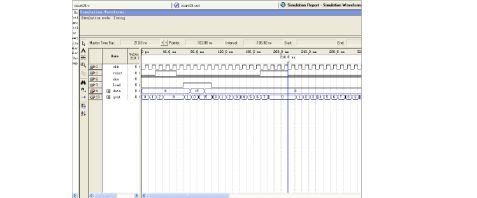

2、模为60的加法计数器模块仿真

源程序:

module count60(qout,cout,data,load,cin,reset,clk);

output[7:0] qout;

output cout;

input[7:0] data;

input load,cin,clk,reset;

reg[7:0] qout;

always @(posedge clk) //clk 上升沿时刻计数

begin

if (reset) qout<=0; //同步复位

else if(load) qout<=data; //同步置数

else if(cin)

begin

if(qout[3:0]==9) //低位是否为9,是则

begin

qout[3:0]<=0; //回0,并判断高位是否为5 if (qout[7:4]==5) qout[7:4]<=0;

else

qout[7:4]<=qout[7:4]+1; //高位不为5,则加1 end

else //低位不为9,则加1

qout[3:0]<=qout[3:0]+1;

end

end

assign cout=((qout==8'h59)&cin)?1:0; //产生进位输出信号 endmodule

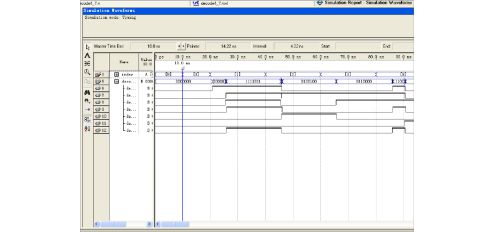

3、模为24的加法计数器模块仿真

源程序:module count24(qout,data,load,cin,reset,clk);

output[7:0] qout;

input[7:0] data;

input load,cin,clk,reset;

reg[7:0] qout;

always @(posedge clk) //clk 上升沿时刻计数 begin

if (reset) qout<=0; //同步复位

else if(load) qout<=data; //同步置数

else if(cin)

begin

if (qout[7:4]==2)

begin

if(qout[3:0]==3) qout<=0;

else

qout[3:0]<=qout[3:0]+1;

end

else

begin

if(qout[3:0]==9) //低位是否为9,是则 begin

qout[3:0]<=0; //回0

qout[7:4]<=qout[7:4]+1; //高位不为5,则加1 end

else //低位不为9,则加1

qout[3:0]<=qout[3:0]+1;

end

end

end

endmodule

4、七段数码管译码器模块

源程序:module decode4_7(decodeout,indec);

output[6:0] decodeout;

input[3:0] indec;

reg[6:0] decodeout;

always @(indec)

begin

case(indec) //用case 语句进行译码 4'd0:decodeout=7'b1000000; 4'd1:decodeout=7'b1111001; 4'd2:decodeout=7'b0100100; 4'd3:decodeout=7'b0110000; 4'd4:decodeout=7'b0011001; 4'd5:decodeout=7'b0010010; 4'd6:decodeout=7'b0000010; 4'd7:decodeout=7'b1111000; 4'd8:decodeout=7'b0000000; 4'd9:decodeout=7'b0010000; default: decodeout=7'bz;

endcase

end

endmodule

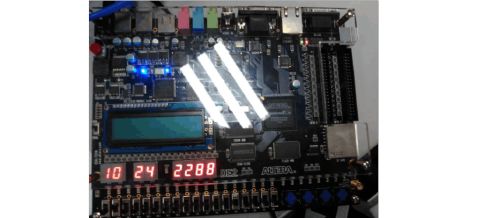

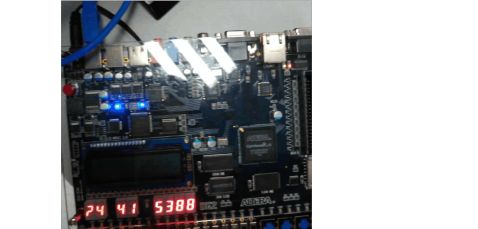

五、上机测试结果

程序烧录到DE2板上后,由13个拨码开关控制整个程序的进行,SW17是置0功能,SW13是暂停功能,SW14到SW16则分别是三个计数器模块的置数开关,置数数据由SW0到SW7输入。本实验中只用到了HEX2到HEX7共6个七段数码管,实现了一个数字时钟该有的所有功能

六、实验总结

本实验实现了一个个模块调用程序的调试、时序仿真、引脚分配、烧录到DE2板的一系列操作。通过实验,我更好地掌握了Quartus ii软件的操作技巧以及各种语句使用方法,同时将课堂上所学的书面知识,应用到实践中来,更好地掌握了知识。不过在试验过程中,由于有些语法用错,导致实验一度仿真失败,后来经过同学提醒,终于搞定仿真。通过实验,我认识到自己实践能力的不足,对知识也掌握得不够熟悉,以后要好好学习才是。同时也认识到,verilog HDL是我们以后硬件设计的基础,和其他设计软件相辅相成。

第二篇:《EDA综合设计与实践》课程设计-用Verilog HDL设计电子钟

广东工业大学实验报告

信息工程学院 通信工程 专业 04 班 成绩评定_______

学号 3205002894 姓名张凤珠 教师签名_______

实验题目 用Verilog HDL设计电子钟 第 17 周至 第 17 周

一、课程设计目的和要求

目的:

1. 学会使用quantusⅡ软件(编译、仿真等),并利用它进行设计一些简单的数字电路;

2. 利用实验室提供的GW48 SOPC系统主板,结合quantusⅡ软件实现电子钟的功能显示。

要求:

电子钟应实现如下功能:

1.时钟显示功能:,该电子钟正常显示小时、分钟、秒,各用2位数码管(共6位数码管)显示范围为0—23时59分59秒,分辨率为1秒,包括启动与停止。

2.校时功能:包括小时校准和分钟校准。

3.跑表:包括跑表清零、启动计时、停止及继续计时功能。

二、实验器件

实验室提供的GW48 SOPC系统主板实验箱

三、设计方案和源程序代码

首先分析电子钟要实现的三个功能,然后确定它的基本结构,因为设计时电子钟的三个基本功能都要用到数码管显示,考虑到三者为了避免竞争数码管资源的问题,因此设计时电子钟有3个主要输入按键K1、K2、K3,分别为时间显示、校时功能、跑表的启动,而且是当任一个按键按下,其余两个键都无效,即此时只有按下的键才有效,执行该键所控制功能的启动。

其次,各个功能模块的设计。A 、对于时间显示模块中,涉及到的是时分秒各个计数器的设计 ,“秒计数器”采用60进制计数器,每累计60秒,发出一个“分脉冲”信号,该信号将被送到“分计数器”。“分计数器”采用60进制计数器,每累计60分,发出一个“分脉冲”信号,该信号被送到“时计数器”。“时计数器”采用24进制计数器,可实现24小时的累计计数。 B 、对于校时模块,同样用到了上述的时分计数器,不过只是能实现校时分钟和小时功能,分别用K4、K5键控制,做法是每按下一次键,对应的计数器加一。C、 最后是跑表模块,这相对于前面两个模块较为复杂,它有计时复位、启动和计时停止三个功能,分别用K6、K8、K7按键控制,这里用到了毫秒、秒、分钟计数器,其中“毫秒计数器”采用100进制计数器,每累计100毫秒产生一个“秒脉冲”信号,该信号将作为“秒计数器”的时钟脉冲,其余同A所述。百分秒、秒和分钟信号用七段LED显示。而复位信号是高电平有效,可以对整个跑表同步清0;当启动/停止为高电平时跑表开始计时,为低电平时停止计时,变高后在原来的数值基础上再计数。

最后,就是整体的综合。包括每个模块用到的时钟设置、按键显示模块和确定输入输出参数;本次课程设计采用了一个输入主时钟源4096HZ,其余各个模块用到的时钟信号从此时钟源分频得到,因此专门设置了一个分频小模块。

源程序代码如下:

module main(k1,k2,k3,k4,k5,k6,k7,k8,clk_4096,LED1,LED2,LED3,LED4,LED5,LED6);

input k1,k2,k3,k4,k5,k6,k7,k8,clk_4096;

output[3:0]LED1,LED2,LED3,LED4,LED5,LED6;

reg [3:0] LED1,LED2,LED3,LED4,LED5,LED6;

reg [7:0] hour,minute,second;

`define hour1 hour[3:0]

`define hour2 hour[7:4]

`define min1 minute[3:0]

`define min2 minute[7:4]

`define sec1 second[3:0]

`define sec2 second[7:4]

reg [15:0] j1,j2,j3;

reg clk1,clk2,clk3;

always @(posedge clk_4096) //输入4096HZ时钟源

begin

if(j1==40)

begin

j1<=0;

clk1<=~clk1; //100HZ

end

else

j1<=j1+1;

if(j2==4095)

begin

j2<=0;

clk2<=~clk2; //1HZ

end

else

j2<=j2+1;

if(j3==7)

begin

j3<=0;

clk3<=~clk3; //512HZ

end

else

j3<=j3+1;

end

//跑表

reg [7:0] missecondrun, secondrun,miurun;

reg runnings,mis,sec;

always@(posedge clk1)

begin

if(k6) //复位

begin

missecondrun[7:0]<=8'd0;

secondrun[7:0]<=8'd0;

miurun[7:0]<=8'd0;

runnings<=0;

end

if(k7) //停止

begin

runnings<=0;

end

if(k8) //运行

runnings<=1;

if(runnings)

begin

if(missecondrun[3:0]==9) // 1/100秒

begin

if(missecondrun[7:4]==9)

begin

missecondrun[7:0]<=0; //如果为99时,转为0

mis<=1; //产生进位提示

end

else

begin

missecondrun[3:0]<=0; //如果只是个位为9时,十位加1,个位为0

missecondrun[7:4]<=missecondrun[7:4]+1;

end

end

else

missecondrun[3:0]<=missecondrun[3:0]+1; //如果个位不为0时,个位加1,十位不变

if(mis) //当进位为1时才进行一次加1

begin

mis<=0;

if(secondrun[3:0]==9) //秒

begin

if(secondrun[7:4]==5)

begin

secondrun[7:0]<=0; //如果为59时,转为0

sec<=1; //产生进位提示

end

else

begin

secondrun[3:0]<=0;

secondrun[7:4]<=secondrun[7:4]+1;//如果只是个位为9时,十位加1,个位为0

end

end

else

secondrun[3:0]<=secondrun[3:0]+1; //如果个位不为0时,个位加1,十位不变

end

if(sec) //当进位为1时才进行一次加1

begin

sec<=0;

if(miurun[3:0]==9) //分钟

begin

if(miurun[7:4]==5)

begin

miurun[7:0]<=0;

end

else

begin

miurun[3:0]<=0;

miurun[7:4]<=miurun[7:4]+1;

end

end

else

miurun[3:0]<=miurun[3:0]+1;

end

end

end

//时钟显示

reg secondin,minutein;

always@(posedge clk2)

begin

if(`sec2==5&&`sec1==9)

begin

`sec2<=0;

`sec1<=0;

secondin<=1;

end

else

begin

if(`sec1==9)

begin

`sec1<=0;

`sec2<=`sec2+1;

end

else `sec1<=`sec1+1;

end

if(secondin)

begin

secondin<=0;

if(`min2==5&&`min1==9)

begin

`min2<=0;

`min1<=0;

minutein<=1;

end

else

begin

if(`min1==9)

begin

`min1<=0;

`min2<=`min2+1;

end

else `min1<=`min1+1;

end

end

if(minutein)

begin

minutein<=0;

if(`hour2==3&&`hour1==2)

begin

`hour2<=0;

`hour1<=0;

end

else

begin

if(`hour1==9)

begin

`hour1<=0;

`hour2<=`hour2+1;

end

else `hour1<=`hour1+1;

end

end

if(k4)//校时分钟

begin

if(minute[7:4]==5)

begin

if(minute[3:0]==9)

begin

minute[7:0]<=0;

end

else

minute[3:0]<=minute[3:0]+1;

end

else

begin

if(minute[3:0]==9)

begin

minute[3:0]<=0;

minute[7:4]<=minute[7:4]+1;

end

else

minute[3:0]<=minute[3:0]+1;

end

end

if(k5)// 校时小时

begin

if(`hour2==2)

begin

if(`hour1==3)

begin

`hour2<=0;

`hour1<=0;

end

else

`hour1<=`hour1+1;

end

else

begin

if(`hour1==9)

begin

`hour1<=0;

`hour2<=`hour2+1;

end

else

`hour1=`hour1+1;

end

end

end

// 按键显示模块

reg k1_rst,k2_rst,k3_rst;

always@(posedge clk3)

begin

if(k1)

begin

k1_rst<=1;

k2_rst<=0;

k3_rst<=0;

end

if(k2)

begin

k1_rst<=0;

k2_rst<=1;

k3_rst<=0;

end

if(k3)

begin

k1_rst<=0;

k2_rst<=0;

k3_rst<=1;

end

if(k1_rst) //时间显示

begin

LED1<=second[3:0];

LED2<=second[7:4];

LED3<=minute[3:0];

LED4<=minute[7:4];

LED5<=hour[3:0];

LED6<=hour[7:4];

end

if(k2_rst) //校时

begin

LED3<=minute[3:0];

LED4<=minute[7:4];

LED5<=hour[3:0];

LED6<=hour[7:4];

end

if(k3_rst) //跑表显示

begin

LED1<=missecondrun[3:0];

LED2<=missecondrun[7:4];

LED3<=secondrun[3:0];

LED4<=secondrun[7:4];

LED5<=miurun[3:0];

LED6<=miurun[7:4];

end

end

endmodule

四、修改后设计方案

由于本课程设计用到的主时钟源是实验箱上的4096HZ,而真正用到的时钟是1HZ、100HZ、512HZ,分别用于时间显示(包含校时)、跑表、按键显示;这些时钟都从主频分频得到,而从主频4096HZ到1HZ,要经过4096次分频,分频计数太大,主频与分频后的时钟频率相差太大,不利于程序仿真,所以建议使用较低的主频,如1024HZ主频;

原设计中用到多个按键控制,而每个按键都只是只有一种控制功能,缺乏灵活性,所以修改后将按键设置为模式键,即每次按下键都实现不同功能显示,可用状态机来实现设计,这里只用到三个按键。

五、实验结果和数据处理

按下按键K1,电子钟正常显示时间,再按下键,停止显示。

按下按键K2,进入校时状态:按下K4键,进行校准分钟,每按下一次K4键,分钟计数器加一;按下K5键,进行小时校准,每按下一次K5键,小时计数器加一;最后再若按下K2键,停止校时。

按下按键K3,进入跑表计时功能:按下K6键,复位;按下K8键,开始计时;按下K7键,停止计时;

六、心得体会

本次课程设计,我花了大概三天时间来完成(不包括报告),虽然没有达到教程安排的五天时间,但是我却是所花时间在课程设计上比较多的少数人之一,不过总算也完成了作品,尽管不是很完美,功能也不是很多,但是心里还是蛮有成就感的!

当然,完成一次课程设计都不是很容易的!首先确定了自己做电子钟的设后,就开始着手写程序;刚开始,确定实现的设计目标是多功能的电子钟,而且还确定了每个功能用一个模块来写,最后编写一个主模块,采取调用模块的形式调用所写的各个功能模块,这样想法构思是很不错的;但是限于自己所学知识不是很牢固,也不是很深入,写Verilog HDL 程序也比较少,实践能力还不够,所以当我好不容易编写好各个功能模块后,最终在编写主程序时却遇上了很多问题,特别是在编写调用模块时,出现了重重关卡,原来想法总比做的来的简单!这期间我也有问过同学,可是由于碍于时间的问题,最终决定还是放弃这种调用多个模块的好方法,转为全部在一个模块实现的正常形式。确定了总体版面后,就将原先全部模块综合在一个模块之内,可是一经编译,还是出现了很多意想不到的错误,编译不成功;一切又得从头检查起,经过多方面的努力,最终得以完成!不过,却比预想的电子钟少了一些功能。

从这次课程设计中,我学到了很多东西,也发现了自己的不足,特别是发现自己不够有恒心,这与搞技术开发的锲而不舍的精神相违背,所以希望自己在这方面都加强些,编程能力也有待进一步加强;多进行自我实践,多请教老师同学,争取自己能上一个台阶!

-

Verilog实验报告(电子)

西安邮电大学VerilogHDL大作业报告书学院名称学生姓名专业名称班级电子工程学院电子信息工程实验一异或门设计一实验目的1熟悉M…

-

Verilog 实验报告

实验一简单组合逻辑电路的设计一实验要求1用verilogHDL语言描写出简单的一位数据比较器及其测试程序2用测试程序对比较器进行波…

-

北航verilog实验报告

北京航空航天大学电子电路设计数字部分实验报告实验一简单组合逻辑设计2实验二简单分频时序逻辑电路的设计3一实验目的1掌握最基本组合逻…

-

Verilog实验报告

实验报告格式要求一实验报告内容包括1实验名称2实验目的3实验仪器及编号写明仪器名称型号编号4实验原理简单叙述有关实验原理包括电路图…

-

Verilog HDL 实验报告

实验一Modelsim仿真软件的使用一实验目的1熟悉Modelsim软件2掌握Modelsim软件的编译仿真方法3熟练运用Mode…

-

北航verilog实验报告

北京航空航天大学电子电路设计数字部分实验报告实验一简单组合逻辑设计2实验二简单分频时序逻辑电路的设计3一实验目的1掌握最基本组合逻…

-

Verilog期末实验报告—波形发生器

深圳大学实验报告课程名称:Verilog使用及其应用实验名称:频率可变的任意波形发生器学院:电子科学与技术学院专业:电子科学与技术…

-

verilog四位BCD加法器实验报告

1实验目的进一步熟悉modelsim仿真工具的使用方法学会设计验证的方法和流程编写一个4位BCD加法器并且用modelsim对其仿…

-

Verilog HDL 实验报告

实验一Modelsim仿真软件的使用一实验目的1熟悉Modelsim软件2掌握Modelsim软件的编译仿真方法3熟练运用Mode…

-

Verilog实验报告(电子)

西安邮电大学VerilogHDL大作业报告书学院名称学生姓名专业名称班级电子工程学院电子信息工程实验一异或门设计一实验目的1熟悉M…

-

51单片机电子时钟课程设计报告

JINGCHUUNIVERSITYOFTECHNOLOGY单片机原理及应用课程设计报告题目电子时钟专业电气工程及其自动化班级20x…