数据采集系统实验报告AD模块的设计

A/D采集模块设计

学院名称: 电气信息工程学院

专 业: 测控技术与仪器

班 级: 07测控

姓 名:

学 号:

指导教师:

20##年12月20日

目录

一、实验目的

二、实验原理

1.ADC0809的原理及原理图

2.AD574A的原理及原理图

三、实验过程

四、实验结果

五、结束语

六、参考文献

一、实验目的:

学习用状态机实现对ADC0809,AD574A等A/D转换器的采样控制。

二、实验原理:

1.ADC0809的原理及原理图

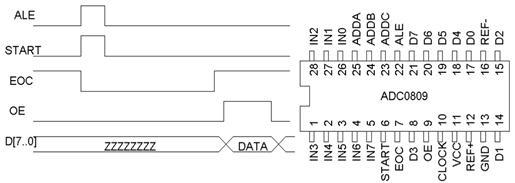

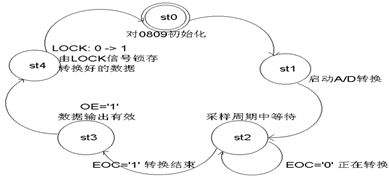

图2.1和图2.2分别是ADC0809的工作时序图以及采样状态图。时序图中,START为转换启动控制信号,高电平有效,ALE为模拟信号输入宣统端口地址所存信号,上升沿有效;一旦START有效后,状态信号EOC变为低电平,表示进入转换状态,转换时间约为100us。转换结束后,EOC将变为高电平。此后外部控制可使OE由低电平变为高电平(输出有效),此时,ADC0809的输出数据总线D[7…0]从原来的高阻态变为输出数据有效。

由状态图也可看到,状态st2中需要对ADC0809工作状态信号EOC进行测试,如果为低电平,表示转换没有结束,仍需要停留在st2状态中等待,直到变成高电平后才说明转换结束,在下一个时钟脉冲到来时转向状态st3。在状态st3,由状态机向ADC0809发出转换好的8位数据输出允许命令,这一状态周期同时可作为数据输出稳定周期,以便能在下一状态中向锁存器中锁入可靠的数据。在状态st4,由状态机向FPGA中的锁存器发出锁存信号(LOCK的上升沿),将ADC0809的输出数据进行锁存。

图2.1 ADC0809工作时序

图2.2控制ADC0809采样状态图

2.AD574A的原理及原理图

(1)12位A/D转换器芯片AD574A特点:芯片内部包含微机接口逻辑和三态输出缓冲器,可以直接与8 位、12 位或16 位;输出可以是12位一次读出或分两次读出,先读高8位,再读低4位;输入电压可有单极性和双极性两种;对外可提供一个+10V基准电压,最大输出电流1.5mA;有较宽的温度使用范围。

(2) 芯片引脚功能如图2.4所示:

图2.4 AD574A引脚功能

(3)启动转换的时序:

在启动转换后,各控制信号不起作用,只有STS信号标志工作状态。读出数据也同样由CE来启动,读时序如下图2.5所示:

图

2.5 AD574A

读时序图

图

2.5 AD574A

读时序图

三、实验过程

本次实验是采用QuartusⅡ软件进行编译与仿真。步骤如下:

1. 打开QuartusⅡ6.0软件,进入QuartusⅡ欢迎界面。

2. 鼠标单击File---new,出现如下窗口,选择“VHDL FILE”,在弹出的窗口中输入VHDL程序文件。

3. 输入完毕后,点击保存,由于接下来步骤繁琐,我就把它简述为保存并新建工程。

4. 接下来就进行编译,选择下图processing菜单中的start complilation命令。若有VHDL程序有错误,则编译不会完成并弹出对话框提示如下图所示,单击确定后,手动排除错误。方法是在红色的错误提示上双击鼠标左键,软件会自动找到可能是错误的地方或者软件认为不符合规范的地方,排除错误后,再重新执行编译过程。

5. 完成编译后方可进行时序波形的仿真,也称为软件仿真,仿真的前提条件是要有波形文件。仿真的过程可以分为新建波形文件,添加节点,设置仿真时间长度,绘制波形,存储文件,启动仿真等步骤。

6. 附上程序清单:

(1)ADC0809程序清单

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY vhdl1 IS

PORT(D : IN STD_LOGIC_VECTOR(7 DOWNTO 0);

--来自0809转换好的8位数据

CLK : IN STD_LOGIC; --状态机工作时钟

EOC : IN STD_LOGIC; --转换状态指示,低电平表示正在转换

ALE : OUT STD_LOGIC; --8个模拟信号通道地址锁存信号

START : OUT STD_LOGIC; --转换开始信号

OE : OUT STD_LOGIC; --数据输出3态控制信号

ADDA : OUT STD_LOGIC; --信号通道最低位控制信号

LOCK0 : OUT STD_LOGIC; --观察数据锁存时钟

Q : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)); --8位数据输出

END vhdl1;

ARCHITECTURE behav OF vhdl1 IS

TYPE states IS (st0, st1, st2, st3,st4) ; --定义各状态子类型

SIGNAL current_state, next_state: states :=st0 ;

SIGNAL REGL : STD_LOGIC_VECTOR(7 DOWNTO 0);

SIGNAL LOCK : STD_LOGIC; -- 转换后数据输出锁存时钟信号

BEGIN

ADDA <= '1';--当ADDA<='0',模拟信号进入通道IN0;当ADDA<='1',则进入通道IN1

Q <= REGL; LOCK0 <= LOCK ;

COM: PROCESS(current_state,EOC,CLK) BEGIN --规定各状态转换方式

IF CLK'EVENT AND CLK='1'

THEN

CASE current_state IS

WHEN st0=>ALE<='0';START<='0';LOCK<='0';OE<='0';

next_state<= st1; --0809初始化

WHEN st1=>ALE<='1';START<='1';LOCK<='0';OE<='0';

next_state<= st2; --启动采样

WHEN st2=> ALE<='0';START<='0';LOCK<='0';OE<='0';

IF (EOC='1') THEN next_state<= st3; --EOC=1表明转换结束

ELSE next_state<= st2; END IF ; --转换未结束,继续等待

WHEN st3=> ALE<='0';START<='0';LOCK<='0';OE<='1';

next_state<= st4;--开启OE,输出转换好的数据

WHEN st4=> ALE<='0';START<='0';LOCK<='1';OE<='1'; next_state<= st0;

WHEN OTHERS =>next_state<= st0; END CASE ;

END IF;

END PROCESS COM ;

REG: PROCESS (CLK)

BEGIN

IF (CLK'EVENT AND CLK='1') THEN current_state<=next_state; END IF;

END PROCESS REG ; -- 由信号current_state将当前状态值带出此进程:REG

LATCH1: PROCESS (LOCK) -- 此进程中,在LOCK的上升沿,将转换好的数据锁入

BEGIN

IF LOCK='1' AND LOCK'EVENT THEN REGL <= D ; END IF;

END PROCESS LATCH1 ;

END behav;

(2)AD574A程序清单:LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY ADCINT1 IS

PORT(D:IN STD_LOGIC_VECTOR(11 DOWNTO 0);

CLK:IN STD_LOGIC;

STS:IN STD_LOGIC;

CE:OUT STD_LOGIC;

CS:OUT STD_LOGIC;

RCN:OUT STD_LOGIC;

A0:OUT STD_LOGIC;

SL: OUT STD_LOGIC;

LOCK0:OUT STD_LOGIC;

Q:OUT STD_LOGIC_VECTOR(11 DOWNTO 0));

END ENTITY ADCINT1;

ARCHITECTURE behav OF ADCINT1 IS

TYPE states IS(st0,st1,st2,st3,st4,ST5);

SIGNAL current_state,next_state:states:=st0;

SIGNAL REGL :STD_LOGIC_VECTOR(11 DOWNTO 0);

SIGNAL LOCK :STD_LOGIC;

BEGIN

A0<='0';

SL<='1';

Q<=REGL;

LOCK0<=LOCK;

COM:PROCESS(current_state,STS)

BEGIN

IF(CLK'EVENT AND CLK='1') THEN

CASE current_state IS

WHEN st0=>CE<='0';CS<='0';RCN<='0';LOCK<='0';

next_state<=st1;

WHEN st1=>CE<='1';CS<='0';RCN<='0';LOCK<='0';

next_state<=st2;

WHEN st2=>CE<='0';CS<='1';RCN<='1';LOCK<='0';

IF(STS='0')THEN next_state<=st3;

ELSE next_state<=st2;

END IF;

WHEN st3=>CE<='0';CS<='0';LOCK<='0';RCN<='1';

next_state<=st4;

WHEN st4=>CE<='1';CS<='0';LOCK<='0';RCN<='1';

next_state<=st5;

WHEN st5=>CE<='1';CS<='0';LOCK<='1';RCN<='1';

next_state<=st0;

WHEN OTHERS=>next_state<=st0;

end case;

END IF;

end process COM;

REG:PROCESS(CLK)

BEGIN

IF(CLK'EVENT AND CLK='1') THEN current_state<=next_state;

END IF;

END PROCESS REG;

LATCH1:PROCESS(LOCK)

BEGIN

IF LOCK='1' AND LOCK'EVENT THEN REGL<=D;END IF;

END PROCESS LATCH1;

END behav;

四、实验结果

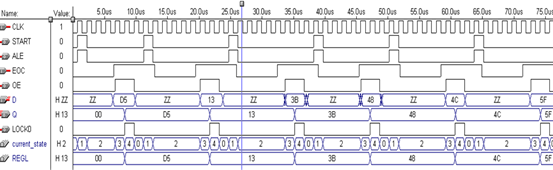

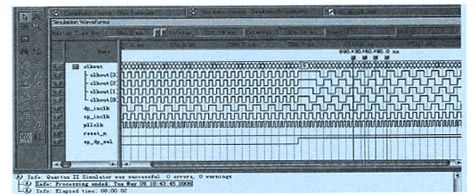

图4 ADC0809采样状态机工作时序

五、结束语

这次的数据采集系统课程设计,让我们有机会将课堂上所学的理论知识运用到实际中。并通过对知识的综合利用,进行必要的分析、比较,从而进一步验证了所学的理论知识。同时,这次课程设计也为我们以后的学习打下基础,指导我们在以后的学习,多动脑的同时,要善于自己去发现并解决问题。

通过这次实验,我学会了用状态机对ADC0809和AD574A转换器的采样控制。在实验的过程中遇到了很多困难,但通过查书本和查资料都得到了解决。所以,在学习的过程中遇到困难并不可拍,我可以通过努力将问题一一克服。

六、参考文献

[1]《数据采集与处理技术》马明建编著西安交通大学出版社 2005

[2]《EDA技术与VHDL》潘松,黄继业编著清华大学出版社 2004

第二篇:高速数据采集系统中时钟模块的设计与实现

《自动化技术与应用》2007年第26卷第6期

经验交流

Tbchnica|COmmunications

.__JL

同

口

速数据采集系统中时钟模块的设计与实现

王红林,王

勇,植

勇

(四川大学电子信息学院,四川成都,610064)

摘要:介绍了一种运用Altera公司的CycloneII芯片EP2C35和TI公司的ADs2807为核心的基于PcI多通道高速数据采集系统

的设计结构。通过对并行时间交替采样结构和原理的分析…,重点描述了应用FPGA资源实现精准移相时钟模块的设计,从而实现了能满足整个系统要求的高精时钟模块。

关键字:高速数据采集;FPGA;交替时间采样;移相时钟中图分类号:TP247

文献标识码:B

文章编号:1003—7241(2007)06—0102—03

DeSignOf

a

PhaSeShiftingCIOCkintheHignSpeedDataACquisitiOnSyStem

~、^,ANG

Hong.Un,WANG

Ybng,ZHIYbng

(Schoolof日ectmIlicsaIldIllfomationEngineering,SichuaIl

Abst船ct:Tmspaperin订oduces

witllFPGA

Key

resources.

a

UniVerS吼Chengdu,61()()64,China)

on

muld—channel11ighspeeddataacquisitionsystembasedPCI.Anaccurateclockmo(1uleisdesigned

words:hi曲speeddataacquisition;FPGA;time—sharedsampling;phaseshiftingclock

1

引言

随着现代科学技术的发展,数据采集技术已渗透到地质勘

制信息的数据流。再送到FIF0缓冲后,在异步读时钟和控制信号的控制下,写入DDR—SDRAM中存储,也可通过FIFO和PCI接口与PC机进行通信等后续处理和应用。

探、医疗器械、雷达、通讯、测控等众多技术领域,对采样速率和采样精度提出了越来越高的要求。但目前受AD芯片发展水平的限制,单片AD很难同时做到高速率和高精度采样,为了突破高速率、高精度的瓶颈,用多片高速的AD芯片进行交替采样是提高系统采样率的一种有效方法。在多片并行AD采样系统中,

信号的重构对于采样时钟的精度要求相当严格,传统的晶体振荡

器加移位电路和滤波电路的模拟方式已不能满足这一要求;采用专用的时钟芯片,时钟模块的灵活性又不够;本设计采用FPGA的内部专用时钟模块和逻辑资源构建了能满足系统要求的灵活

的高精准时钟模块。

图1数据采集系统结构图

在传统的数据采集系统中,AD的控制和数据的转存可通过微处理器来进行控制。当此方式用于高速数据采集系统将会浪费大量CPU资源,而对于MCU来说根本不可能控制高速数据的

2

数据采集系统简介

系统设计架构如图l所示:

首先前端输入的模拟信号经过信号调理电路处理后,送到

采集和存储过程。因为,一般将AD转换的结果读入,然后再转存到片外的存储器中,此过程至少需要4个机器周期。传统的微处理器或者采用ARM的方案,根本不能满足系统的需要。因此,本系统采用FPGA方案来实现50M时钟采样率14位精度的高速数据采集系统,同时通过PcI总线与PC机通信。

ADS2807转换器。每通道AD输出的14位数字信号通过应用

FPGA内部的逻辑电路合并处理后,形成一个64位的带符号和控

收稿日期:2006—1卜03

时钟模块设计与实现

万方数据

经验交流

T酏hnica|COmmunicatiOns

《自动化技术与应用》2007年第26卷第6期

3。lFPGA内嵌锁相环原理分析

随着系统时钟频率的逐步提升,I/0性能要求越来越高,于

语言描述,运用D触发器的时延特陛和综合时加入硬时延约束【4]条件从而达到精准的移相要求。其部分关键代码如下:

是在FPGA内部出现了专门的时钟管理单元,其最具有代表性的

if(删—n)

就是延时锁定环(DLL)和锁相环(PLL)两种电路。DLL作为Xilinx公司的纯数字电路实现的离散延时单元电路模块,不能过滤掉时钟源的抖动,而且会引入固有的抖动,造成抖动的积累。

本系统选用Altera公司的内嵌PLL管理单元的CydoneII芯片为核心器件。PLL作为Altem在FPGA内嵌的模拟时钟管

理单元,在消除时钟抖动,延迟等方面有着卓越的表现。其结构原

dkout<=41b0000:elseif(sp—dp—sel==l’bo)

cmout<={Sp—inc墩,sp

elSeif(pⅡc墩)

indk,sp

inclk,s皿inclk};

be翊n

c墩out【3】<=c墩o“2];

dkout[2]<=dkout[1];clkout【1]<一dkout【0】;dkout[0]<=dpjncU‘;

end

碰?I:它通过压控振荡器(VCO)自振来产生高精时钟,同时反馈给输入端的频率相位检测器(PFD)。频率相位检测器根据比较

输入时钟和反馈时钟的相位来判断压控振荡器输出的快慢,同时

输出两个控制信号Pump』p和Pump—doⅥm给环路低通滤波器(LPF)。环路低通滤波器把这些变换成电压信号,再用来控制VC0的输出频率,当PFD检测到输入时钟和反馈时钟的边沿一致时,锁相环锁定。3.2

在编译仿真,时序优化后生成生成供顶层调用的SlDeCLK子模块,再加入舢tpⅡO锁相环子模块,就完成了整

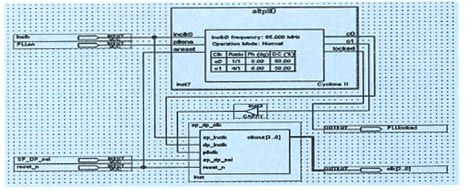

个时钟部份的顶层设计。如图3所示:

并行时间交替采样设计原理分析

假定一数据采集系统采样率为£,共有N片AD(其中每片

AD采样率均为£/N);使采样信号同时到达每片AD的输入端,由于每路信号的采样率为£/N,且均满足相邻两通道之间的时钟相位差360/N度;相邻通道之间的采样时间间隔为E(1/£),则N路信号合并处理后输出的数据率可达到e。在理想情况下,这样的系统称为并行时间交替均匀采样[2]系统,其采样波形示例如图2所示。

J

图3时钟模块顶层设计原理图

o

一,r17r_……l|r1—T——二一一~

T

2T

(N~t)T

NT

3.3.2仿真测试结果分析

在QuartuSIl5.1的软件平台上用其自带的综合和波形仿真工具对cⅨ3,c11【2,cu【l,clk0之间的相位差仿真结果如图4所示:

一

图2并行时间交替采样波形示例

sp一蚓为‘0’:可以得到cⅨ3,cⅡ【2,dkl,cll【0和Sp一砌【为同

频同相的时钟;当系统需要进行时间交替采样,以提高采样率时,时钟。通过添加TimeBar标志线可以准确的测得clk3,clk2,

当系统需要用sp-inclk对四路信号进行同频同相采样时,选择

3.3时钟模块软件设计与实现和测试结果分析3.3.1时钟模块软件设计

在高速高分辨的AD采样电路中,采样时钟的微小抖动都将大大降低AD转换电路的信噪比,使其有效位减小,而采样时钟的偏移也将影响两路AD之间的正交一致性。当然对于高速并行时间交替采样系统,时钟的准确性要求更加严格。当采用基于FPGA内嵌的pLL模块和资源来实现此类系统的高精时钟,由于FPGA方式灵活的特点,可以依据现场的具体|青况,对的内部配置进行修改和调试,可达到十分满意的效果。

由并行交替时间采样的原理分析可知,相邻时钟相位差应为90度。对于90度移相设计,采用由上至下的顶层原理图设计。在灿tem公司提供的QLlartusIl5.1集成开发环境【3]中,可以直接调用PLL模块按实际系统需要进行配置,生成PLL子模块,为

把sp_dp_9el置为‘1’,这样可得到四路相邻间相差900度的同频

c墩1,cⅡ∞相互间的相差,当改变姒k的频率进行多次测量:两两

相邻时钟间相位差的最小值为0.436ps;两两相邻时钟间相位差的最大值为0.867pS。

SP_DP—CLK子模块提供两个基准时钟电i11clk和一个四倍频于

incu【的p1】dk时钟。其中SPDP—CLK子模块设计采用Vemog

图4

时钟模块仿真波形

(下转第95页)

万方数据

经验交流

TbchnicaI(:OmmunicatiOns

Ⅸ自动化技术与应用》2007年第26卷第6期

主控制芯片W77E58发出命令,GM82C765B来完成相应的指令如读磁道、读卷标、格式化、读数据、写数据、读已删除数据、写已删除数据等。这样主控制芯片与软盘控制芯片之间必定要有相关电路与之配合。

(2)等待主状态寄存器D7(RQM)=1D6(DIO)=0

(3)写一个参数,转执行阶段,至全部参数写完;

2.执行阶段:

根据输入的命令和参数,执行命令;如果是读写命令则按规定的中断方式或DMA方式与主控制芯片交换数据。

4

软件实现

不论何时,只要GM82C765B处在命令阶段,就可以写入命

3.结果阶段:

主控制芯片必须按顺序读取状态信息和参数信息,两者都不

可少,再用状态信息确定执行的正确性。

令。每一种命令都有一个独一无二的,由所需的参数和状态结果组成的集合。GM82C765B先检验第一个字节,看它是否为一条有效的指令,如果是,则进而执行之;如果是无效的,那么到下一次时MSR寄存器中的RQM位就为“l”,同时DIO位和CB位也为“1”,表明必须读取FIF0【l】o在FIF0里会读出一个结果字节80H,

表示发出的是无效命令。从FIF0读取了结果字节后,

GM82C765B就返回到命令阶段。

GM82c765B主状态童在器:

D0(DOB)Dl(DlB)D2(D2B)

0号寻遭虻

1号寻道忙2号寻道忙3号寻道忙

FDC

图2读数据或写数据程序框图

D3(D3B)

D4(CB)D5(NDM)

忙

非DMA方式

一0,FDC接收;=1,FDC发送

5

结束语

本接口电路运行稳定、可实珊l生好,已被某电控有限公司采

D6(DIO)

D7(RQM)主骂;统发:彭0瑟0—0.FI)C瑶嗣量瓣l

主系统接:数据到=l;系统取走数据=0

u

用,生产出实际产品并投放市场。基于本电路设计出的产品是绣花机控制系统的辅助设备,产品性价比高,得到用户的青睐,有很

好的市场前景。

GM82C765B等待的最大时限是12s,这样可满足主控制

芯片时序关系[2l。在进行读数据或写数据时,DMA要予以初始

化,还要始发读命令或写命令。

命令执行三阶段分为:l命令阶段,2执行阶段,3结果阶段。在执行命令前先检查主状态寄存器D4(BuSY)=0D0(寻道)=0,再进入命令阶段。

1.命令阶段:

(1)主控制芯片往765写命令码;

(上接第103页)

参考文献:

[1】Intel公司-夕h围器件系列手册【M】.上海:匕海科学普及出版社,1994[2】李朝青.单片机原理及接口技术【M】.北京:北京航空航天大学出版社,1999

作者简介:郭俊明(1976一),男,工程师,研究方向:嵌入式系统开发。

由时钟参数在高速数据采集系统中的影响[5]一文中提出的计算时钟相位偏移对采样有效位和采样后信号的正交一致l生的影响公式计算得出,当偏移误差在1个ps范围内时,将能满足50M采样率和14位的采样精度的高速高精AD芯片对时钟的要求。因此,采用FPGA来实现本系统的时钟模块,能严格的满足设计需要。

参考文献:

【l】Altera.INC.CyclorleIIDevice

ClOck

Handbook

Section

II【Z】.

Mamgement.2006.1

19l;

[21张清洪,吕幼新.多片ADc并行采集系统的误差时域测量与校正.[J]电讯技术.2005.(4):189

3

A1tera.INC.QuartuS11Developm∞tS0ftwareHandbook

[Z】v6.0.2006.1;

[4]吴继华,王诚.AlteraFPGA/CPLD设计(高级篇)[M】.北京:人民邮电出版社,2005.

[5】马永刚,何佩琨等.时钟参数在高速数据采集系统中的影响…,数采与监控.2005.(9):2l一23

4

结束语

时钟作为一个数据采集系统的重要组成部分,对于系统有着

非常重要的作用和地位。通过应用FPGA内部的高速时钟管理模块和资源,设计并实现了能满足系统要求的时钟模块,已在该高速数据采集卡上成功应用。

作者简介:王红林(1982一),男,硕士研究生,研究方向:集成电路设计与应用。

万方数据

高速数据采集系统中时钟模块的设计与实现

作者:

作者单位:

刊名:

英文刊名:

年,卷(期):

被引用次数:王红林, , 植勇, WANG Hong lin, WANG Yong, ZHI Yong四川大学电子信息学院,四川,成都,610064自动化技术与应用TECHNIQUES OF AUTOMATION AND APPLICATIONS2007,26(6)1次

参考文献(5条)

1.马永刚;何佩琨 时钟参数在高速数据采集系统中的影响[期刊论文]-数采与监控 2005(09)

2.吴继华;王诚 Altera FPGA/CPLD设计(高级篇) 2005

3.Altera INC Quartus Ⅱ Development Software Handbook v6.0 2006

4.张清洪;吕幼新 多片ADC并行采集系统的误差时域测量与校正[期刊论文]-电讯技术 2005(04)

5.Altera INC Cyclone Ⅱ Device Handbook Section Ⅱ Clock Management 2006

引证文献(1条)

1.漆晶.包杰 基于MPC8280的IMA E1数据采集系统设计[期刊论文]-现代电子技术 2009(4)

本文链接:http://d..cn/Periodical_hljzdhjsyyy200706035.aspx

-

数据采集实验报告

中国石油大学(北京)实验报告实验名称:基于声卡的数据采集班级:过程10-4班学号:***姓名:***成绩:实验日期:20**年1月…

-

数据采集实验报告

实验报告班级姓名学号实验二基于单片机控制的直流微电压测量系统设计一任务设计并制作一套直流微电压测量装置用来测量输入的正负直流微电压…

-

数据采集系统实验报告AD模块的设计

JIANGSUTEACHERSUNIVERSITYOFTECHNOLOGY数据采集系统实验AD采集模块设计学院名称电气信息工程学院…

-

PHP数据采集实验报告

PHP数据采集实验报告班级:10网工三班学生姓名:谢昊天学号:1215134046实验目的和要求:1、使学生掌握各种Form表单控…

-

数据采集与处理技术实验报告

数据采集与处理技术实验报告书实验名称ADC量化与显示原理实验实验时间20xx年11月24日得分一实验目的1了解数据采集中ADC外围…

-

PHP数据采集实验报告

PHP数据采集实验报告班级:10网工三班学生姓名:谢昊天学号:1215134046实验目的和要求:1、使学生掌握各种Form表单控…

-

实验三野外数据采集

数字化测图技术及应用实验三全站仪数字测图外业数据采集指导书一实验目的与要求1掌握用GTS102N全站仪进行数字测图外业数据采集的作…

-

GPS实验数据处理报告

中南大学本科生课程实验报告GPS测量与数据处理学生姓名指导教师陈煌匡翠林学院地球科学与信息物理学院专业班级学生学号测绘0902班G…

-

数据采集实验报告

实验报告班级姓名学号实验二基于单片机控制的直流微电压测量系统设计一任务设计并制作一套直流微电压测量装置用来测量输入的正负直流微电压…

-

电子系统设计实验报告【多路数据采集系统设计(单片机设计类)】

电子系统设计报告题目多路数据采集系统设计单片机设计类摘要本设计采用ATmega16单片机作为数据采集系统的控制核心系统分为数据采集…