EDA 课程设计论文()

《EDA技术》课程结业论文

题目:交通灯控制器

姓 名:

班 级:

学 号:

指导教师:

日期:20##年4月30日

摘 要

EDA(Electronic Design Automation)-电子设计自动化,作为现代电子信息工程领域的一门新技术,它已成为电子设计的主要手段,本次课程设计的只要课题是设计一个交通信号灯控制器,此控制器由一条主干道和一条支干道汇合成十字路口,在每个入口处设置红、绿、黄三色信号灯,红灯亮禁止通行,绿灯亮允许通行,黄灯亮则给行驶中的车辆有时间停在禁行外。值得注意的是,交通灯两个方向的灯的状态是相关的。也就是说,每个方向的灯的状态影响着另外一个方向的灯的状态,这样才能够协调两个方向的车流。如果每个方向的灯是独立变化的,那么交通灯就没有了意义。本论文包括将向我们展现交通灯控制器的设计思想,以及设计原理,各模块的设计理念,除此之外还将给出我们自己的观点,设计后的心得,对于设计过后的想法,从中学习到的等各方面内容。

关键词:EDA 交通灯控制器 设计思想 心得

目 录

第一章 总体设计思想………………………………………………

1.1 设计基本要求……………………………………………

1.2 基本原理 …………………………………………………

1.3 设计框图 …………………………………………………

第二章设计步骤和调试过程………………………………………

2.1 总体电路设计……………………………………………

2.2 模块设计…………………………………………………

2.3 实验调试…………………………………………………

第三章 作者的观点想法…………………………………………

3.1 实验过程………………………………………………

3.2 实验心得体会 ………………………………………

小 结……………………………………………………………

致 谢……………………………………………………………

参考文献……………………………………………………………

第一章 交通灯控制器总体设计思想

1.1 设计基本要求

1、红、绿、黄发光二极管作信号灯,用传感器或逻辑开关作检测车辆是否到来的信号,实验电路用逻辑开关代替。

2、主干道处于常允许通行的状态,支干道有车来时才允许通行。主干道亮绿灯时,支干道亮红灯;支干道亮绿灯时,主干道亮红灯。

3、主、支干道均有车时,两者交替允许通行,主干道每次放行45秒,支干道每次放行25秒,设立45秒、25秒计时、显示电路,选择1HZ时钟脉冲作为系统时钟。

4、在每次由绿灯亮到红灯亮的转换过程中,要亮5秒黄灯作为过渡,使行驶中的车辆有时间停到禁行线外,设立5秒计时、显示电路。

1.2 基本原理

交通灯是城市交通中不可缺少的重要工具,是城市交通秩序的重要保障。本实例就是实现一个常见的十字路通灯功能。读者通过学习这个交通灯控制器,可以实现一个更加完整的交通灯。例如实现实时配置各种灯的时间,手动控制各个灯的状态等。

一个十字路口的交通一般分为两个方向,每个方向具有红灯、绿灯和黄灯3种,另外每个方向还具有左转灯,因此每个方向具有4个灯。

这个交通灯还为每一个灯的状态设计了倒计时数码管显示功能。可以为每一个灯的状态设置一个初始值,灯状态改变后,开始按照这个初始值倒计时。倒计时归零后,灯的状态将会改变至下一个状态。

值得注意的是,交通灯两个方向的灯的状态是相关的。也就是说,每个方向的灯的状态影响着另外一个方向的灯的状态,这样才能够协调两个方向的车流。如果每个方向的灯是独立变化的,那么交通灯就没有了意义。

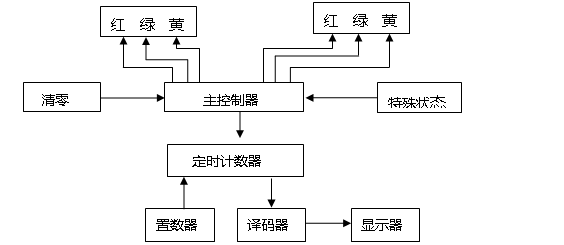

1.3设计大致框图

交通灯控制器原理框图如下图所示,包括置数模块、计数模块、主控制器模块和译码器模块。由于本实验室所用的硬件开发板是50MHZ,因此需要接分频器进行分频。置数模块将交通灯的点亮时间预置到置数电路中,计数模块以秒为单位倒计时,当计数值减为零时,主控电路改变输出状态,电路进入下一个状态的倒计时。其中,核心部分是主控制模块。

第二章 设计步骤和调试过程

2.1总体设计电路

由以第一章的设计大致框图,我们有一个大致的了解交通灯控制器主要由置数模块、计数模块、主控制器模块和译码器模块以及分频等几个模块组成。这样一来我们就可以把其进行模块化设计与理解。那么经过分析以及结合设计要求可得出总体设计电路如下所示

从总体设计电路可以看出上面的核心器件是主控制器,除此之外我们还需了解每一个器件所实现的功能,以及在电路中起到的作用。

2.2模块设计

(1)交通灯控制器JTDKZ设计模块

JTDKZ器件如下

JTDKZ也即主控制器部分,它是连接定时计数,以及显示灯亮,输出等的中心部分。对于其源程序在此就不一一列举出来进行逐条讲解。

(2)显示控制单元CSKZ设计模块

由上面显示控制单元的各个引脚可以看出它所连接的输入与输出的部分。

(3)倒计时45s——CNT45s设计模块

倒计时45秒计数器,也即从44秒到0秒的以个计数器,输出后接七段译码显示器,显示数字为十进制,用两位即可表示。

(4)倒计时25s——CNT25s设计模块

25秒倒计时计数模块原理与45秒基本相同,注意其输入与输出。

(5)倒计时5s——CNT05s的设计模块

5秒倒计时,和上面两个不同之处,它只需一位即可表示。

(6)分频器设计模块

由于我们在课堂上学习过分频器的设计所以在此可以接进十分频器进行十次分频。分频其如下:

上述的各个模块的设计,需我们自己动手进行程序的书写,然后进行编译,封装打包,最后进行连线得到总体的电路原理图,再进一步的分析。

2.3实验调试结果

在进行硬件开发板测试之前,我们可以先进行波形仿真以测试我们所连接的电路是否正确。在确认仿真结果基本无错误之后,再进行锁引脚,硬件测试等工作。

通过自己锁的各个引脚,来控制各个状态实现设计要求的灯亮情况。

开始时,支干道没有车辆行驶。主干道处于常通行状态,支干道处于禁止状态;

当支干道有车来时,主干道亮绿灯,经行45秒倒计时,支干道亮红灯,经行25秒倒计时;

主干道45秒倒计时结束后跳变到黄灯,进行5秒倒计时,支干道继续亮红灯,进行倒计时;

主干道5秒倒计时结束后跳变到红灯,经行45秒倒计时,支干道跳变到绿灯,进行25秒倒计时;

支干道25秒倒计时结束后跳变到黄灯,进行5秒倒计时,主干道继续亮红灯,进行倒计时;

支干道5秒倒计时结束后,判断支干道是否有车,若有车跳变到S1状态,没有车跳变到S0状态

第三章 作者的观点想法

3.1实验过程

刚开始想到交通灯控制器这个设计课题时,我们组的三名成员都有各自拿出自己的想法,交通灯大致是差不多的,但至于往细节里讲,就有各种不同的类型,经过我们组各成员查阅资料以及相互之间的讨论,最后决定设计此类型的交通灯。刚开始,对于原理图里面的每一个原件,我不能说百分之百的全部都懂,其中在看主控制器时程序里面是有一大段看不懂的,经过三人的共同讨论才得出一致的结论。在实验的过程中我们每一个组员都有参与课题的设计,有负责程序的书写以及编译打包的,有负责连接电路图的,当然对于全局电路的理解是我们组三人共同进行讨论的,以及向其他同学的请教得出的,组长还负责了跟老师讲解我们所设计的课题实现了怎样的功能等等。在实验过程中我负责了十分频器的制作,以及倒计时五秒器件的制作,同时还和他们一起参与了部分器件锁引脚的工作。当然讨论电路功能的实现是我们全组成员共同完成的。

3.2实验心得体会

经过了此次的实验,我们收获到的不仅仅是如何完成一个课程设计的方法这一点,我感觉收获颇多。首先本次实验在很大程度上培养了我们的团队合作的意识,团队的力量让我们有不一样的感想和收获,同时有团队合作,但又不失我们独立思考这一能力的培养,分成了小组,但是每个成员又有自己独立完成的一部分。其次我还学会了面对一个自己不熟的问题时,如何把它跟我们熟悉的联系起来然后进行分析。此外程序编写以及编译过程中出现了不少的问题,这就需要我们要有足够的耐心去查错,发现程序中是哪些地方出了问题,其实有些错误是我们人为的,比如掉了个符号或者大小写的问题,或者关键字里面字母多或少了的问题等。除了常见的错误以外还出现了一些程序编写错误上的问题,这就需要我们对所编写的程序的功能进行了解,好在在这方面我们组员之间都能够积极的讨论发现问题并且解决问题。最后我们经过了数天的修改,讨论及调试,终于可以达到预期的效果。有可能在这其中我们还有很多的方面做得不够好或者有些欠缺,但是相信每一次实验我们都在逐步地提高自己。

小结

本次的课题实验,意在考察我们熟练掌握EDA理论、数字系统设计等相关知识,独立思考完成自己的设计的能力,通过本次设计,我系统的了解了交通灯的设计流程,尤其是硬、软件的设计方法,掌握了延时程序的基本功能及编程方法,掌握了它的一般原理,也进一步掌握了QuartusⅡ的使用

致 谢

本次的实验能够顺利完成,在此首先要感谢我的老师一学期以来对我的指导和教育,对于我们提出的疑问的悉心的解答,另外还要感谢我组成员陈鑫、雷燕对于组中工作分配明确,对于问题积极共同的讨论,同时还要感谢其他同学和我们之间的交流给我们以启示。

参考文献

[1] 潘松著.EDA技术实用教程(第二版). 北京:科学出版社,2005.

[2] 康华光主编.电子技术基础 模拟部分. 北京:高教出版社,2006.

[3] 阎石主编.数字电子技术基础. 北京:高教出版社,2003.

[4] 宋烈武.EDA技术与实践教程.北京: 电子工业出版社,2009.

[5] 刘艳萍,等.EDA实用技术及应用.国防工业出版社,2006.

第二篇:EDA课程设计论文 24制数字钟数字钟设计

EDA课程设计报告书

数字钟设计

设计者:

指导老师:

学 号:

专业班级:

XXXXXXXXX学院

201X.X.XX

目录

1. 摘要,关键字………………………………………………………3

2. 正文…………………………………………………………………3

2.1设计任务及要求……………………………………………………3

2.2方案选择与论证……………………………………………………3

2.3方案的原理框图及其说明……………………………………………4

2.4硬件选择……………………………………………………………4

2.5系统设计详述………………………………………………………4

2.6系统仿真及分析…………………………………………………… 6

2.7下载测试及分析……………………………………………………9

2.8收获体会、存在问题和进一步的改进意见等…………………………10

3.参考文献……………………………………………………………10

VHDL语言实现数字电子钟的设计

作者:xxx 指导老师:xxx

(xx大学xxxx学院 xxx xxxx)

[摘要]:随着基于PLD的EDA技术的发展和应用领域的扩大与深入,EDA技术在电子信息、通信、自动控制及计算机应用等领域的重要性日益突出。本文详细介绍EDA课程设计任务——数字钟的设计的详细设计过程及结果,并总结出心得体会。

[关键字]:EDA技术;VHDL语言;数字钟

EDA技术作为现代电子设计技术的核心,它依赖强大的计算机,在EDA工具软件平台上,对以硬件描述语言HDL为系统逻辑描述手段完成的设计文件,自动地完成逻辑编译、逻辑简化、逻辑分割、逻辑综合,以及逻辑优化和仿真测试,直至实现既定的电子线路系统功能。[1]笔者详细介绍在QUARTUS II软件环境下开发基于VHDL语言数字钟的设计。

1.设计任务及要求

1、设计内容

选用合适的可编程逻辑器件及外围电子元器件,设计一个数字电子钟,利用EDA软件(QUARTUS Ⅱ)进行编译及仿真,设计输入可采用VHDL硬件描述语言输入法和原理图输入法,并下载到EDA实验开发系统,连接外围电路,完成实际测试。

2、设计要求

(1)具有时、分、秒计数显示功能。

(2)具有清零的功能,且能够对计时系统的小时、分钟进行调整。

(3)小时为十二小时制。

2.方案选择与论证

数字系统的设计采用自顶向下、由粗到细, 逐步分解的设计方法, 最顶层电路是指系统的整体要求, 最下层是具体的逻辑电路的实现。自顶向下的设计方法将一个复杂的系统逐渐分解成若干功能模块, 从而进行设计描述, 并且应用EDA 软件平台自动完成各功能模块的逻辑综合与优化, 门级电路的布局, 再下载到硬件中实现设计[1]。

因此对于数字钟来说首先是时分秒的计数功能,然后能显示,附带功能是清零、调整时分。通过参考EDA课程设计指导书,有以下方案:

1. 作为顶层文件有输入端口:时钟信号,清零按键,调时按键,调分按键;输出端口有:用于接数码管的八段码输出口,扫描用于显示的六个数码管的输出口。

2. 底层文件分为:1时间计数模块。分秒计数模块计数为60计数,时计数模块为12计数。2显示模块。显示模块由一个六进制计数器模块和一个七段译码器组成。六进制计数器为六选一选择器的选择判断端提供输入信号, 六选一选择器的选择输出端分别接秒个位、秒十位、分个位、分十位和时个位、时十位的选通位用来完成动态扫描显示,同时依次输出秒个位、秒十位、分个位、分十位和时个位、时十位数向给译码模块。3报警模块(为指导书自带)。当时间到整点时就报时。输入有时分秒计数,时钟脉冲。

3.方案的原理框图及其说明

以上为方案原理图,秒计数、分计数模块为60计数,计满后分别产生分脉冲、时脉冲,用于分计数、时计数。各计数器同时将计数值送报时模块和送数及六选一选择器模块。送数及六选一选择器模块依次将秒分时数送往译码模块译码,同时产生扫描信号用于数码管扫描显示。整点报警在整点时刻将秒脉冲信号送扬声器声音报警。

4.硬件选择

本次选用cyclone系列EP1C3T144C8芯片。外部需接2个不同频率的时钟信号,及几个上升沿按键,并接扬声器和不许译码器的数码管。以上均由EDA试验箱提供。

5.系统设计详述

整个系统的构成如下图所示。其中输入端口有:

clk1——用于送数及六选一选择器和整点报警的时序脉冲;

Stop——用于整点报时的停止控制;

clk——作为秒脉冲和整点报警的信声音号;

reset——用于各个模块复位;

setmin——调整分钟,接按键;

sethour——调整小时,接按键;

输出端口:

speak——接扬声器,用于报时;

led——接数码管,送字型码;

dp——接数码管的小数点为,隔开时分秒位;

sel——位选扫描信号输出口,接数码管位选接口;

6.系统仿真及分析

1.各模块仿真及分析。

1 Second模块

从仿真图形上来看,daout从0加到59后enmin有进位,setmin有脉冲时,enmin也会出现脉冲,说明秒计数,分调整,分脉冲都是正确的。

2minute模块

从仿真图形上来看,daout从0加到59后enhour有进位,说明分计数,时脉冲都是正确的。

3hour模块

从仿真图看,daout从0加到B即0到11后重新从0开始加,说明十二小时计数正确。

4settime模块

从仿真波形看,sec、min、hour分别设置数为09、08、1时,daout也依次输出0、9、0、8、0、1,将时分秒的每一位输出,同时sel输出正确扫描信号,dp小数点输出也正确。

5alert模块

从仿真波形来看,当stop=0和damin=0时,可看出speak有脉冲输出,stop=1停止。说明报时是正确的。

6deled模块

从仿真波形来看,num输入0~9,而led分别输出相应正确字型码。

7.下载测试及分析

下载测试后的效果如下图所示,按复位键后数码管显示0时0分0秒开始计数,分秒时计数都正确。按动调分键或调小时键后,分位或小时位开始自加,再按键后停止。当时间到整点时会有十秒报时,按动停止键停止报时,不按此键时自动到十秒后停止报时。设计结果达到要求。

8.收获体会、存在问题和进一步的改进意见等。

此次设计虽然指导书上有参考程序,但经本组同学仿真后仿真波形与理论值差别很大,因而遇到很大困难,使进度大大减慢。“梅花香自苦寒来,宝剑锋从磨砺出”,经过本组同学齐心协力,我们从程序发现分秒时计数上出了问题。参考程序分秒时计数采用十六进制表示,即用BCD码来表示计数值,便于后面译码输出。但不足是在计数时,加一运算时按十六进制来计算,本来控制加到59或11(均采用BCD码表示),实际上计数超过60或12.,是问题根本所在。认识到这一方面,本人通过将所有计数值数据类型改为整型,并在其它方面做了较大改进。经过全组成员努力和老师的认真指导,多次仿真结果正确,硬件测试显示正确。报时模块起先报时时间不准,经最后修改也正确报时。这次设计圆满完成任务。

从这次EDA设计中,可以看我们的动手能力还有待提高。另一方面,我们更加对EDA从实践上更有深刻认识。从实践中发现问题,分析问题,解决问题在这次设计中很大的体现出来,提高了我们的能力和自信。同时,成功与团队合作十分不开的。

[参考文献]

[1] 潘松, 黄继业. EDA 技术实用教程[M] 第2版 北京: 科学出版社, 2006

[2] 曹昕燕 ,周凤臣,聂春燕.EDA技术实验与课程设计 北京:清华大学出版社,2006.5

-

工程预算课程设计总结

课程设计是培养学生综合运用所学知识,发现,提出,分析和解决实际问题,锻炼实践能力的重要环节,是对学生实际工作能力的具体训练和考察过…

-

c++课程设计总结

课程设计总结经过一个学期对《C++程序设计》的学习,我学习到了基本的理论知识,了解到了C++语言程序设计的思想,这些知识都为我的课…

-

化工原理课程设计总结

《化工原理课程设计》总结本学期顺利完成了化学工程与工艺专业共100名同学的化工原理课程设计,总体来看学生的工艺计算、过程设计及绘图…

-

PLC自动门课程设计心得体会

PLC自动门课程设计心得体会:通过此次C语言程序设计实践本人实在是获益不浅!C语言是上个学期开的课程所以这个学期并没怎么看过当要开…

-

课程设计心得体会

课程设计心得体会在初学C语言的一个学期后,学校组织我们进行了C语言实训,尝试编写一些有难度的程序。在为期两周的时间中,同组同学共同…

-

年终总结

在过去的一年里,我在领导、同事们的支持和帮助下,用自己所学知识,在自己的工作岗位上,尽职尽责,较好的完成了各项工作任务。为公司做出…

-

太平学校民主评议学校工作总结

太平学学创办于19xx年,现有专任教师56人,18个教学班,在校学生560余人。民主评议政风行风活动,是学校工作的一个重要组成部分…

-

上半年安全隐患整改工作总结

工作总结/计划淮安市青山煤矿上半年安全隐患排查整改工作总结20xx年x月x日淮安市青山煤矿青山煤矿上半以来,严格按照上级部门的指示…

-

工作总结

20xx—20xx年温州大学瓯江学院学生会个人总结青年志愿者协会yqq20xx年x月x日不知不觉,在学生会已经工作了一年。加入院学…

-

20xx年慢性病工作总结

高台中心卫生院20xx年慢性病(高血压、2型糖尿病)工作总结基本公共卫生慢性病(高血压、2型糖尿病)管理服务项目开展以来。根据年初…