寄存器实验报告

寄存器实验报告

一、实验目的

1. 了解寄存器的分类方法,掌握各种寄存器的工作原理;

2. 学习使用Verilog HDL 语言设计两种类型的寄存器。

二、实验设备

PC 微机一台,TD-EDA 实验箱一台,SOPC 开发板一块。

三、实验内容

寄存器中二进制数的位可以用两种方式移入或移出寄存器。第一种方法是以串行的方式将数据每次移动一位,这种方法称之为串行移位(Serial Shifting),线路较少,但耗费时间较多。第二种方法是以并行的方式将数据同时移动,这种方法称之为并行移位(Parallel Shifting),线路较为复杂,但是数据传送的速度较快。因此,按照数据进出移位寄存器的方式,可以将移位寄存器分为四种类型:串行输入串行输出移位寄存器(Serial In- Serial Out)、串行输入并行输出移位寄存器(Serial In- Parallel Out)、并行输入串行输出移位寄存器(Parallel In- Serial Out)、并行输入并行输出移位寄存器(Parallel In-Parallel Out)。

本实验使用Verilog HDL 语言设计一个八位并行输入串行输出右移移位寄存器(Parallel In- Serial Out)和一个八位串行输入并行输出寄存器(Serial In- Parallel Out),分别进行仿真、引脚分配并下载到电路板进行功能验证。

四、实验步骤

1.并行输入串行输出移位寄存器实验步骤

1). 运行Quartus II 软件,选择File?New Project Wizard 菜单,工程名称及顶层文件名称为SHIFT8R,器件设置对话框中选择Cyclone 系列EP1C6Q240C8 芯片,建立新工程。

2.) 选择File?New 菜单,创建Verilog HDL 描述语言设计文件,打开文本编辑器界面。

3.) 在文本编辑器界面中编写Verilog HDL 程序,源程序如下:

module SHFIT8R(din,r_st,clk,load,dout);

input [7:0]din;

input clk,r_st,load;

output dout;

reg dout;

reg [7:0]tmp;

always @(posedge clk)

if(!r_st)

begin

dout<=0;

end

else

begin

if(load)

begin

tmp=din;

end

else

begin

tmp[6:0]=tmp[7:1];

tmp[7]=0;

end

dout<=tmp[0];

end

endmodule

4). 选择File?Save As 菜单, 将创建的VHDL 设计文件保存为工程顶层文件名 SHIFT8R.V。

5). 选择Tools?Compiler Tool 菜单,编译源文件。编译无误后建立仿真波形文件SHIFT8R.VWF。选择Tools?Simulator Tool 菜单进行仿真。

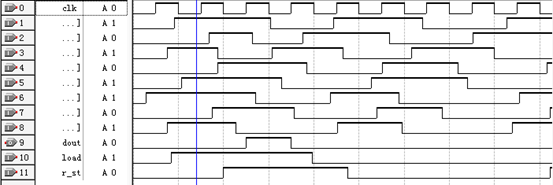

时序仿真:

功能仿真:

6). 分析仿真结果,仿真正确后选择Assignments?Assignment Editor 菜单,对工程进行引脚分配。分配结果如下表所

7). 选择Tools?Compiler Tool 菜单,点击”Start”按钮对此工程进行编辑,生成可以配置到FPGA 的SOF 文件。

8). 使用TD-EDA 实验系统及SOPC 开发板,如图3-6-1 所示进行实验接线,将ByteBlaster II 下载电缆插入SOPC 开发板的JTAG 下载接口。仔细检查确保接线无误后打开电源。

9). 在Quartus II 软件中,选择Tools?Programmer 菜单,对芯片进行配置。

10). 配置完成后验证移位寄存器的正确性。

2.串行输入并行输出寄存器实验步骤

1). 运行Quartus II 软件,选择File?New Project Wizard 菜单,工程名称及顶层文件名称为SHIFT8,器件设置对话框中选择Cyclone 系列EP1C6Q240C8 芯片,建立新工程。

2). 选择File?New 菜单,创建Verilog HDL 描述语言设计文件,打开文本编辑器界面。

3). 在文本编辑器界面中编写Verilog HDL 程序,源程序如下:

module SHIFT8(din,clk,r_st,dout);

input clk;

input r_st;

input din;

output [7:0]dout;

reg [7:0]dout;

reg [7:0]tmp;

integer i;

always @(posedge clk)

if(!r_st)

begin

tmp[7:0]<=8'b00000000;

end

else

begin

tmp[7]<=din;

for(i=1;i<=7;i=i+1)

tmp[7-i]<=tmp[8-i];

dout[7:0]<=tmp[7:0];

end

endmodule

4). 选择File?Save As 菜单, 将创建的VHDL 设计文件保存为工程顶层文件名SHIFT8.V。

5). 选择Tools?Compiler Tool 菜单,编译源文件。编译无误后建立仿真波形文件SHIFT8.VWF。选择Tools?Simulator Tool 菜单进行仿真。

时序仿真:

功能仿真:

6). 分析仿真结果,仿真正确后选择Assignments?Assignment Editor 菜单,对工程进行引脚分配。分配结果如表3-6-2 所示

7). 选择Tools?Compiler Tool 菜单,点击”Start”按钮对此工程进行编辑,生成可以配置到FPGA 的SOF 文件。

8). 使用TD-EDA 实验系统及SOPC 开发板,如图3-6-2 所示进行实验接线,将ByteBlaster II 下载电缆插入SOPC 开发板的JTAG 下载接口。仔细检查确保接线无误后打开电源。

9). 在Quartus II 软件中,选择Tools?Programmer 菜单,对芯片进行配置。

10). 配置完成后验证串入并出寄存器的正确性。

五、实验总结

了解寄存器的分类方法,掌握各种寄存器的工作原理;学习使用Verilog HDL 语言设计寄存器。

第二篇:寄存器实验报告

实验报告

实验名称_______________

姓名__________学号___________

同组同学姓名__________学号__________

实验日期______________

实验完成日期______________

1.实验题目名称: 寄存器实验

2.实验目的:1)掌握QuartusII 5.0软件的图形编辑、编译、 仿真的设计流程。

2)学习74670三态输出寄存器堆的使用。

3)了解寄存器组的使用,设计出完善的寄存器组。

3.实验内容:设计出功能完善的寄存器组,并对设计的正确性进行验证。具体要求如下:

1)用图形方式设计出寄存器组的电路原理图。

2)测试波形要用时序仿真实现,现将不同的数据连续写入4个寄存器后,在分别读出。

3)将设计文件封装成器件符号。

4)数据的宽度最好为16位。

4.实验设计思想:

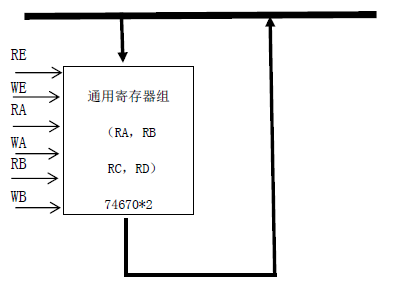

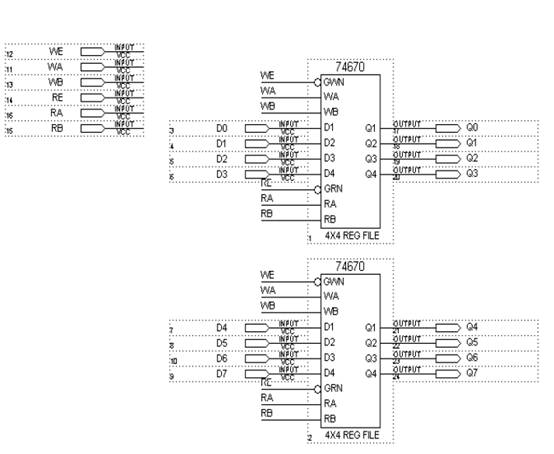

在主机系统中,寄存器组用于暂存程序运行过程中所需要的各种数据。可以采用具有三态功能的两片4位片的74LS760芯片进行设计。构成4字*8位的寄存器组。通用寄存器组的设计原理图如下:

通用寄存器组的设计原理图

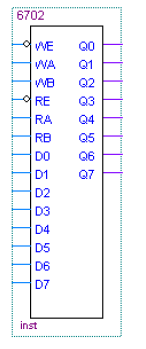

5. 芯片封装图

通用寄存器组芯片封装图

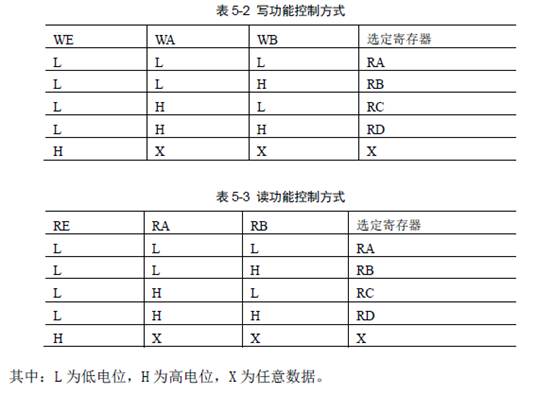

图中RA,RB输出控制管脚接收需要读出信息的通用寄存器地址,在RE读控制信号的作用下,输出相应寄存器中的数据到输出管脚Q0~Q7端。WA,WB输入控制管脚接收需要写入信息的通用寄存器的地址,在WE写控制信号的作用下,把输入管脚D0~D7的输入数据写入到相应的寄存器中。其通用寄存器的“写”“读”功能控制方式可参见表

5-2,5-3.

6.逻辑电路图

6.实验结果:

7.实验小结:

1)实验过程中所遇到的问题及其分析:

2)解决的方法:

3)实验收获:

4)对实验的意见和建议:

-

移位寄存器实验报告

移位寄存器实验报告一实验原理移位寄存器是用来寄存二进制数字信息并且能进行信息移位的时序逻辑电路根据移位寄存器存取信息的方式可分为串…

-

移位寄存器实验报告

移位寄存器实验报告一、实验目的和要求掌握移位寄存器的工作原理及设计方法掌握串、并数据转换的概念与方法了解序列信号在CPU控制器设计…

-

实验一、线性移位寄存器实验报告

实验一实验报告姓名何璟学号120xx60099实验日期20xx108一实验名称线性移位寄存器二实验目的1234了解线性移位寄存器产…

-

实验8 移位寄存器实验报告

移位寄存器实验报告一实验原理移位寄存器是用来寄存二进制数字信息并且能进行信息移位的时序逻辑电路根据移位寄存器存取信息的方式可分为串…

-

移位寄存器实验报告

移位寄存器实验报告424实验目的1掌握移位寄存器的工作原理2综合移位寄存器数码扫描电路在实验板上下载并验证结果3掌握电路仿真的基本…

-

通用寄存器实验报告

69通用寄存器实验报告一实验目的1了解通用寄存器组的用途及对CPU的重要性2掌握通用寄存器组的设计方法二实验内容1通用寄存器组的作…

-

通用寄存器组实验报告

通用寄存器组学号20xx07030姓名叶利钦专业计算121一实验目的1了解通用寄存器组的用途及对CPU的重要性2掌握通用寄存器组的…

-

计算机组成原理实验报告 通用寄存器单元实验

西华大学数学与计算机学院实验报告课程名称计算机组成原理指导教师祝昌宇实验名称通用寄存器单元实验年级20xx级姓名蒋俊学号3120x…

-

寄存器实验

实验七寄存器实验实验题目寄存器实验实验类型设计性一实验目的掌握74HC574寄存器使用方法掌握component语句和portma…

-

寄存器实验报告

实验报告实验名称姓名学号同组同学姓名学号实验日期实验完成日期1实验题目名称寄存器实验2实验目的1掌握QuartusII50软件的图…