数电实验报告之集成触发器

数字逻辑与数字系统设计实验报告

——D、JK触发器与广告流水灯异步时序电路

VHDL语言仿真

学 院 电子工程学院

班 级 卓越001012班

学 号 00101201

姓 名 冉 艳 伟

实验时间 2012.4.20

一.实验目的

1.了解集成触发器的工作原理。

2.对Quartus II 软件使用操作有初步的了解,能用该软件进行简单的VHDL语言编程与功能仿真

3、掌握VHDL设计实体的基本结构及文字规则。

二.实验仪器

1.计算机一台

2.万用表一块

3.直流稳压电源一台

4.数字电路实验板一台(含cyclone—II FPGA芯片)

5.数据下载线,JTAG连接线若干

三.实验内容

用VHDL代码输入的方法设计以下三个电路功能,并进行全程编译,执行功能和时序仿真。

1. 用VHDL语言描述D触发器功能。

2. 用VHDL语言描述JK触发器功能。

3. 用VHDL语言描述以下功能:

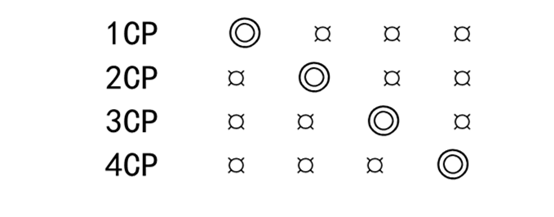

用双D触发器74LS74和与非门74LS00设计一个广告流水灯同步时序电路,广告流水灯有四个灯,这四个灯始终是一暗三明且暗灯循环右移,其状态图如图5-11所示,图中¤表示灯亮,◎表示灯暗。

四.实验数据记录与处理

1. D触发器

1)VHDL语言

library ieee;

use ieee.std_logic_1164.all;

entity Dflipflop is

port(D,clock :in std_logic;

Q :out std_logic);

end Dflipflop;

architecture behavior of Dflipflop is

begin

Process (clock)

begin

if clock'event and clock='1' then

Q<=D;

end if;

end process;

end behavior;

2)功能仿真

建立波形文件,功能仿真结果如下:

3)时序仿真

建立波形文件,时序仿真结果如下:

2.JK触发器

1)VHDL语言

LIBRARY ieee ;

USE ieee.std_logic_1164.all ;

ENTITY jkflipflop IS

PORT ( Clock : IN STD_LOGIC ;

J,K : IN STD_LOGIC ;

Q : OUT STD_LOGIC) ;

END jkflipflop ;

ARCHITECTURE Behavior OF jkflipflop IS

SIGNAL Q1: STD_LOGIC ;

BEGIN

PROCESS ( Clock )

BEGIN

IF Clock'EVENT AND Clock = '1' THEN

Q1 <= (J AND NOT Q1)OR(NOT K AND Q1);

END IF ;

Q <= Q1;

END PROCESS ;

END Behavior ;

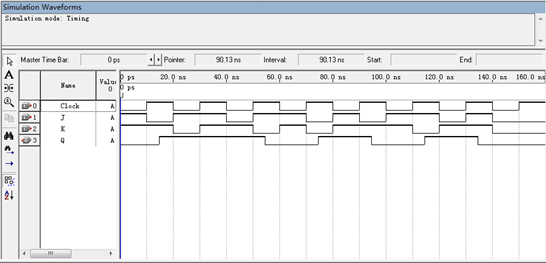

2)功能仿真

建立波形文件,功能仿真结果如下

3)时序仿真

建立波形文件,时序仿真结果如下:

3. 广告流水灯

1)VHDL语言

LIBRARY ieee ;

USE ieee.std_logic_1164.all ;

ENTITY fd2 IS

PORT ( Clock : IN STD_LOGIC ;

Q : OUT STD_LOGIC);

END fd2 ;

ARCHITECTURE Behavior OF fd2 IS

SIGNAL D : STD_LOGIC ;

BEGIN

PROCESS ( Clock )

BEGIN

IF Clock'EVENT AND Clock = '1' THEN

D <= NOT D ;

END IF ;

Q <= D;

END PROCESS ;

END Behavior ;

LIBRARY ieee ;

USE ieee.std_logic_1164.all ;

PACKAGE fd2_package IS

COMPONENT fd2

PORT ( Clock : IN STD_LOGIC ;

Q : OUT STD_LOGIC);

END COMPONENT ;

END fd2_package;

LIBRARY ieee ;

USE ieee.std_logic_1164.all ;

LIBRARY work ;

USE work.fd2_package.all;

ENTITY fd4 IS

PORT ( Clock : IN STD_LOGIC ;

Q0,Q1 : OUT STD_LOGIC);

END fd4 ;

ARCHITECTURE Structure OF fd4 IS

SIGNAL W : STD_LOGIC ;

BEGIN

S0: fd2 PORT MAP( CLOCK, W );

Q0 <= W;

S1: fd2 PORT MAP( W, Q1 );

END Structure ;

LIBRARY ieee ;

USE ieee.std_logic_1164.all ;

PACKAGE fd4_package IS

COMPONENT fd4

PORT ( Clock : IN STD_LOGIC ;

Q0,Q1 : OUT STD_LOGIC);

END COMPONENT ;

END fd4_package;

LIBRARY ieee ;

USE ieee.std_logic_1164.all ;

LIBRARY work ;

USE work.fd4_package.all;

ENTITY liushuideng IS

PORT ( Clock : IN STD_LOGIC ;

Q0,Q1 : OUT STD_LOGIC ;

L : OUT STD_LOGIC_VECTOR(0 TO 3));

END liushuideng ;

ARCHITECTURE Structure OF liushuideng IS

SIGNAL W0,W1 : STD_LOGIC ;

BEGIN

S0: fd4 PORT MAP( CLOCK, W0, W1 );

Q0<= W0;

Q1<= W1;

L(0)<= (NOT W0) OR (NOT W1);

L(1)<= W0 OR (NOT W1);

L(2)<= (NOT W0) OR W1;

L(3)<= W0 OR W1;

END Structure ;

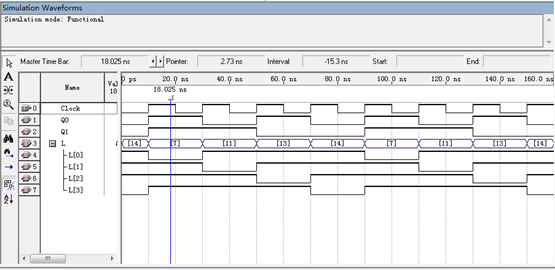

2)功能仿真

建立波形文件,功能仿真结果如下

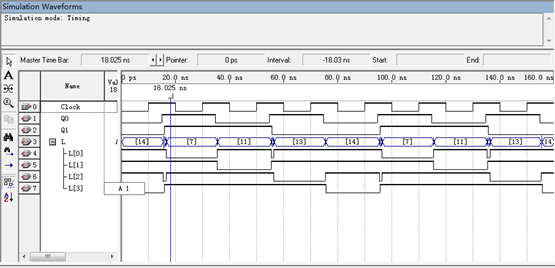

3)时序仿真

建立波形文件,时序仿真结果如下:

第二篇:集成触发器实验报告

电子电路试验报告

姓名: 专业: 班级: 学号:

一、试验名称

集成触发器功能及其应用。

二、试验目的

掌握用与非门组成的基本RS触发器的特征;掌握集成JK触发器、D触发器的逻辑功能和使用方法;熟悉各种触发器的应用。

三、试验任务

用74LS73设计一个异步四进制计数器,并用双踪示波器观察输入输出波形。

四、试验任务原理

第一步:建立原始状态表和状态图。

第二步:简化状态(实际是状态合并)

第三步:状态分配(即状态编码)

第四步:选择触发器,求激励方程和状态转移方程

第五步:检查电路是否具有自启动特性

五、实现试验的电路图及其结果

试验电路图:实现的是6进制的计数器。

波形图:

六、思考题

(1)为解决主从JK触发器的一次变化问题,对CP脉冲有何要求?

答:对CP的要求是宽度较窄的正脉冲,且在CP=1期间,输入信号J,K不发生变化

七、试验心得与体会

通过这次电子电路试验,我对触发器有了了解,触发器是一种具有记忆功能的电路,可作为二进制存储单元使用。触发器有置位端和复位端,只有当它们同时为1的时候,触发器才能正常工作,否则进行复位、置位、维持的功能,这些是我在这次试验中所学到的。

-

数电实验报告之集成触发器

数字逻辑与数字系统设计实验报告DJK触发器与广告流水灯异步时序电路VHDL语言仿真学院电子工程学院班级卓越001012班学号001…

-

触发器实验报告

深圳大学实验报告课程名称学院计算机与软件学院实验时间实验报告提交时间教务部制注1报告内的项目或内容设置可根据实际情况加以调整和补充…

- 触发器及其应用实验报告

- 集成触发器功能测试及转换_实验报告

-

集成触发器及其应用实验报告

实验报告课程名称数字逻辑实验项目名称实验6:集成触发器及其应用班级与班级代码11软件工程1班实验室名称(或课室)ss1-337专业…

-

浙大电工电子实验报告 实验十五 集成定时器及其应用

实验报告课程名称:电工电子学实验指导老师:实验名称:集成定时器及其应用一、实验目的1.了解集成定时器的功能和外引线排列。2.掌握用…

-

触发器实验报告

深圳大学实验报告课程名称学院计算机与软件学院实验时间实验报告提交时间教务部制注1报告内的项目或内容设置可根据实际情况加以调整和补充…

-

数字逻辑JK触发器实验报告

信息工程学院数字逻辑与数字系统实习报告学院信息工程学院班级信息103姓名张丽玲学号20xx013077成绩实验五JK触发器一实验目…

- 触发器及其应用实验报告

-

触发器实验报告

深圳大学实验报告课程名称学院信息工程班级实验时间实验报告提交时间教务部制深圳大学学生实验报告用纸注1报告内的项目或内容设置可根据实…

-

数电实验报告 试验五 触发器及其应用

实验三触发器及其应用一实验目的1熟悉基本D触发器的功能测试2了解触发器的两种触发方式脉冲电平触发和脉冲边沿触发及触发特点3熟悉触发…