译码器实验报告

实验2 译码器及其应用

一、实验目的

1、掌握中规模集成译码器的逻辑功能和使用方法

2、熟悉数码管的使用

二、实验原理

译码器是一个多输入、多输出的组合逻辑电路。它的作用是把给定的代码进行“翻译”,变成相应的状态,使输出通道中相应的一路有信号输出。译码器在数字系统中有广泛的用途,不仅用于代码的转换、终端的数字显示,还用于数据分配,存贮器寻址和组合控制信号等。不同的功能可选用不同种类的译码器。

译码器可分为通用译码器和显示译码器两大类。前者又分为变量译码器和代码变换译码器。

1、变量译码器(又称二进制译码器),用以表示输入变量的状态,如2线-4线、3线-8线和4线-16线译码器。若有n个输入变量,则有2n个不同的组合状态,就有2n 个输出端供其使用。而每一个输出所代表的函数对应于n个输入变量的最小项。

以3线-8线译码器74LS138为例进行分析,图5-6-1(a)、(b)分别为其

逻辑图及引脚排列。

其中 A2 、A1 、A0 为地址输入端, ~

~ 为译码输出端,S1、

为译码输出端,S1、 、

、 为使能端。

为使能端。

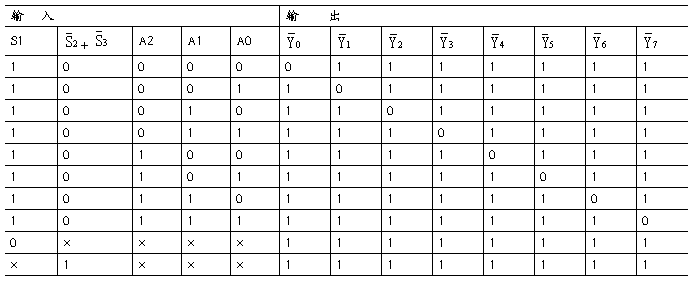

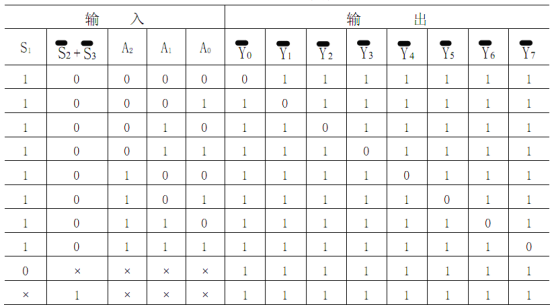

表5-6-1为74LS138功能表

当S1=1, +

+ =0时,器件使能,地址码所指定的输出端有信号(为0)输出,其它所有输出端均无信号(全为1)输出。当S1=0,

=0时,器件使能,地址码所指定的输出端有信号(为0)输出,其它所有输出端均无信号(全为1)输出。当S1=0, +

+ =X时,或 S1=X,

=X时,或 S1=X, +

+ =1时,译码器被禁止,所有输出同时为1。

=1时,译码器被禁止,所有输出同时为1。

(a) (b)

图5-6-1 3-8线译码器74LS138逻辑图及引脚排列

表5-6-1

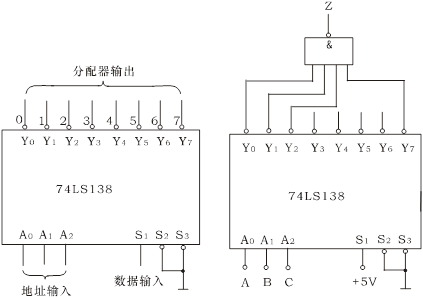

二进制译码器实际上也是负脉冲输出的脉冲分配器。若利用使能端中的一个输入端输入数据信息,器件就成为一个数据分配器(又称多路分配器),如图5-6-2所示。若在S1输入端输入数据信息, =

= =0,地址码所对应的输出是S1数据信息的反码;若从

=0,地址码所对应的输出是S1数据信息的反码;若从 端输入数据信息,令S1=1、

端输入数据信息,令S1=1、 =0,地址码所对应的输出就是

=0,地址码所对应的输出就是 端数据信息的原码。若数据信息是时钟脉冲,则数据分配器便成为时钟脉冲分配器。

端数据信息的原码。若数据信息是时钟脉冲,则数据分配器便成为时钟脉冲分配器。

根据输入地址的不同组合译出唯一地址,故可用作地址译码器。接成多路分配器,可将一个信号源的数据信息传输到不同的地点。

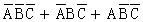

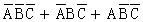

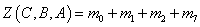

二进制译码器还能方便地实现逻辑函数,如图5-6-3所示,实现的逻辑函数是

Z=

Z= +ABC

+ABC

图5-6-2 作数据分配器 图5-6-3 实现逻辑函数

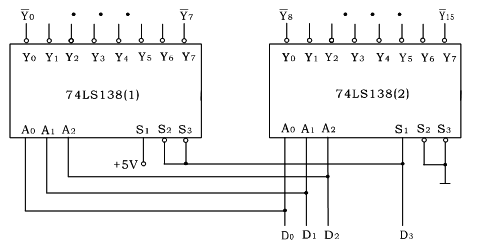

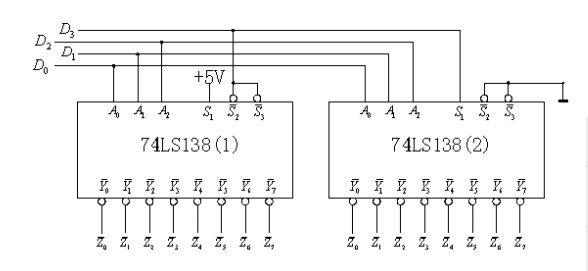

利用使能端能方便地将两个 3/8译码器组合成一个4/16译码器,如图5-6-4所示。

图5-6-4 用两片74LS138组合成4/16译码器

2、数码显示译码器

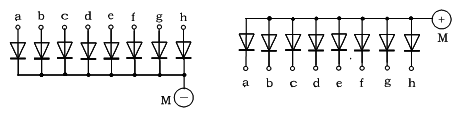

a、七段发光二极管(LED)数码管

LED数码管是目前最常用的数字显示器,图5-6-5(a)、(b)为共阴管和共阳管的电路,(c)为两种不同出线形式的引出脚功能图。

一个LED数码管可用来显示一位0~9十进制数和一个小数点。小型数码管(0.5寸和0.36寸)每段发光二极管的正向压降,随显示光(通常为红、绿、黄、橙色)的颜色不同略有差别,通常约为2~2.5V,每个发光二极管的点亮电流在5~10mA。LED数码管要显示BCD码所表示的十进制数字就需要有一个专门的译码器,该译码器不但要完成译码功能,还要有相当的驱动能力。

(a) 共阴连接(“1”电平驱动) (b) 共阳连接(“0”电平驱动)

(c) 符号及引脚功能

图 5-6-5 LED数码管

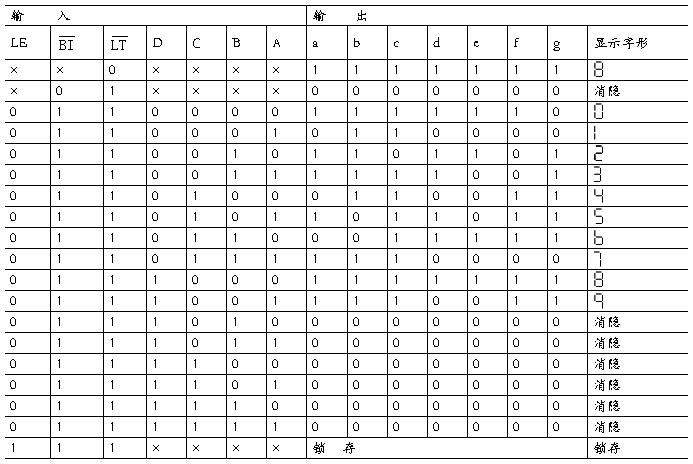

b、BCD码七段译码驱动器

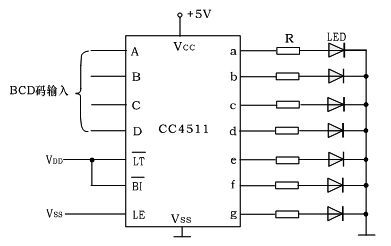

此类译码器型号有74LS47(共阳),74LS48(共阴),CC4511(共阴)等,本实验系采用CC4511 BCD码锁存/七段译码/驱动器。驱动共阴极LED数码管。

此类译码器型号有74LS47(共阳),74LS48(共阴),CC4511(共阴)等,本实验系采用CC4511 BCD码锁存/七段译码/驱动器。驱动共阴极LED数码管。

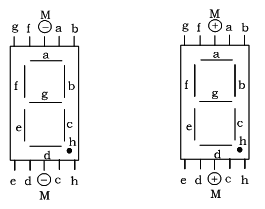

图5-6-6为CC4511引脚排列

图5-6-6 CC4511引脚排列

其中

A、B、C、D — BCD码输入端

a、b、c、d、e、f、g — 译码输出端,输出“1”有效,用来驱动共阴极LED数码管。

— 测试输入端,

— 测试输入端, =“0”时,译码输出全为“1”

=“0”时,译码输出全为“1”

— 消隐输入端,

— 消隐输入端, =“0”时,译码输出全为“0”

=“0”时,译码输出全为“0”

LE — 锁定端,LE=“1”时译码器处于锁定(保持)状态,译码输出保持在LE=0时的数值,LE=0为正常译码。

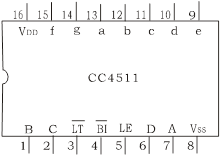

表5-6-2为CC4511功能表。CC4511内接有上拉电阻,故只需在输出端与

数码管笔段之间串入限流电阻即可工作。译码器还有拒伪码功能,当输入码超过1001时,输出全为“0”,数码管熄灭。

表5-6-2

在本数字电路实验装置上已完成了译码器CC4511和数码管BS202之间的连接。实验时,只要接通+5V电源和将十进制数的BCD码接至译码器的相应输入端A、B、C、D即可显示0~9的数字。四位数码管可接受四组BCD码输入。CC4511与LED数码管的连接如图5-6-7所示。

图5-6-7 CC4511驱动一位LED数码管

三、实验设备与器件

1、+5V直流电源 2、连续脉冲源

3、逻辑电平开关 4、逻辑电平显示器

5、拨码开关组 6、译码显示器

7、74LS138×2 CC4511

四、实验内容

1、数据拨码开关的使用。

将实验装置上的四组拨码开关的输出Ai、Bi、Ci、Di分别接至4组显示译码/驱动器CC4511的对应输入口,LE、 、

、 接至三个逻辑开关的输出插口,接上+5V显示器的电源,然后按功能表5-6-2输入的要求揿动四个数码的增减键(“+”与“-”键)和操作与LE、

接至三个逻辑开关的输出插口,接上+5V显示器的电源,然后按功能表5-6-2输入的要求揿动四个数码的增减键(“+”与“-”键)和操作与LE、 、

、 对应的三个逻辑开关,观测拨码盘上的四位数与LED数码管显示的对应数字是否一致,及译码显示是否正常。

对应的三个逻辑开关,观测拨码盘上的四位数与LED数码管显示的对应数字是否一致,及译码显示是否正常。

2、74LS138译码器逻辑功能测试

将译码器使能端S1、 、

、 及地址端A2、A1、A0 分别接至逻辑电平开关输出口,八个输出端

及地址端A2、A1、A0 分别接至逻辑电平开关输出口,八个输出端 依次连接在逻辑电平显示器的八个输入口上,拨动逻辑电平开关,按表5-6-1逐项测试74LS138的逻辑功能。

依次连接在逻辑电平显示器的八个输入口上,拨动逻辑电平开关,按表5-6-1逐项测试74LS138的逻辑功能。

3、用74LS138构成时序脉冲分配器(数据分配器)

参照图5-6-2和实验原理说明,时钟脉冲CP频率约为1Hz,要求分配器输出端 的信号与CP输入信号同相。

的信号与CP输入信号同相。

画出分配器的实验电路,用逻辑电平显示器观察和记录在地址端A2、A1、A0分别取000~111 8种不同状态时 端的输出。

端的输出。

4、用两片74LS138组合成一个4线—16线译码器,并进行实验。

5、用138实现Z函数

Z= +ABC

+ABC

五、实验报告

1、数据拨码开关的使用

由图5-6-7连接实验电路,将 、

、 和LE接至逻辑开关,优先级LE<

和LE接至逻辑开关,优先级LE< <

< ,测试结果与功能表5-6-2一致。

,测试结果与功能表5-6-2一致。

2、74LS138译码器逻辑功能测试

74LS138译码器接入电路, =

= =0

=0  =1,改变地址端A2 A1 A0,测试结果与表5-6-1一致。

=1,改变地址端A2 A1 A0,测试结果与表5-6-1一致。

3、用74LS138构成时序脉冲分配器

由图5-6-2连接实验电路,将 接高电平,

接高电平,

作数据输入,得到同相输出数据分配器,改变地址端,其对应输出端与输入信号相同且同相。

作数据输入,得到同相输出数据分配器,改变地址端,其对应输出端与输入信号相同且同相。

4、用两片74LS138组成4线-16线译码器

由图5-6-4连接实验电路74LS138(2)优先级高于74LS138(1),每时刻只选中一个输出端为0,改变 的值即可改变译码器输出。

的值即可改变译码器输出。

5、用74LS138实现Z函数

由图5-6-3连接实验电路

当输入端最小项为0、1、2、7时,Z输出为1(有效)。

六、实验心得

BCD码七段译码驱动器锁存器锁存如何实现,相当于保存上一个时间点数据?组合电路不是不能保存?那不就相当于时序电路的保存了,不懂。

第二篇:译码器及其应用实验报告

实验二译码器及其使用

一. 实验目的

1. 掌握译码器的测试方法。

2. 了解中规模集成译码器的管脚分布,掌握其逻辑功能。

3. 掌握译码器构成组合电路的方法。

4. 学习译码器的扩展。

二.实验设备及器件。

1. 数字逻辑电路实验板1块。

2. 74HC(LS)20(四二输入与非门)一片。

3.74HC(LS)138(3-8译码器)二片。

三.实验原理

1.74HC(LS)138 是集成3 线-8 线译码器,在数字系统中应用比较广泛。下图是其引脚排列,

其中A2、A1、A0 为地址输入端,~为译码输出端,S 1、2、3 为使能端。下表为74HC(LS)138

功能表。74HC(LS)138 工作原理为:当S 1=12+3=0 时,电路完成译码功能,输出低电平有效。

其中:

因为74HC(LS)138的输出包括了三变量数字信号的全部八种组合,每一个输出端表示一个最小项(的非),因此可以利用八条输出线组合构成三变量的任意组合电路;其输出低电平有效。

2.实验用器件管脚介绍:

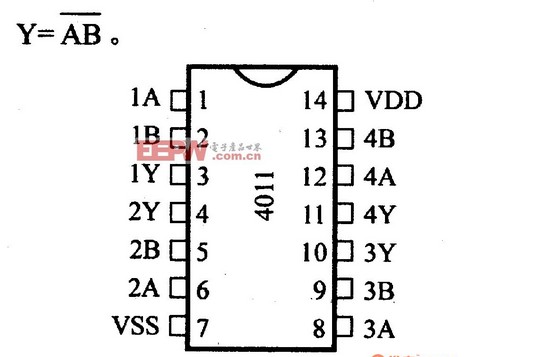

74HC(LS)20(二四输入与非门)管脚如下图所示。

四.实验内容

1.逻辑功能测试

将输出端接到发光二极管上,然后从000~111依次输入译码器,然后改变输出线与8个端口的链接,探索发光规律。如:当输入为010时(A2=0,A1=1,A0=0),输出线接在Y2(非)时发光,即其输出为低电平。

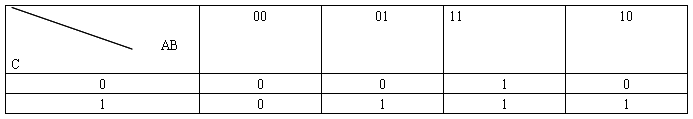

2.用74HC(LS)138实现逻辑函数(基本命题)

Y=AB+BC+CA

由k图知:

Y=m3+m5+m6+m7=Y3*Y5*Y6*Y7

Y=m3+m5+m6+m7=Y3*Y5*Y6*Y7

所以在译码器上有ABC=A2A1A0,而在译码器的输出端,将Y3,Y5,Y6,Y7接到四二与非门的输入端,四二与非门的输出端接入发光二极管即可完成逻辑电路。由于LED 是低电平有效,所以选中时Y 输出高电平,LED 反而不发光,未选中时LED灯发光。

3、扩展(扩展命题)

用两个3 线-8 线译码器构成4 线-16 线译码器

根据该图连接逻辑电路,然后对电路进行测试其是否达到预期效果。

心得:

任务一比较简单;任务二关键将逻辑表达式进行化简,以便知道如何去连接电路;任务三主要是连接线路,但是由于电线细小且使用较多,容易发生从接口脱落和接触不良的现象。

-

译码器实验报告

课程编号深圳大学实验报告课程名称数字电路实验名称译码器学院信息工程学院指导教师刘静报告人李金梁组号03学号20xx130025实验…

-

数字电路译码器实验报告

一实验目的与要求1了解和正确使用MSI组合逻辑部件2掌握一般组合逻辑电路的特点及分析设计方法3学会对所设计的电路进行静态功能测试的…

-

数字电子线路实验报告_译码器及其应用

数电实验报告实验三译码器及其应用一实验目的1掌握译码器的测试方法2了解中规模集成译码器的功能管脚分布掌握其逻辑功能3掌握用译码器构…

-

138译码器实验报告

138译码器实验报告一实验目的与要求1掌握74HC138译码器的工作原理熟悉74HC138译码器的具体运用连接方法了解74HC13…

-

译码器实验报告

实验2译码器及其应用一实验目的1掌握中规模集成译码器的逻辑功能和使用方法2熟悉数码管的使用二实验原理译码器是一个多输入多输出的组合…

-

数字电路实验二--译码器实验报告深圳大学--郭治民

深圳大学实验报告实验课程名称数字电路与逻辑设计实验项目名称学院计算机与软件学院专业计算机科学与技术报告人同组人指导教师实验时间实验…

-

译码器实验报告

课程编号深圳大学实验报告课程名称数字电路实验名称译码器学院信息工程学院指导教师刘静报告人李金梁组号03学号20xx130025实验…

-

译码器实验报告

深圳大学实验报告课程名称学院计算机与软件学院班级实验时间实验报告提交时间教务部制深圳大学学生实验报告用纸注1报告内的项目或内容设置…

-

译码器实验报告

数字电路逻辑与设计实验报告姓名刘凯班级0401206学号20xx211791实验名称译码器及其应用实验目的123掌握数码管的使用方…

-

译码器实验报告

数字逻辑实验报告院系数学与计算机学院专业计算机类4班姓名田恒学号1305110089指导教师刘昌华实验题目译码器的EDA设计实验目…

-

数字电路译码器实验报告

一实验目的与要求1了解和正确使用MSI组合逻辑部件2掌握一般组合逻辑电路的特点及分析设计方法3学会对所设计的电路进行静态功能测试的…