EDA实验_七人表决器

河 北 科 技 大 学

实 验 报 告

20##级 电信专业 122 班 学号38 15年5月20日

姓名 郑振兴 同组人 指导教师 于国庆

实验名称 实验一 七人表决器 成绩

实验类型 设计型 批阅教师

一、实验目的

(1)掌握MUXPLUS II语言输入的设计过程。

(2)初步了解VHDL语言。

(3)熟悉FPGA项目设计的基本流程。

二、实验原理:

用七个开关作为表决器的7个输入变量,输入变量为逻辑“1”时表示表决者“赞同”; 输入变量为逻辑“0”时表示表决者“不赞同”;输出逻辑“1”时,表示表决“通过”; 输出逻辑“0”时,表示表决“不通过”;当表决器的七个输入变量中有4个及以上为“1”时,则表决器输出为“1”,否则为“0”。

表决器输入采用试验箱K1~K16,输出采用试验箱L15、L16指示;同意红灯亮,否则黄灯亮。

三、实验内容及步骤

1.打开MUXPLUS II VHDL编辑器,完成七人表决器的设计。包括VHDL程序输入、编译、综合。

实验程序如下:

library ieee;

use ieee.std_logic_1164.ALL;

entity GSL is

port(a:in std_logic_vector(6 downto 0);

b:out std_logic;

c:out std_logic);

end entity GSL;

architecture number of GSL is

begin

process(a)

variable cnt:integer range 0 to 7;

begin cnt:=0;

for i in 6 downto 0 loop

if a(i)='1'then

cnt:=cnt+1;

end if;

end loop;

if cnt>3 then b<='1';

c<='0';

else b<='0';

c<='1';

end if;

end process;

end architecture number;

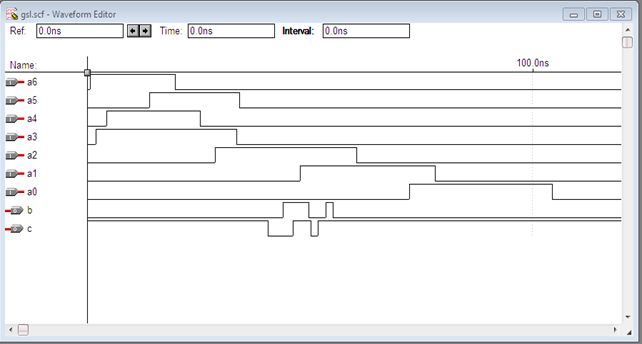

2、建立仿真波形文件,使用 MAXPLUS II Simulator功能进行功能仿真。

仿真结果如下:

3、目标器件选择与管脚锁定并重新编译、综合、适配。

FPGA型号:EP1K100QC208-3

引脚绑定:

4、下载并验证结果

将编译好的程序进行引脚锁定及硬件配置后便可下载到目标芯片中,我们将程序下载到芯片中后结果输出灯c亮b灭,当我们按下a0到a6任意四个或四个以上按键时c灭b亮,实验结果符合预期效果,结果正确。

四、实验结果与总结

我们这次EDA实验课设计了一个双LED灯输出七人表决器,实验结果符合预期效果即任意按下四个或四个以上按键表示同意,同意灯亮反对灯灭。通过这次实验使我首次接触到了FPGA的项目设计以及MAX PLUSⅡ的使用,使我更加深了对EDA这门课程的理解,并且初步学会了如何使用MAX PLUSⅡ进行VHDL语言编程以及将程序下载到芯片上,虽然过程中遇到了一些困难,但通过请教同学,最后都完美的解决了。我相信通过接下来几次试验,我一定能更加熟练地使用MAX PLUSⅡ,独立完成设计。

第二篇:EDA实验 七人表决器

河 北 科 技 大 学

实 验 报 告

20##级 电信专业 101 班 学号 13年4月1日

姓名 同组人 指导教师 于国庆

实验名称 实验一 七人表决器 成绩

实验类型 设计型 批阅教师

一、实验目的

(1)掌握MUXPLUS II语言输入的设计过程。

(2)初步了解VHDL语言。

(3)熟悉FPGA项目设计的基本流程。

二、实验原理:

用七个开关作为表决器的7个输入变量,输入变量为逻辑“1”时表示表决者“赞同”; 输入变量为逻辑“0”时表示表决者“不赞同”;输出逻辑“1”时,表示表决“通过”; 输出逻辑“0”时,表示表决“不通过”;当表决器的七个输入变量中有4个及以上为“1”时,则表决器输出为“1”,否则为“0”。

表决器输入采用试验箱K1~K16,输出采用试验箱L15、L16指示;同意红灯亮,否则黄灯亮。

三、实验内容及步骤

1.打开MUXPLUS II VHDL编辑器,完成七人表决器的设计。包括VHDL程序输入、编译、综合。

实验程序如下:

library ieee;

use ieee.std_logic_1164.ALL;

entity GSL is

port(a:in std_logic_vector(6 downto 0);

b:out std_logic;

c:out std_logic);

end entity GSL;

architecture number of GSL is

begin

process(a)

variable cnt:integer range 0 to 7;

begin cnt:=0;

for i in 6 downto 0 loop

if a(i)='1'then

cnt:=cnt+1;

end if;

end loop;

if cnt>3 then b<='1';

c<='0';

else b<='0';

c<='1';

end if;

end process;

end architecture number;

2、建立仿真波形文件,使用 MAXPLUS II Simulator功能进行功能仿真。

仿真结果如下:

3、目标器件选择与管脚锁定并重新编译、综合、适配。

FPGA型号:EP1K100QC208-3

引脚绑定:

4、下载并验证结果

将编译好的程序进行引脚锁定及硬件配置后便可下载到目标芯片中,我们将程序下载到芯片中后结果输出灯c亮b灭,当我们按下a0到a6任意四个或四个以上按键时c灭b亮,实验结果符合预期效果,结果正确。

四、实验结果与总结

我们这次EDA实验课设计了一个双LED灯输出七人表决器,实验结果符合预期效果即任意按下四个或四个以上按键表示同意同意灯亮反对灯灭。通过这次实验我们加深了对EDA这门课程的理解,学会了如何使用MAX PLUSⅡ进行VHDL语言编程以及将程序下载到芯片上,增加了对学习VHDL语言的兴趣,增强了实践动手能力,学到了许多课本上没有的知识。

- 三人表决器实验报告

-

三人表决器实验报告

技能实训三人表决器的逻辑电路设计与制作姓名班级日期课时成绩一实训目标1增强专业意识培养良好的职业道德和职业习惯2能借助资料读懂集成…

-

三人表决器实验报告

电子技术与仿真项目报告项目名称三人表决器的制作专业班级电气121姓名刘斌学号24指导教师张琴江西工业工程职业技术学院电工电子实训中…

-

三人表决器报告

项目一三人表决器的设计与装配实验报告姓名学号专业指导教师实训时间数字电子技术9月26日电子信息工程系20xx20xx学年第一学期设…

-

五人表决器实验报告——孙小喃

学生实验报告实验课名称VHDL硬件描述语言实验项目名称五人表决器专业名称电子科学与技术班学级320xx801号05学生姓名孙小喃教…

- 三人表决器实验报告

-

三人表决器实验报告

技能实训三人表决器的逻辑电路设计与制作姓名班级日期课时成绩一实训目标1增强专业意识培养良好的职业道德和职业习惯2能借助资料读懂集成…

-

三人表决器实验报告

电子技术与仿真项目报告项目名称三人表决器的制作专业班级电气121姓名刘斌学号24指导教师张琴江西工业工程职业技术学院电工电子实训中…

-

三人表决器报告

项目一三人表决器的设计与装配实验报告姓名学号专业指导教师实训时间数字电子技术9月26日电子信息工程系20xx20xx学年第一学期设…

-

五人表决器实验报告——孙小喃

学生实验报告实验课名称VHDL硬件描述语言实验项目名称五人表决器专业名称电子科学与技术班学级320xx801号05学生姓名孙小喃教…