实验一 组合逻辑电路的设计

实验一 组合逻辑电路的设计

一、实验目的:

1、 掌握组合逻辑电路的设计方法。

2、 掌握组合逻辑电路的静态测试方法。

3、 加深FPGA设计的过程,并比较原理图输入和文本输入的优劣。

4、 理解“毛刺”产生的原因及如何消除其影响。

5、 理解组合逻辑电路的特点。

二、实验的硬件要求:

1、 EDA/SOPC实验箱。

2、 计算机。

三、实验原理

1、组合逻辑电路的定义

数字逻辑电路可分为两类:组合逻辑电路和时序逻辑电路。组合逻辑电路中不包含记忆单元(触发器、锁存器等),主要由逻辑门电路构成,电路在任何时刻的输出只和当前时刻的输入有关,而与以前的输入无关。时序电路则是指包含了记忆单元的逻辑电路,其输出不仅跟当前电路的输入有关,还和输入信号作用前电路的状态有关。

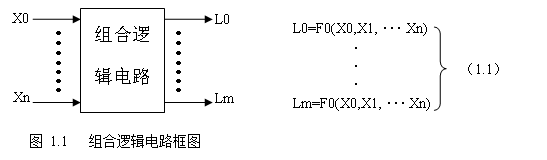

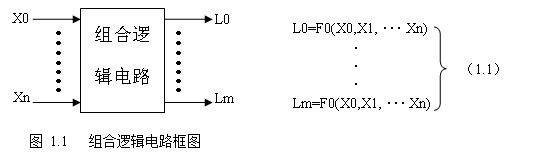

通常组合逻辑电路可以用图1.1所示结构来描述。其中,X0、X1、…、Xn 为输入信号, L0、L1、…、Lm为输出信号。输入和输出之间的逻辑函数关系可用式1.1表示:

2、组合逻辑电路的设计方法

组合逻辑电路的设计任务是根据给定的逻辑功能,求出可实现该逻辑功能的最合理组 合电路。理解组合逻辑电路的设计概念应该分两个层次:(1)设计的电路在功能上是完整的,能够满足所有设计要求;(2)考虑到成本和设计复杂度,设计的电路应该是最简单的,设计最优化是设计人员必须努力达到的目标。

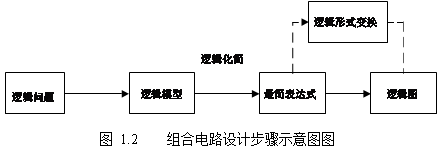

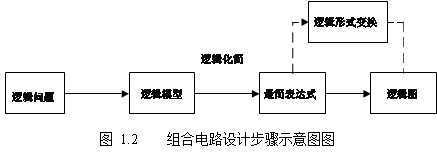

在设计组合逻辑电路时,首先需要对实际问题进行逻辑抽象,列出真值表,建立起逻辑模型;然后利用代数法或卡诺图法简化逻辑函数,找到最简或最合理的函数表达式;根据简化的逻辑函数画出逻辑图,并验证电路的功能完整性。设计过程中还应该考虑到一些实际的工程问题,如被选门电路的驱动能力、扇出系数是否足够,信号传递延时是否合乎要求等。组合电路的基本设计步骤可用图1.2来表示。

3、组合逻辑电路的特点及设计时的注意事项

①组合逻辑电路的输出具有立即性,即输入发生变化时,输出立即变化。(实际电路中还要考虑器件和导线产生的延时)。

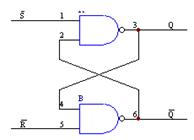

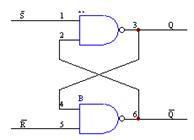

②组合逻辑电路设计时应尽量避免直接或间接的反馈,以免出现不确定的状态或形成振荡。如右图设计的基本触发器,当输入~S、~R从“00”变为“11”时,无法确定Q和~Q的值。

②组合逻辑电路设计时应尽量避免直接或间接的反馈,以免出现不确定的状态或形成振荡。如右图设计的基本触发器,当输入~S、~R从“00”变为“11”时,无法确定Q和~Q的值。

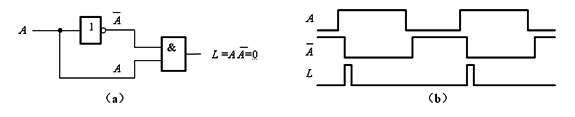

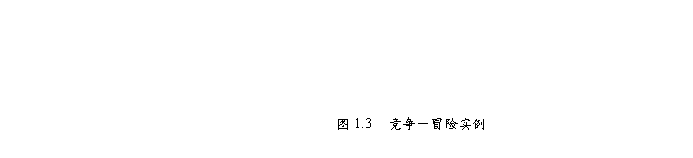

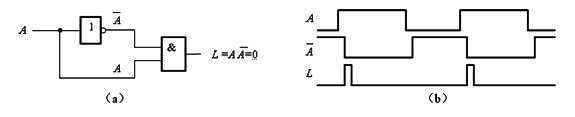

③组合逻辑电路容易出现“毛刺”,这是由于电路“竞争-冒险”产生的。如图1.3所示,图中与门的两个输入分别由信号 A 经过不同路径传递而来。按照理想情况分析,电路输出端应该始终为 L=A ·~A =0。考虑到信号在逻辑门中的传输延迟,~A 到达与门输入端的时间始终落后于 A。图 3.2-1(b)的波形显示,信号 A的四次变化都产生了竞争。但这四次竞争引起的结果是不一样的。第一次和第三次竞争造 成输出错误,第二次和第四次竞争则没有造成输出错误。换言之,只有第一次和第三次竞争引起了冒险,产生了尖峰干扰。

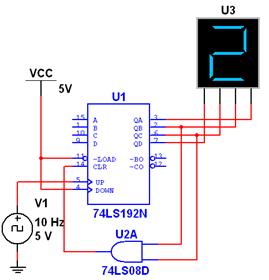

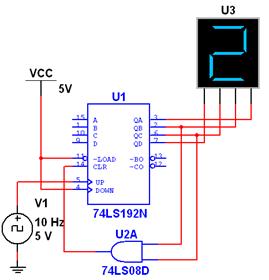

由于“毛刺”的影响,应避免使用组合逻辑电路直接产生时钟信号,也应避免将组合逻辑电路的输出作为另一个电路的异步控制信号。如右图,本意是设计一个计数范围为“0~5”的六进制计数器,即输出QD、QC、QB、QA从5“0101”变到6“0110”时,与门输出“1”,控制“CLR”异步复位到“0000”,但是由于输出从3“0011”变到4“0100”时,QC先于QB从“0”变到“1”,导致短暂的“0111”出现,使与门输出“1”,引起复位,从而使实际的电路计数范围为“0~3”,与设计的初衷相悖。

由于“毛刺”的影响,应避免使用组合逻辑电路直接产生时钟信号,也应避免将组合逻辑电路的输出作为另一个电路的异步控制信号。如右图,本意是设计一个计数范围为“0~5”的六进制计数器,即输出QD、QC、QB、QA从5“0101”变到6“0110”时,与门输出“1”,控制“CLR”异步复位到“0000”,但是由于输出从3“0011”变到4“0100”时,QC先于QB从“0”变到“1”,导致短暂的“0111”出现,使与门输出“1”,引起复位,从而使实际的电路计数范围为“0~3”,与设计的初衷相悖。

④用VHDL描述组合逻辑电路时,所有的输入信号都应放在敏感信号表中。

⑤用IF语句和CASE语句描述电路分支时,一定要列举出所有输入状态(一般在最后加上“else”或“when others”分支),否则在综合时将引入LATCH,使电路输出出现延时。

四、实验内容:

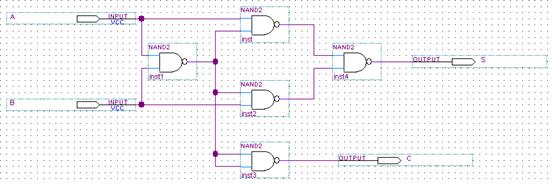

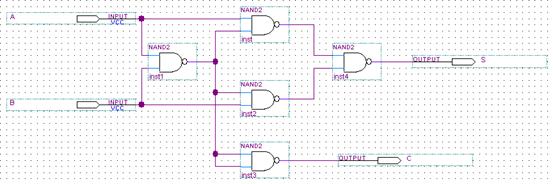

1、 用原理图方式设计1位二进制半加器半加器。

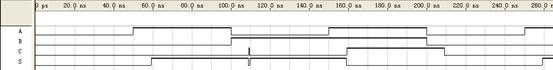

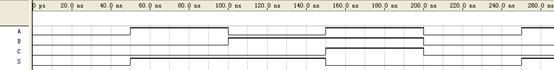

建立波形文件,对半加器电路分别进行时序仿真和功能仿真,其波形如下:

半加器时序仿真波形,注意观察输出延时,以及毛刺的产生原因

半加器功能仿真波形

用开关K1、K2输入A、B,用两个LED显示S和C。

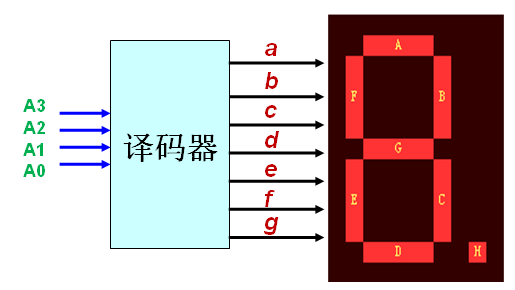

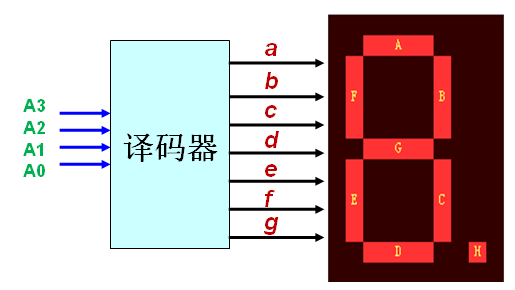

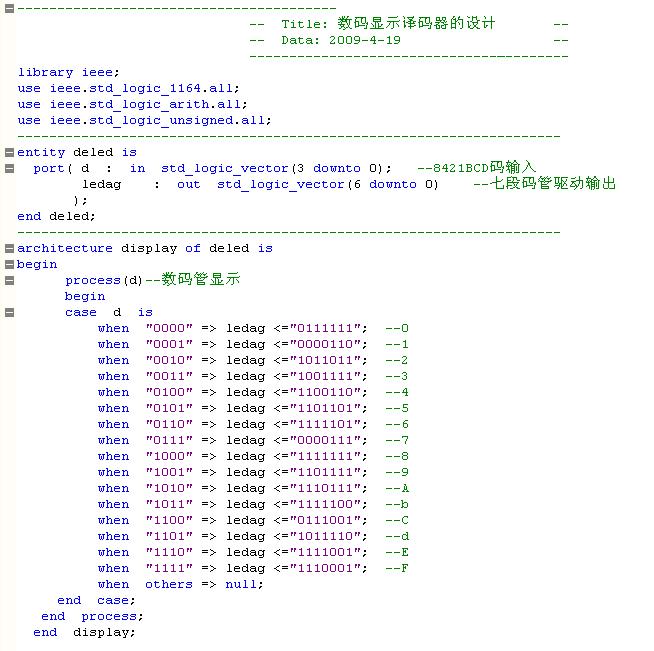

2、 设计BCD码译码器设计。

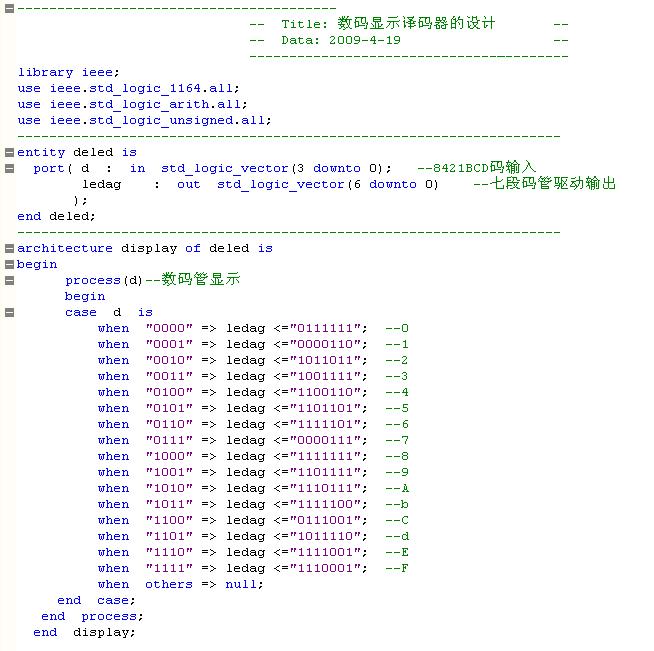

源码如下:

输入信号:D[3],D[2],D[1],D[0]所对应的管脚同四位拨码开关相连。

输出信号:代表7段字码驱动信号ledag[0]——ledag[6]的管脚分别同扫描数码管的段输入a,b,c,d,e,f,g相连。

使用数码管时注意设置“管脚复用”

3、 设计一个BCD码加法器。

BCD码是二进制编码的十进制码,也就是用4位二进制数来表示十进制中的0~9这十个数。由于4位二进制数有0000~1111共16种组合,而十进制数只需对应4位二进制数的10种组合,故从4位二进制数的16种组合中取出10种组合来分别表示十进制中的0~9,则有许多不同的取舍方式,于是便形成了不同类型的BCD码。

本实验我们只针对最简单的情况,也是最常见的BCD码,就是用4位二进制的0000~1001来表示十进制的0~9,而丢弃4位二进制的1010~1111共6种组合,这样一来,就相当于用4位二进制的0~9对应十进制的0~9。这样的BCD码进行相加时会出现两种可能,一种可能是当两个BCD码相加的值小于10时,结果仍旧是正确的BCD码;另外一种可能是当两个码相加的结果大于或者等于10时,就会得到错误的结果,这是因为4位二进制码可以表示0~15,而BCD码只取了其中的0~9的原因。对于第二种错误的情况,有一个简单的处理方法就是作加6处理,就会得到正确的结果。

下面举例说明第二种情况的处理过程。

假如A=(7)10=(0111)2=(0111)BCD,B=(8)10=(1000)2=(1000)BCD,那么A+B=(15)10=(1111)2≠(0001 0101)BCD。但是对于(1111)2+(0110)2=(0001 0101)2=(0010 0001)BCD。因此在程序设计时要注意两个输入的BCD码相加结果是否会出现大于或等于10的情况,如果是则必须作加6的修正处理。

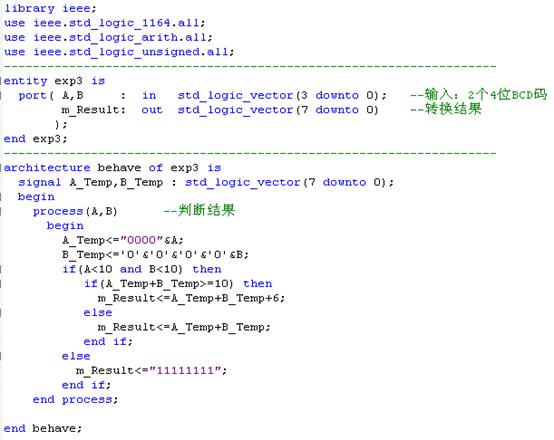

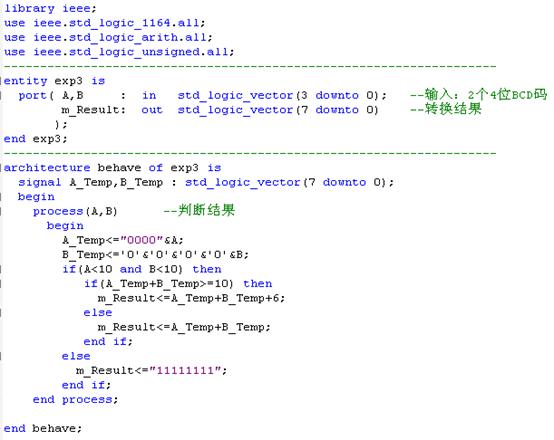

BCD码加法器的VHDL源码如下:

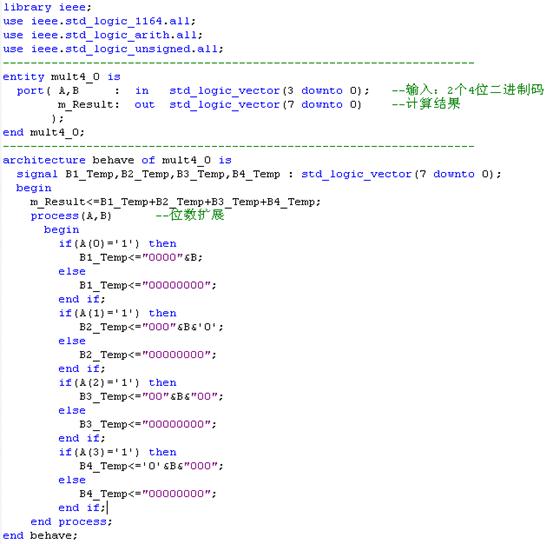

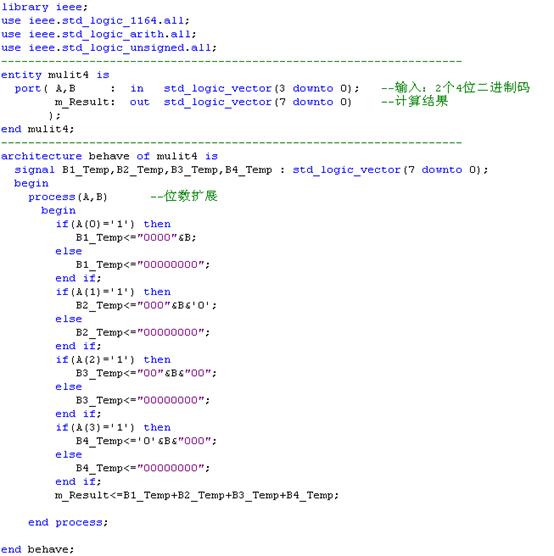

4、 设计一个4位硬件乘法器。

实现并行乘法器的方法有很多种,但是归结起来基本上分为两类,一类是靠组合逻辑电路实现,另一类通过流水线结构实现。组合逻辑电路结构的并行乘法器的最大优点就是速度快,但是当位数很大时占用的逻辑资源较多。下面就组合逻辑电路实现无符号数乘法的方法作详细介绍。

假如有被乘数A和乘数B,首先用A与B的最低位相乘得到S1,然后再把A左移1位与B的第2位相乘得到S2,再将A左移3位与B的第三位相乘得到S3,依此类推,直到把B的所有位都乘完为止,然后再把乘得的结果S1、S2、S3……相加即得到相乘的结果。

需要注意的是,具体实现乘法器是,并不是真正的去乘,而是利用简单的判断去实现,举个简单的例子。假如A左移n位后与B的第n位相乘,如果B的这位为‘1’,那么相乘的中间结果就是A左移n位后的结果,否则如果B的这位为‘0’,那么就直接让相乘的中间结果为‘0’即可。待B的所有位相乘结束后,把所有的中间结果相加即得到A与B相乘的结果。

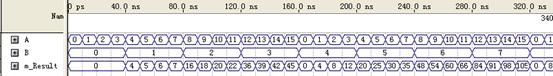

乘法器的功能仿真波形如下图(注意:三个端口数据类型设置为Unsigned Decimal),图中可以看出,乘法结构的输出没有延时(实际情况应有一定的器件延时,可以通过时序仿真看到)。

五、实验步骤:

1.首先打开Quartus II软件,新建工程。

2.按照自己的想法,编写原理图或VHDL文件程序。

3.对自己的设计进行编译并仿真。

4.仿真无误后,根据附录一的引脚对照表,对实验中用到的拨挡开关及LED进行管脚绑定,然后再重新编译一次。

5.用下载电缆通过JTAG接口将对应的sof文件下载到FPGA中。

6.观察实验结果是否与自己的预期想法相吻合。

7.二进制半加器半加器要求分别用时序仿真“Timing”和功能仿真“Function”观察仿真波形,说明“毛刺”出现的原因。其它实验只需进行功能仿真。

六、实验报告要求

1.总结组合逻辑电路的行为特点。

2.论述组合逻辑电路设计、分析和测试方法。

3. 分析“毛刺”产生的原因及如何消除其影响。

4.写出对于原理图和文本描述(VHDL)这两种设计输入方法的优劣心得。

第二篇:实验一 组合逻辑电路的设计

实验一 组合逻辑电路的设计

一、实验目的:

1、 掌握组合逻辑电路的设计方法。

2、 掌握组合逻辑电路的静态测试方法。

3、 加深FPGA设计的过程,并比较原理图输入和文本输入的优劣。

4、 理解“毛刺”产生的原因及如何消除其影响。

5、 理解组合逻辑电路的特点。

二、实验的硬件要求:

1、 EDA/SOPC实验箱。

2、 计算机。

三、实验原理

1、组合逻辑电路的定义

数字逻辑电路可分为两类:组合逻辑电路和时序逻辑电路。组合逻辑电路中不包含记忆单元(触发器、锁存器等),主要由逻辑门电路构成,电路在任何时刻的输出只和当前时刻的输入有关,而与以前的输入无关。时序电路则是指包含了记忆单元的逻辑电路,其输出不仅跟当前电路的输入有关,还和输入信号作用前电路的状态有关。

通常组合逻辑电路可以用图1.1所示结构来描述。其中,X0、X1、…、Xn 为输入信号, L0、L1、…、Lm为输出信号。输入和输出之间的逻辑函数关系可用式1.1表示:

2、组合逻辑电路的设计方法

组合逻辑电路的设计任务是根据给定的逻辑功能,求出可实现该逻辑功能的最合理组 合电路。理解组合逻辑电路的设计概念应该分两个层次:(1)设计的电路在功能上是完整的,能够满足所有设计要求;(2)考虑到成本和设计复杂度,设计的电路应该是最简单的,设计最优化是设计人员必须努力达到的目标。

在设计组合逻辑电路时,首先需要对实际问题进行逻辑抽象,列出真值表,建立起逻辑模型;然后利用代数法或卡诺图法简化逻辑函数,找到最简或最合理的函数表达式;根据简化的逻辑函数画出逻辑图,并验证电路的功能完整性。设计过程中还应该考虑到一些实际的工程问题,如被选门电路的驱动能力、扇出系数是否足够,信号传递延时是否合乎要求等。组合电路的基本设计步骤可用图1.2来表示。

3、组合逻辑电路的特点及设计时的注意事项

①组合逻辑电路的输出具有立即性,即输入发生变化时,输出立即变化。(实际电路中还要考虑器件和导线产生的延时)。

②组合逻辑电路设计时应尽量避免直接或间接的反馈,以免出现不确定的状态或形成振荡。如右图设计的基本触发器,当输入~S、~R从“00”变为“11”时,无法确定Q和~Q的值。

②组合逻辑电路设计时应尽量避免直接或间接的反馈,以免出现不确定的状态或形成振荡。如右图设计的基本触发器,当输入~S、~R从“00”变为“11”时,无法确定Q和~Q的值。

③组合逻辑电路容易出现“毛刺”,这是由于电路“竞争-冒险”产生的。如图1.3所示,图中与门的两个输入分别由信号 A 经过不同路径传递而来。按照理想情况分析,电路输出端应该始终为 L=A ·~A =0。考虑到信号在逻辑门中的传输延迟,~A 到达与门输入端的时间始终落后于 A。图 3.2-1(b)的波形显示,信号 A的四次变化都产生了竞争。但这四次竞争引起的结果是不一样的。第一次和第三次竞争造 成输出错误,第二次和第四次竞争则没有造成输出错误。换言之,只有第一次和第三次竞争引起了冒险,产生了尖峰干扰。

由于“毛刺”的影响,应避免使用组合逻辑电路直接产生时钟信号,也应避免将组合逻辑电路的输出作为另一个电路的异步控制信号。如右图,本意是设计一个计数范围为“0~5”的六进制计数器,即输出QD、QC、QB、QA从5“0101”变到6“0110”时,与门输出“1”,控制“CLR”异步复位到“0000”,但是由于输出从3“0011”变到4“0100”时,QC先于QB从“0”变到“1”,导致短暂的“0111”出现,使与门输出“1”,引起复位,从而使实际的电路计数范围为“0~3”,与设计的初衷相悖。

由于“毛刺”的影响,应避免使用组合逻辑电路直接产生时钟信号,也应避免将组合逻辑电路的输出作为另一个电路的异步控制信号。如右图,本意是设计一个计数范围为“0~5”的六进制计数器,即输出QD、QC、QB、QA从5“0101”变到6“0110”时,与门输出“1”,控制“CLR”异步复位到“0000”,但是由于输出从3“0011”变到4“0100”时,QC先于QB从“0”变到“1”,导致短暂的“0111”出现,使与门输出“1”,引起复位,从而使实际的电路计数范围为“0~3”,与设计的初衷相悖。

④用VHDL描述组合逻辑电路时,所有的输入信号都应放在敏感信号表中。

⑤用IF语句和CASE语句描述电路分支时,一定要列举出所有输入状态(一般在最后加上“else”或“when others”分支),否则在综合时将引入LATCH,使电路输出出现延时。

四、实验内容:

1、 用原理图方式设计1位二进制半加器半加器。

用开关K1、K2输入A、B,用两个LED显示S和C。

2、 设计一个BCD码加法器。

BCD码是二进制编码的十进制码,也就是用4位二进制数来表示十进制中的0~9这十个数。由于4位二进制数有0000~1111共16种组合,而十进制数只需对应4位二进制数的10种组合,故从4位二进制数的16种组合中取出10种组合来分别表示十进制中的0~9,则有许多不同的取舍方式,于是便形成了不同类型的BCD码。

本实验我们只针对最简单的情况,也是最常见的BCD码,就是用4位二进制的0000~1001来表示十进制的0~9,而丢弃4位二进制的1010~1111共6种组合,这样一来,就相当于用4位二进制的0~9对应十进制的0~9。这样的BCD码进行相加时会出现两种可能,一种可能是当两个BCD码相加的值小于10时,结果仍旧是正确的BCD码;另外一种可能是当两个码相加的结果大于或者等于10时,就会得到错误的结果,这是因为4位二进制码可以表示0~15,而BCD码只取了其中的0~9的原因。对于第二种错误的情况,有一个简单的处理方法就是作加6处理,就会得到正确的结果。

下面举例说明第二种情况的处理过程。

假如A=(7)10=(0111)2=(0111)BCD,B=(8)10=(1000)2=(1000)BCD,那么A+B=(15)10=(1111)2≠(0001 0101)BCD。但是对于(1111)2+(0110)2=(0001 0101)2=(0010 0001)BCD。因此在程序设计时要注意两个输入的BCD码相加结果是否会出现大于或等于10的情况,如果是则必须作加6的修正处理。

BCD码加法器的VHDL源码如下:

3、 设计BCD码译码器设计。

源码如下:

输入信号:D[3],D[2],D[1],D[0]所对应的管脚同四位拨码开关相连。

输出信号:代表7段字码驱动信号ledag[0]——ledag[6]的管脚分别同扫描数码管的段输入a,b,c,d,e,f,g相连。

使用数码管时注意设置“管脚复用”

4、 设计一个4位硬件乘法器。

实现并行乘法器的方法有很多种,但是归结起来基本上分为两类,一类是靠组合逻辑电路实现,另一类通过流水线结构实现。组合逻辑电路结构的并行乘法器的最大优点就是速度快,但是当位数很大时占用的逻辑资源较多。下面就组合逻辑电路实现无符号数乘法的方法作详细介绍。

假如有被乘数A和乘数B,首先用A与B的最低位相乘得到S1,然后再把A左移1位与B的第2位相乘得到S2,再将A左移3位与B的第三位相乘得到S3,依此类推,直到把B的所有位都乘完为止,然后再把乘得的结果S1、S2、S3……相加即得到相乘的结果。

需要注意的是,具体实现乘法器是,并不是真正的去乘,而是利用简单的判断去实现,举个简单的例子。假如A左移n位后与B的第n位相乘,如果B的这位为‘1’,那么相乘的中间结果就是A左移n位后的结果,否则如果B的这位为‘0’,那么就直接让相乘的中间结果为‘0’即可。待B的所有位相乘结束后,把所有的中间结果相加即得到A与B相乘的结果。

五、实验步骤:

1.首先打开Quartus II软件,新建工程。

2.按照自己的想法,编写原理图或VHDL文件程序。

3.对自己的设计进行编译并仿真。

4.仿真无误后,根据附录一的引脚对照表,对实验中用到的拨挡开关及LED进行管脚绑定,然后再重新编译一次。

5.用下载电缆通过JTAG接口将对应的sof文件下载到FPGA中。

6.观察实验结果是否与自己的预期想法相吻合。

7.二进制半加器半加器要求分别用时序仿真“Timing”和功能仿真“Function”观察仿真波形,说明“毛刺”出现的原因。其它实验只需进行功能仿真。

六、实验报告要求

1.总结组合逻辑电路的行为特点。

2.论述组合逻辑电路设计、分析和测试方法。

3. 分析“毛刺”产生的原因及如何消除其影响。

4.写出对于原理图和文本描述(VHDL)这两种设计输入方法的优劣心得。

-

组合逻辑电路实验报告

实验报告课程名称:数字电子技术基础实验指导老师:樊**成绩:实验名称:组合逻辑电路实验实验类型:设计类同组学生姓名:一、实验目的和…

-

组合逻辑电路的设计实验报告

广西大学实验报告纸实验内容指导老师实验名称组合逻辑电路的设计实验目的学习组合逻辑电路的设计与测试方法设计任务用四二输入与非门设计一…

- 电子技术实验报告4—组合逻辑电路的设计与测试

-

组合逻辑电路的设计及半加器、全加器

实验四组合逻辑电路的设计及半加器全加器一实验目的1掌握组合逻辑电路的设计与测试方法2掌握半加器全加器的工作原理二实验原理和电路1组…

-

《组合逻辑电路的设计》的实验报告

实验五组合逻辑电路的设计一实验目的学习组合逻辑电路的设计与测试方法二实验用仪器仪表数字电路实验箱万用表74LS00三设计任务设计一…

-

实验1 门电路功能测试及组合逻辑电路设计

实验1门电路功能测试及组合逻辑电路设计1实验目的1掌握常用门电路的逻辑功能及测试方法2掌握用小规模集成电路设计组合逻辑电路的方法2…

-

实验二 组合逻辑电路分析与设计

信息工程学院数字逻辑与数字系统实验实习报告学院信息工程学院班级信息111姓名朱伟定学号20xx013259成绩实验二组合逻辑电路分…

-

实验二 组合逻辑电路分析与设计.

实验一实验目的组合逻辑电路分析与设计1掌握组合逻辑电路的分析方法与测试方法2掌握组合逻辑电路的设计方法二实验预习要求1熟悉门电路工…

- 电子技术实验报告4—组合逻辑电路的设计与测试

-

组合逻辑电路的分析与设计-实验报告

组合逻辑电路的分析与设计实验报告院系电子与信息工程学院班级电信132班组员姓名盖兵134xxxxxxxx邢帅成134xxxxxxx…

-

组合逻辑电路实验报告

实验报告课程名称:数字电子技术基础实验指导老师:樊**成绩:实验名称:组合逻辑电路实验实验类型:设计类同组学生姓名:一、实验目的和…