组合逻辑电路的设计及半加器、全加器

实验四 组合逻辑电路的设计及半加器、全加器

一、实验目的

1. 掌握组合逻辑电路的设计与测试方法

2.掌握半加器、全加器的工作原理。

二、实验原理和电路

1、组合逻辑电路的设计

使用中、小规模集成电路来设计组合电路是最常见的逻辑电路。设计

组合电路的一般步骤如图1.4.1所示。

图1.4.1 组合逻辑电路设计流程图

根据设计任务的要求建立输入、输出变量,并列出真值表。然后用逻辑代数或卡诺图化简法求出简化的逻辑表达式。并按实际选用逻辑门的类型修改逻辑表达式。 根据简化后的逻辑表达式,画出逻辑图,用标准器件构成逻辑电路。最后,用实验来验证设计的正确性。

1.半加器

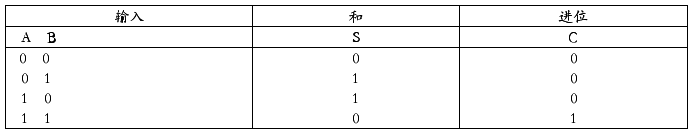

根据组合电路设计方法,首先列出半加器的真值表,见表1.4.1。

写出半加器的逻辑表达式

S=AB+AB=A?B

S=AB+AB=A?B

C=AB

若用“与非门”来实现,即为

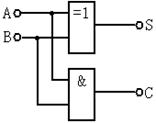

半加器的逻辑电路图如图1.4.2所示。

在实验过程中,我们可以选异或门74LS86及与门74LS08实现半加器的逻辑功能;也可用全与非门如74LS00反相器74LS04组成半加器。

(a)用异或门组成的半加器 (b)用与非门组成的半加器

图1.4.2 半加器逻辑电路图

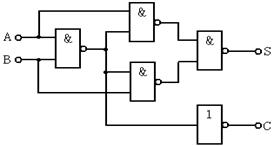

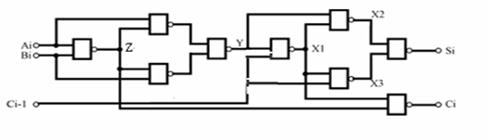

2.全加器

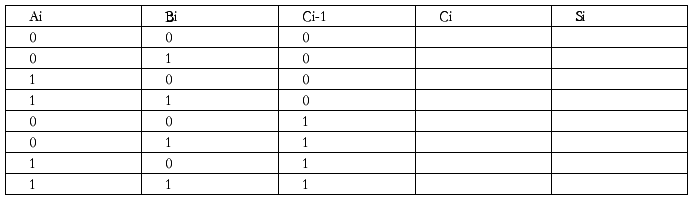

用上述两个半加器可组成全加器,原理如图1.4.3所示。

图1.4.3由二个半加器组成的全加器 表1.4.2 全加器逻辑功能表

表1.4.1 半加器逻辑功能

三、实验内容及步骤

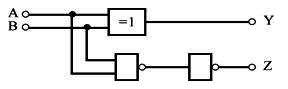

1.测试用异或门(74LS86)和与非门组成的半加器的逻辑功能。

根据半加器的逻辑表达式可知,相加的和Y是A、B的异或,而进位Z是A、B相与,故半加器可用一个集成异或门和二个与非门组成如图1.4.4。

图1.4.4 用一个集成异或门和二个与非门组成半加器

⑴ 在实验仪上用异或门和与门接成以上电路。A、B接逻辑开关,Y、Z接发光二极管显示。

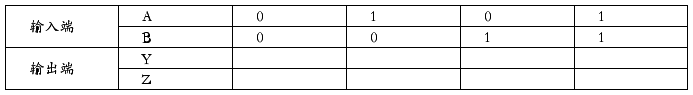

⑵ 按表1.4.3要求改变A、B状态,将相加的和Y和进位Z的状态填入下表中。

表1.4.3

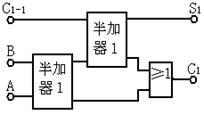

2.测试全加器的逻辑功能。

⑴写出图1.4.5电路的逻辑表达式。S = C

= C =

=

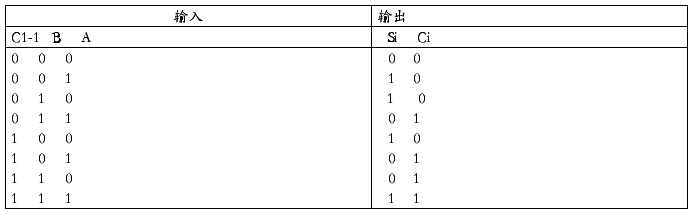

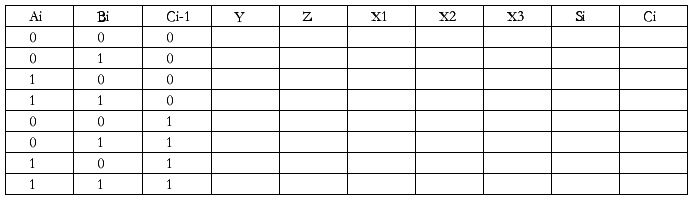

⑵根据逻辑表达式列真值表,并完成表1.4.4,实验证之。

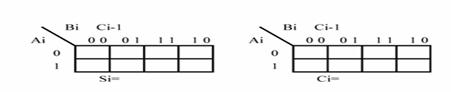

⑶根据真值表画逻辑函数SiCi的卡诺图。完成图1.4.6

图 1.4.5

图 1.4.6

表1.4.4

⑸ 试设计用异或门、与门、或门组成的全加器的逻辑功能并接线进行测试,将测试结果记入表1.4.5中,与上表进行比较看逻辑功能是否一致。

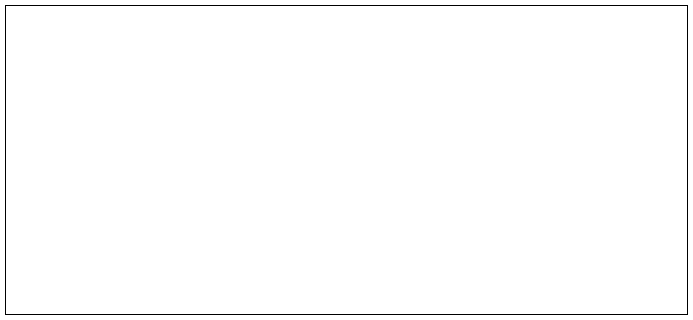

设计要求按组合逻辑电路设计流程图所述的设计步骤进行,直到测试电路逻辑功能符合设计要求为止。

表1.4.5

设计过程及设计的逻辑电路图写入方框中:

四、实验器材

1.数字电子技术实验系统 1台

2.直流稳压电源 1台

3.集成电路:74LS00 3片

74LS86,74LS32, 74LS08 各1片

五、预习要求

1. 根据实验任务要求设计组合电路,并根据所给的标准器件画出逻辑图。

2. 复习半加器、全加器工作原理和特点。

3. 了解本实验中所用集成电路的逻辑功能和使用方法。

六、实验报告要求

1.列写实验任务的设计过程,画出设计的逻辑电路图。

2.对所设计的电路进行实验测试,记录测试结果。

3.组合电路设计体会。

第二篇:基础实验二、 组合逻辑电路(半加器全加器及逻辑运算)

基础实验二、 组合逻辑电路(半加器全加器及逻辑运算)一、 实验目的1. 掌握组合逻辑电路的功能侧试。2. 验证半加器和全加器的逻辑功。3. 学会二进制数的运算规律。二、 实验仪器及材料器件74LS00 二输入端四与非门 3片 74LS86 二输入端四异或门 1片 74LS54 四组输入与或非门 1片三、 预习要求1. 预习组合逻辑电路的分析方法。2. 预习用与非门和异或门构成的半加器、全加器的工作原理。3. 预习二进制数的运算。四、 实验内容1. 组合逻辑电路功能测试。(1)用2片74 LS00组成图2. 1所示逻辑电路,为便于接线和检查,在图中要注明芯片编号及各引脚对应的编号。(2)图中A、B、C接电平开关,Y1.Y2接发光管电平显示。(3)按表2.1要求,改变A、B、C的状态填表并写出Y1.Y2逻辑表达式。(4)将运算结果与实验比较。2. 测试用异或门(74LS86)和与非门组成的半加器逻辑功能。根据半加器的逻辑表达式可知,半加器Y是A、B的异或,而进位Z是A、B相与,故半加器可用一个集成异或门和二个与非门组成如图2.2。(1) 在学习机上用异或门和与门接成以上电路.A、B接电平开关S.Y,Z接电平显示。(2) 按表2.2要求改变A、B状态,填表。3. 测试全加器的逻辑功能(1)写出图2.3电路的逻辑表达式。(2)根据逻辑表达式列真值表。(3)根据真值表画逻辑函数Si、Ci的卡诺图。(5)按原理图选择与非门并接线进行测试,将测试结果记入表2.4,并与上表进行比较看逻辑功能是否一致4. 测试用异或、与非和非门组成的全加器的逻辑功能。全加器可以用两个半加器和两个与门一个或门组成,在实验中,常用一块双异或门、一个与或门和一个与非门实现。(1)画出用异或门、与或非门和非门实现全加器的逻辑电路图,写出逻辑表达式。(2)找出异或门、与或非门和与门器件按自己画出的图接线。接线时注意与或非门中不用的与门输入端接地。(3)当输入端Ai、Bi及Ci-1为下列情况时,用万用表测量Si和Ci的电位并将其转为逻辑状态 填入表。五、 实验报告1. 整理实验数据、图表并对实验结果进行分析讨论。2. 总结组合逻辑电路的分析方法。2

-

组合逻辑电路实验报告

实验报告课程名称:数字电子技术基础实验指导老师:樊**成绩:实验名称:组合逻辑电路实验实验类型:设计类同组学生姓名:一、实验目的和…

-

组合逻辑电路的设计实验报告

广西大学实验报告纸实验内容指导老师实验名称组合逻辑电路的设计实验目的学习组合逻辑电路的设计与测试方法设计任务用四二输入与非门设计一…

- 电子技术实验报告4—组合逻辑电路的设计与测试

-

组合逻辑电路的设计及半加器、全加器

实验四组合逻辑电路的设计及半加器全加器一实验目的1掌握组合逻辑电路的设计与测试方法2掌握半加器全加器的工作原理二实验原理和电路1组…

-

《组合逻辑电路的设计》的实验报告

实验五组合逻辑电路的设计一实验目的学习组合逻辑电路的设计与测试方法二实验用仪器仪表数字电路实验箱万用表74LS00三设计任务设计一…

-

组合逻辑电路实验报告

实验报告课程名称:数字电子技术基础实验指导老师:樊**成绩:实验名称:组合逻辑电路实验实验类型:设计类同组学生姓名:一、实验目的和…

-

实验二 组合逻辑电路分析与设计

信息工程学院数字逻辑与数字系统实验实习报告学院信息工程学院班级信息111姓名朱伟定学号20xx013259成绩实验二组合逻辑电路分…

-

实验二 组合逻辑电路分析与设计.

实验一实验目的组合逻辑电路分析与设计1掌握组合逻辑电路的分析方法与测试方法2掌握组合逻辑电路的设计方法二实验预习要求1熟悉门电路工…

- 电子技术实验报告4—组合逻辑电路的设计与测试

-

实验二 组合逻辑电路分析与设计

实验二组合逻辑电路分析与设计一、实验目的1.掌握组合逻辑电路的分析方法与测试方法;2.掌握组合逻辑电路的设计方法。二、实验预习要求…

-

组合逻辑电路实验报告

甘肃政法学院本科生实验报告组合逻辑电路的设计姓名学院专业班级实验课程名称数字电子技术基础实验日期指导教师及职称实验成绩开课时间甘肃…