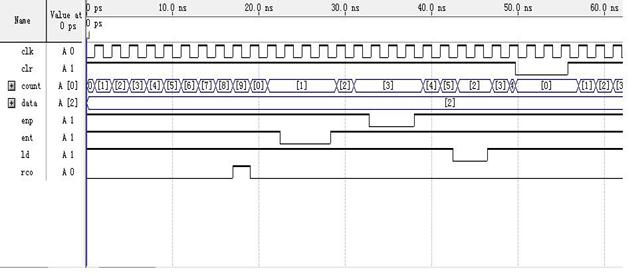

集成电路设计实验报告

第二篇:专用集成电路设计实验报告

专用集成电路设计实验报告

班 级:

学 号:

姓 名:

指导教师:

2011.07.04

一、74160功能:

① 异步清零

当 =0时,不管其他输入端的状态如何(包括时钟信号CP ),

=0时,不管其他输入端的状态如何(包括时钟信号CP ),

计数器输出将被直接置零,称为异步清零。

② 同步并行预置数

在 =1的条件下,当

=1的条件下,当 =0、且有时钟脉冲CLK 的上升沿作用时,A、B、C、D 输入端的数据将分别被QA~QD所接收。由于这个置数操作要与CLK上升沿同步,且DA、DB、DC、DD的数据同时置入计数器,所以称为同步并行置数。

=0、且有时钟脉冲CLK 的上升沿作用时,A、B、C、D 输入端的数据将分别被QA~QD所接收。由于这个置数操作要与CLK上升沿同步,且DA、DB、DC、DD的数据同时置入计数器,所以称为同步并行置数。

③ 保持

在 =

= =1的条件下,当ENT=ENP=0,即两个计数使能端中有0时,不管有无CP 脉冲作用,计数器都将保持原有状态不变(停止计数)。需要说明的是,当ENP=0, ENT=1时,进位输出C也保持不变;而当ENT=0时,不管ENP状态如何,进位输出RCO=0。

=1的条件下,当ENT=ENP=0,即两个计数使能端中有0时,不管有无CP 脉冲作用,计数器都将保持原有状态不变(停止计数)。需要说明的是,当ENP=0, ENT=1时,进位输出C也保持不变;而当ENT=0时,不管ENP状态如何,进位输出RCO=0。

④ 计数

当 =

= =ENP=ENT=1时,74160处于计数状态。

=ENP=ENT=1时,74160处于计数状态。

这种同步可预置十进计数器是由四个D 型触发器和若干个门电路构成,内部有超前进位,具有计数、置数、禁止、直接(异步)清零等功能。对所有触发器同时加上时钟,使得当计数使能输入和内部门发出指令时输出变化彼此协调一致而实现同步工作。这种工作方式消除了非同步(脉冲时钟)计数器中常有的输出计数尖峰。缓冲时钟输入将在时钟输入上升沿触发四个触发器。

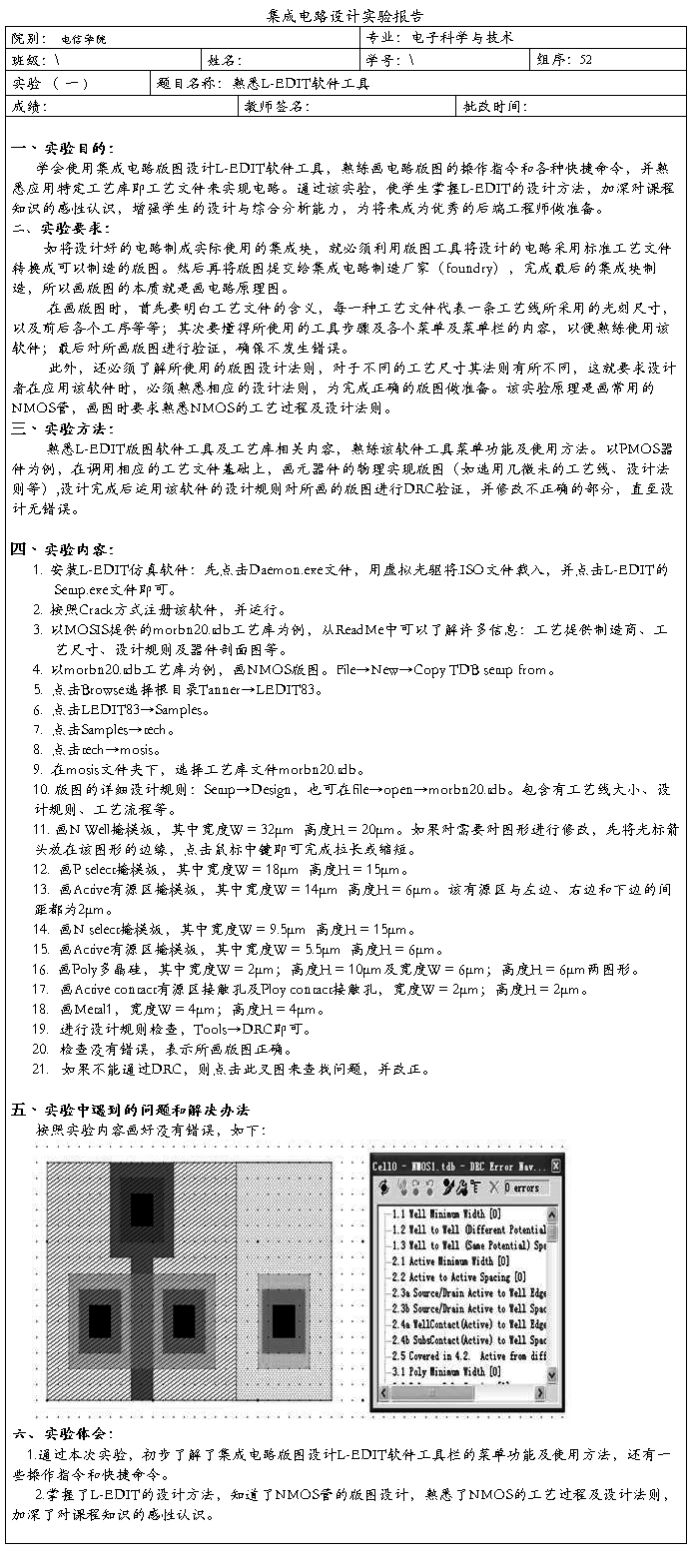

74LS160时序图:

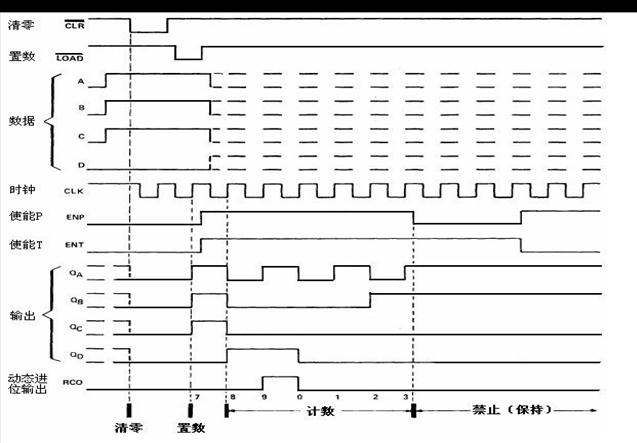

真值表:

二、用VHDL进行功能仿真

1、程序:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

ENTITY LS160 IS PORT(

data:IN std_logic_vector(3 downto 0);

clk,ld,enp,ent,clr:IN std_logic;

count:buffer std_logic_vector(3 downto 0);

rco:OUT std_logic); END LS160;

ARCHITECTURE behavior OF LS160 IS

BEGIN

rco<='1'when(count="1001"and enp='1'and ld='1'and clr='1')else'0'; PROCESS(clk,clr,enp,ent,ld)

BEGIN

IF(CLR='0')THEN count<="0000";

ELSIF(clk'event and clk='1')THEN

IF(ld='1')THEN

IF(enp='1')THEN

IF(ent='1')THEN

IF(count="1001")THEN

count<="0000"; ELSE

count<=count+1; END IF;

ELSE

count<=count;

END IF;

ELSE

count<=count;

END IF;

ELSE

count<=data;

END IF;

end if;

END PROCESS;

END behavior;

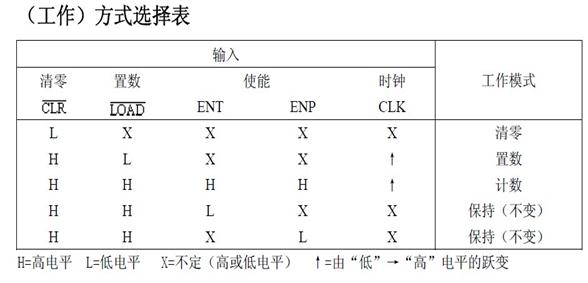

2、仿真波形:

-

集成门电路功能测试实验报告

集成门电路功能测试实验报告一实验预习1逻辑值与电压值的关系2常用逻辑门电路逻辑功能及其测试方法3硬件电路基础实验箱的结构基本功能和…

- 集成电路设计实验报告

-

集成运算放大电路实验报告

韶关学院-电子技术基础实验与课程设计实验报告实验项目名称:运算放大器基本放大电路院系(学号):物理与机电工程学院专业:姓名:学号:…

-

集成电路综合实验报告

集成电路设计综合实验实验报告学院电气与控制工程学院班级姓名学号1完成日期目录一实验要求2二实验目的2三实验内容2一版图提出电路并分…

-

西工大数字集成电路实验报告 数集实验2(1)

实验二反相器上一分析电路解答下面的问题1这个电路是不是反相器为什么该门属于有比逻辑还是无比逻辑为什么是因为当Vin1时下拉网络导通…

-

浙大版电工电子学实验报告12集成运算放大器及应用(一)模拟信号运算电路

课程名称电工电子学实验指导老师实验名称集成运算放大器及应用一模拟信号运算电路实验报告一实验目的1了解集成运算放大器的基本使用方法和…

-

电路实验报告

数字电路实验报告姓名:***学号:***学院:信息学院专业:计算机科学与技术指导教师:***协助指导教师:20XX年12月28日实…

-

数字电路实验报告4

暨南大学本科实验报告专用纸课程名称数字逻辑电路实验成绩评定实验项目名称中规模集成电路功能测试及应用指导教师实验项目编号080600…

-

西工大数电实验报告_实验一TTL集成逻辑门电路参数测试

实验一TTL集成逻辑门电路参数测试姓名同组一实验目的1加深了解TTL逻辑门的参数意义2掌握TTL逻辑门电路的主要参数及测量方法3认…

-

集成门电路功能测试实验报告

集成门电路功能测试实验报告一实验预习1逻辑值与电压值的关系2常用逻辑门电路逻辑功能及其测试方法3硬件电路基础实验箱的结构基本功能和…

-

dsp课程设计实验报告总结

DSP课程设计总结(20##-20##学年第2学期)题目:专业班级:电子1103学生姓名:学号:指导教师:设计成绩:20##年6月…