实验四38译码器实验(王赟)

本科学生综合性实验报告

学号 094090xxx 姓名 王 赟

学院 物电学院 专业、班级 物理09物理D班 实验课程名称 数电实验 教师及职称 张超 开课学期 至 填报时间年月日

云南师范大学教务处编印

第二篇:实验四 译码器

实验名称:组合逻辑VHDL设计----译码器

班级:09通信1 学号:09811106 姓名:顾礼萍

一、用WITH-SELECT语句实现2-4译码器

1.实体框图

2.程序设计

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY DECODER24B IS

PORT(A1,A0:IN STD_LOGIC;

Y:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

END ENTITY DECODER24B;

ARCHITECTURE ONE OF DECODER24B IS

SIGNAL S: STD_LOGIC_VECTOR(1 DOWNTO 0);

BEGIN

S<=A1&A0;

WITH S SELECT

Y<="1110" WHEN"00",

"1101" WHEN"01",

"1011" WHEN"10",

"0111" WHEN"11",

"ZZZZ" WHEN OTHERS;

END ARCHITECTURE ONE;

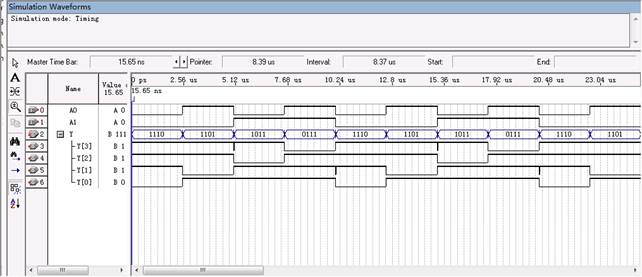

3.仿真波形图

4.仿真波形分析

二、用WITH-SELECT语句实现带使能端的3-8译码器

1.实体框图

2.程序设计

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY DECODER38B IS

PORT(A2,A1,A0:IN STD_LOGIC;

S3,S2,S1:IN STD_LOGIC;

Y:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END ENTITY DECODER38B;

ARCHITECTURE ONE OF DECODER38B IS

SIGNAL G: STD_LOGIC_VECTOR(4DOWNTO 0);

BEGIN

G<=S1&(S2 AND S3)&A2&A1&A0;

WITH G SELECT

Y<="11111110" WHEN"10000",

"11111101" WHEN"10001",

"11111011" WHEN"10010",

"11110111" WHEN"10011",

"11101111" WHEN"10100",

"11011111" WHEN"10101",

"10111111" WHEN"10110",

"01111111" WHEN"10111",

"ZZZZZZZZ" WHEN OTHERS;

END ARCHITECTURE ONE;

3.仿真波形图

4.仿真波形分析

三、用WITH-SELECT语句实现驱动共阳极数码管七段显示译码器

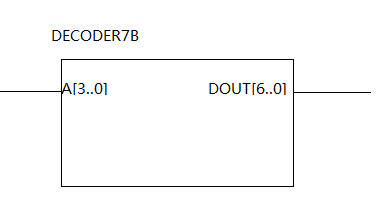

1.实体框图

2.程序设计

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY DECODER7B IS

PORT(A:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

DOUT:OUT STD_LOGIC_VECTOR(6 DOWNTO 0)

END ENTITY DECODER7B;

ARCHITECTURE ONE OF DECODER7B IS

SIGNAL S: STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

S<=A3&A2&A1&A0;

WITH S SELECT

Y<="1111111" WHEN"0000",

"1111001" WHEN"0001",

"0100100" WHEN"0010",

"0110000" WHEN"0011",

"0011001" WHEN"0100",

"0010010" WHEN"0101",

"0000010" WHEN"0110",

"1111000" WHEN"0111",

"0000000" WHEN"1000",

"0010000" WHEN"1001",

"ZZZZZZZ" WHEN OTHERS;

END ARCHITECTURE ONE;

3.仿真波形图

4.仿真波形分析

思考题

1. 设计共阴极七段显示译码器。

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY DECODER7B IS

PORT(A:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

DOUT:OUT STD_LOGIC_VECTOR(6 DOWNTO 0)

END ENTITY DECODER7B;

ARCHITECTURE ONE OF DECODER7B IS

SIGNAL S: STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

S<=A3&A2&A1&A0;

WITH S SELECT

Y<="0000000" WHEN"0000",

"0000110" WHEN"0001",

"1011011" WHEN"0010",

"1001111" WHEN"0011",

"1100110" WHEN"0100",

"1101101" WHEN"0101",

"1111101" WHEN"0110",

"0000111" WHEN"0111",

"1111111" WHEN"1000",

"1101111" WHEN"1001",

"ZZZZZZZ" WHEN OTHERS;

END ARCHITECTURE ONE;

2. 设计2进制变换为格雷码的码制变换译码器。

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

ENTITY DECODDER 7C IS

GENERIC(n:INTEGER :=4);

PORT(

NORM : IN STD_LOGIC_VECTOR(N-1 DOWNTO 0);

GREY: OUT STD_LOGIC_VECTOR(N-1 DOWNTO 0));

END ENTITY DECODDER 7C ;

ARCHITECTURE ONE OF DECODDER 7C IS

SIGNAL TEMP_NORMAL: STD_LOGIC_VECTOR(N-1 DOWNTO 0);

SIGNAL TEMP_GREY : STD_LOGIC_VECTOR(N-1 DOWNTO 0);

BEGIN

PROCESS(NORM)

BEGIN

TEMP_NORMAL <= NORM;

TEMP_GREY(n-1) <=TEMP_NORMAL(N-1)

FOR I IN N-2 DOWNTO 0 LOOP

TEMP_GREY(I) <= TEMP_NORMAL(I+1) XOR TEMP_NORMAL(I);

END LOOP;

GREY <= TEMP_GREY;

END PROCESS;

END ONE;

-

实验四38译码器实验(王赟)

本科学生综合性实验报告学号094090xxx姓名王赟学院物电学院专业班级物理09物理D班实验课程名称数电实验教师及职称张超开课学期…

- 3-8译码器的设计实验报告

-

译码器实验报告

课程编号深圳大学实验报告课程名称数字电路实验名称译码器学院信息工程学院指导教师刘静报告人李金梁组号03学号20xx130025实验…

-

实验一 38译码器

实验一38译码器的设计一实验目的1掌握MAXplus软件的使用方法2重点掌握原理图的编辑和仿真方法3通过38译码器的设计掌握利用E…

-

数字电路译码器实验报告

一实验目的与要求1了解和正确使用MSI组合逻辑部件2掌握一般组合逻辑电路的特点及分析设计方法3学会对所设计的电路进行静态功能测试的…

-

数字电路实验二--译码器实验报告深圳大学--郭治民

深圳大学实验报告实验课程名称数字电路与逻辑设计实验项目名称学院计算机与软件学院专业计算机科学与技术报告人同组人指导教师实验时间实验…

-

译码器实验报告

课程编号深圳大学实验报告课程名称数字电路实验名称译码器学院信息工程学院指导教师刘静报告人李金梁组号03学号20xx130025实验…

-

译码器实验报告

深圳大学实验报告课程名称学院计算机与软件学院班级实验时间实验报告提交时间教务部制深圳大学学生实验报告用纸注1报告内的项目或内容设置…

-

译码器实验报告

数字电路逻辑与设计实验报告姓名刘凯班级0401206学号20xx211791实验名称译码器及其应用实验目的123掌握数码管的使用方…

-

译码器实验报告

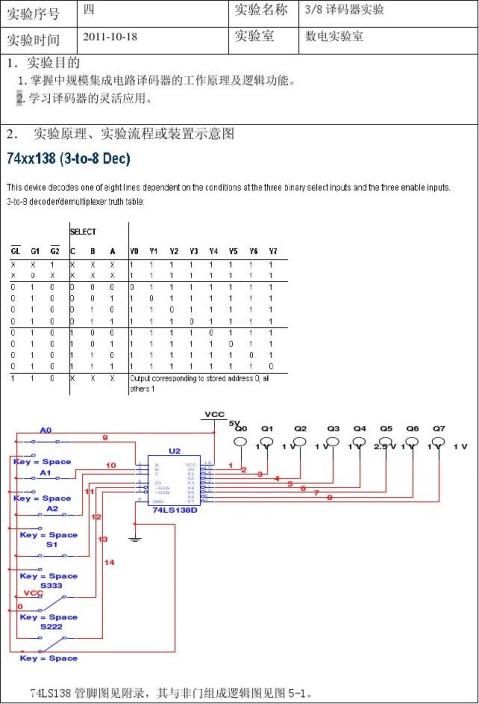

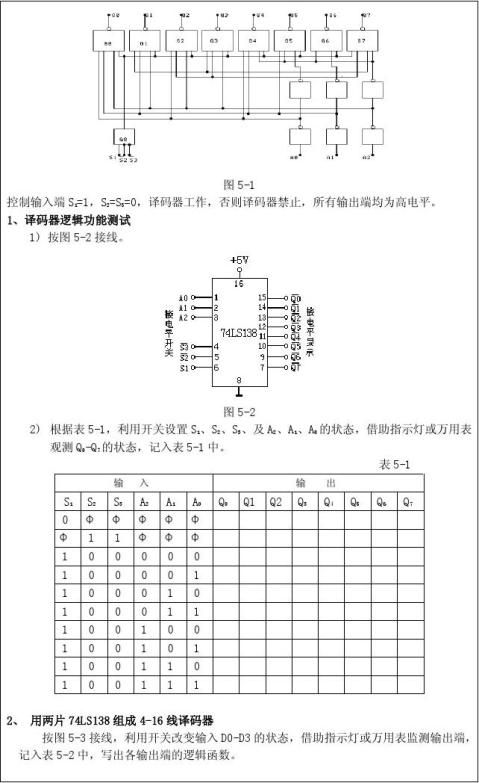

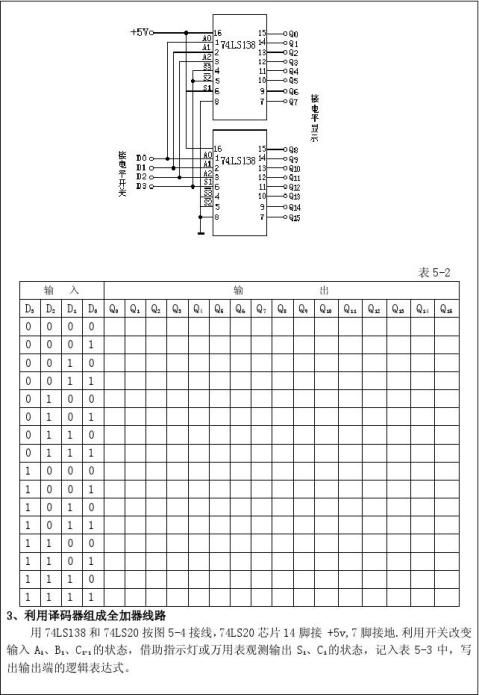

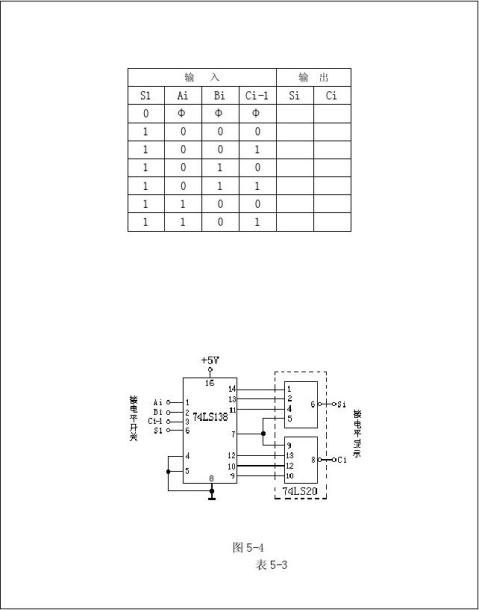

实验2译码器及其应用一实验目的1掌握中规模集成译码器的逻辑功能和使用方法2熟悉数码管的使用二实验原理译码器是一个多输入多输出的组合…

-

译码器实验报告

数字逻辑实验报告院系数学与计算机学院专业计算机类4班姓名田恒学号1305110089指导教师刘昌华实验题目译码器的EDA设计实验目…