FPGA_三人投票表决器实验报告

实验报告

一. 实验名称

三人投票表决器的实现

二. 实验目的

1) 熟练掌握QUARTUSII的操作方法

2) 了解VHDL程序书写基本语法规则

3) 熟悉原理图绘制的方法

4) 学会波形仿真验证结果

三. 实验原理

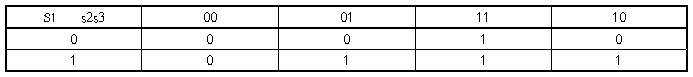

设开关状态0,1代表三人投票情况s1,s2,s3,二极管的亮灭代表投票结果win,lose。画卡诺图(表1):

表格 1

化简卡诺图得:win=s1s2+s2s3+s1s3

则:lose=~win

四. 实验过程

1) 创建工程

2) 新建VHDL文件,输入程序,结果见图表1:

图表 1

3) 编译工程,查看RTL,见图表2

图表 2

4) 创建波形仿真文件,设置s1,s2,s3的波形,进行仿真,查看结果见图表3:

图表 3

5)投票表决器除了可以用VHDL语言实现外还可以用原理图进行实现,见图表4:

图表 4

5) 用原理图法的实现接下来步骤同3)、4)

6) 引脚分配

7) 下载到试验箱,看结果

五. 实验总结

注意事项:

1) 修改完成VHDL文件或原理图文件后在进行下一步之前要对整个工程进行编译构建

2) 在波形仿真的时候选择好每个引脚的波形后按波形仿真按钮而不是编译按钮

3) 在同一个工程下各个新建文件必须与工程同名

第二篇:三人表决器实验报告

武汉纺织大学

数字逻辑 实验报告

数计 系 计算机 专业 102 班 1004681083

姓名 鲍旭良 指导老师 曾西洋 实验日期 2012年6月

实验名称 三人表决器

-

三人表决器实验报告

技能实训三人表决器的逻辑电路设计与制作姓名班级日期课时成绩一实训目标1增强专业意识培养良好的职业道德和职业习惯2能借助资料读懂集成…

-

三人表决器实验报告

电子技术与仿真项目报告项目名称三人表决器的制作专业班级电气121姓名刘斌学号24指导教师张琴江西工业工程职业技术学院电工电子实训中…

-

三人表决器报告

项目一三人表决器的设计与装配实验报告姓名学号专业指导教师实训时间数字电子技术9月26日电子信息工程系20xx20xx学年第一学期设…

-

五人表决器实验报告——孙小喃

学生实验报告实验课名称VHDL硬件描述语言实验项目名称五人表决器专业名称电子科学与技术班学级320xx801号05学生姓名孙小喃教…

-

FPGA_三人投票表决器实验报告

实验报告一实验名称三人投票表决器的实现二实验目的1234熟练掌握QUARTUSII的操作方法了解VHDL程序书写基本语法规则熟悉原…

- 三人表决器实验报告

-

三人表决器实验报告

技能实训三人表决器的逻辑电路设计与制作姓名班级日期课时成绩一实训目标1增强专业意识培养良好的职业道德和职业习惯2能借助资料读懂集成…

-

三人表决器实验报告

电子技术与仿真项目报告项目名称三人表决器的制作专业班级电气121姓名刘斌学号24指导教师张琴江西工业工程职业技术学院电工电子实训中…

-

三人表决器报告

项目一三人表决器的设计与装配实验报告姓名学号专业指导教师实训时间数字电子技术9月26日电子信息工程系20xx20xx学年第一学期设…

-

五人表决器实验报告——孙小喃

学生实验报告实验课名称VHDL硬件描述语言实验项目名称五人表决器专业名称电子科学与技术班学级320xx801号05学生姓名孙小喃教…