一位半加器实验报告

实验一 1位半加器

一、 实验目的

熟悉利用QuartusⅡ的原理图输入方法设计简单组合电路,并掌握其设计方法和软件的应用

二、 实验原理:

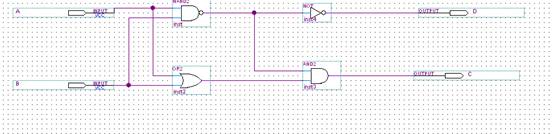

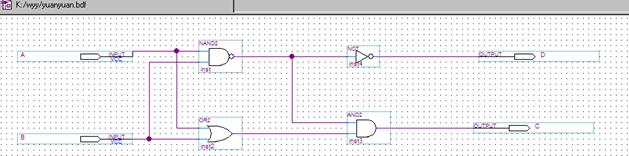

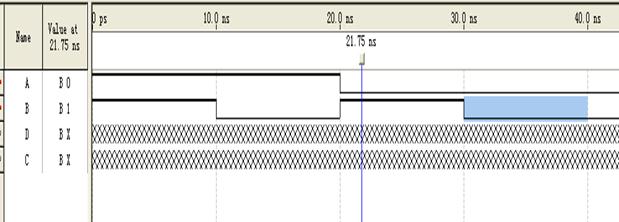

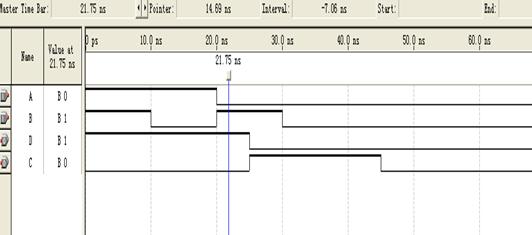

1位半加器可以由与、或、非等基本门构成,如下图所示。

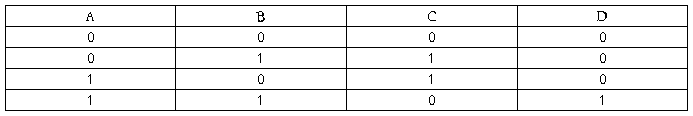

半加器的真值表中两个输入是加数A和B,输出有一个是C,另一个是D。

三、 实验内容

按半加器的原理图完成输入、编译,然后进行仿真。

四、 步骤

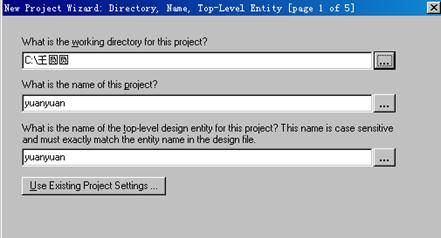

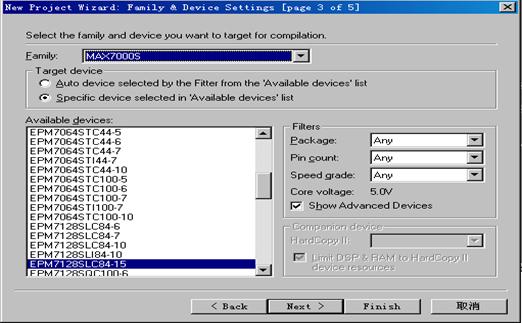

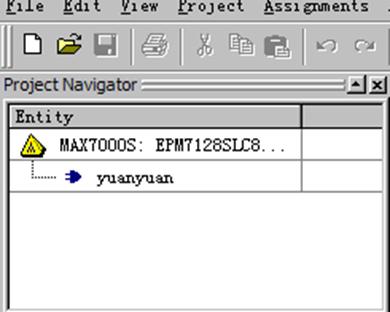

1、 项目的新建

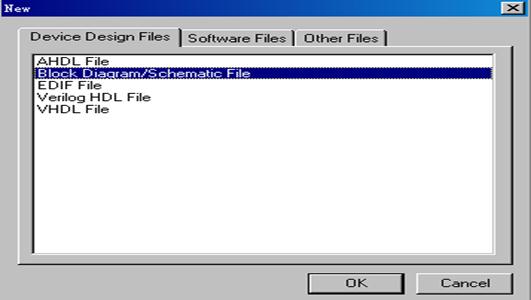

2、 半加器的原理图设计

3、 编译

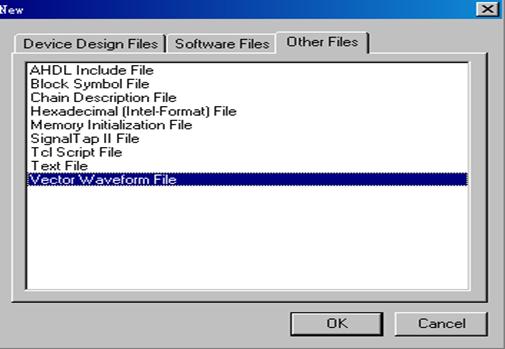

4、 仿真

仿真要设置仿真结束时间,波形编辑器默认的仿真结束时间为1µS,根据仿真需要,可以自由设置仿真的结束时间。选择QUARTUSII软件的Edit>End Time命令,弹出线路束时间对话框,在Time框办输入仿真结束时间,点击OK按钮完成设置。

5、仿真结果

五、实验心得

通过本次实验,我进一步熟悉了QuartusII5.0 软件的使用,并进一步学习了一些对基本时序电路器件进行描述和仿真,还复习了数字电路中的一些基本知识,相信对于以后本课程的学习及实验会有很大的好处。

第二篇:半加器和全加器

-

一位半加器实验报告

实验一1位半加器一实验目的熟悉利用Quartus的原理图输入方法设计简单组合电路并掌握其设计方法和软件的应用二实验原理1位半加器可…

-

Quartus II半加器实验报告

CPLD/FPGA设计实验报告实验一半加器一、创建工程工程名称:adder顶层实体文件名:adder器件:EP1C12Q240C8…

-

半加器EDA上机实验报告

ED姓名学号班级专业学院A上机实验报告集成电路工程类半加器设计实验1实验目的练习半加器的VHDL程序设计以及功能仿真2实验任务参考…

-

半加器和D触发器实验报告

VHDL硬件描述语言实验实验内容报告1半加器2D触发器半加器实验原理quot和quot与quot进位quot根据半加器的逻辑表达式…

-

数电实验报告半加全加器

实验二半加减器与全加减器一实验目的1掌握全加器和半加器的逻辑功能2熟悉集成加法器的使用方法3了解算术运算电路的结构二实验设备174…

-

半加器和D触发器实验报告

VHDL硬件描述语言实验实验内容报告1半加器2D触发器半加器实验原理quot和quot与quot进位quot根据半加器的逻辑表达式…

-

一位全加器VHDL的设计实验报告

EDA技术及应用实验报告一位全加器VHDL的设计班级XXX姓名XXX学号XXX一位全加器的VHDL设计一实验目的1学习MAXPLU…

-

全加器实验报告

数电实验报告二组合逻辑电路半加器全加器及逻辑运算一实验目的1掌握组合逻辑电路的功能测试2验证半加器和全加器的逻辑功能3学会二进制数…

-

一位全加器的实验报告

专业班级20xx级电子2班学号1020xx07姓名周娟EDA技术实验报告实验项目名称在QuartusII中用原理图输入法设计1位加…

-

实验八全加器的设计分析实验报告

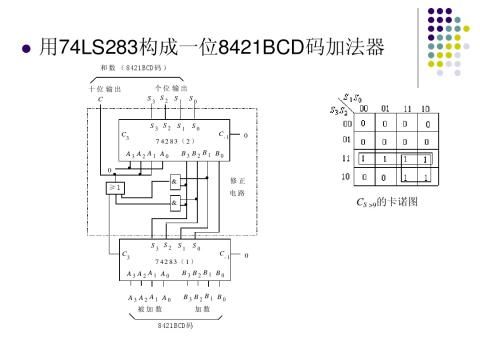

实验八全加器的设计分析实验报告姓名孙时佳3110102935学号同组学生姓名无专业计算机科学与技术课程名称逻辑与计算机设计基础实验…