数字系统设计与Verilog HDL实验报告(一)

《数字系统设计与Verilog HDL》

实验报告(一)

班级:自动1003班

姓名: 刘洋

学号: 06101103

实验一、ModelSim认识及四位比较器

一、 实验目的

1、了解及掌握ModelSim软件的基本功能;

2、通过ModelSim软件编写基本的程序进行仿真和调试。

二、 实验内容

1、熟悉ModelSim软件中各部分的功能及用法;

2、编写一个四位比较器设计程序以及测试该模块的测试程序,要求如下:

(1)输入两个四位二进制数a、b;

(2)若a<b,则输出LA_out=0,EQ_out=0,LE_out=1;

若a=b,则输出LA_out=0,EQ_out=1,LE_out=0;

若a>b,则输出LA_out=1,EQ_out=0,LE_out=0;

三、 实验步骤及源程序

新建工程及文件,分别添加设计程序及测试程序,进行编译及纠错,编译通过后运行程序仿真进行调试得出结果。

设计模块:

module compare4(LA_out,EQ_out,LE_out,a,b,LA_in,EQ_in,LE_in);

output LA_out,EQ_out,LE_out;

input [3:0] a,b;

input LA_in,EQ_in,LE_in;

reg LA_out,EQ_out,LE_out;

always @(b)

begin

if(a>b)

begin

LA_out=1'b1;

EQ_out=1'b0;

LE_out=1'b0;

end

else if(a<b)

begin

LA_out=1'b0;

EQ_out=1'b0;

LE_out=1'b1;

end

else

begin

if({LA_in,EQ_in,LE_in}==3'b100)

begin

LA_out=1'b1;

EQ_out=1'b0;

LE_out=1'b0;

end

else if({LA_in,EQ_in,LE_in}==3'b001)

begin

LA_out=1'b0;

EQ_out=1'b0;

LE_out=1'b1;

end

else if({LA_in,EQ_in,LE_in}==3'b010)

begin

LA_out=1'b0;

EQ_out=1'b1;

LE_out=1'b0;

end

end

end

endmodule

测试模块:

`timescale 10ns/1ns

module compare_top;

wire LA_out,EQ_out,LE_out;

reg [3:0] a,b;

reg LA_in,EQ_in,LE_in;

integer i,j;

compare4 cmp1(LA_out,EQ_out,LE_out,a,b,LA_in,EQ_in,LE_in);

initial

begin

a<=4'd0;

b<=4'd1;

end

always

begin

#5 {LA_in,EQ_in,LE_in}=3'b100;

#5 {LA_in,EQ_in,LE_in}=3'b001;

#5 {LA_in,EQ_in,LE_in}=3'b010;

end

initial

begin

for(i=0;i<16;i=i+1)

for(j=0;j<16;j=j+1)

begin

#5 a=i;b=j;

end

end

endmodule

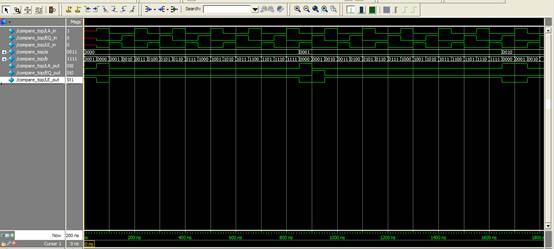

四、 实验结果

五、 实验心得体会

这回是我们第一次的实验,由于实验室准备的不够充分,所以我们大部分时间都在安装实验所要用到的软件,做实验的时间就不多了,所以对实验环境人是不是很到位,对实验有一定的影响,但由于第一次实验老师讲解的比较详细,所以我准备的也很充分,顺利的在有限的时间里完成了实验。

第二篇:数字系统设计与Verilog HDL实验报告(五)

《数字系统设计与Verilog HDL》

实验报告(五)

班级:自动1003班

姓名: 刘洋

学号: 06101103

实验五、自动售饮料机系统设计

一、 实验目的

1、了解及掌握状态机的基本构成用法;

2、通过ModelSim软件编写程序,用状态机可以编程设计简单的自动控制系统。

二、 实验内容

设计一个自动售饮料机。假定每瓶饮料售价为2.5元,可使用两种硬币,即5角和1元,机器有找零功能。

机器设计有2个投币孔,可用2个按键来代替。还设有2个输出孔,分别输出饮料和找零,提示用户取走饮料和零钱。

三、 实验步骤及源程序

新建工程及文件,分别添加设计程序及测试程序,进行编译及纠错,编译通过后运行程序仿真进行调试得出结果。

设计模块:

module sell(yi_yuan,wu_jiao, get,half_out,sell_out,reset,clk);

parameter idle=0, half=1, one=2,two=3,three=4;

input yi_yuan,wu_jiao,reset,clk;

output get,half_out,sell_out;

reg get,half_out,sell_out;

reg[2:0] s;

always @(posedge clk)

begin

if(reset)

begin

sell_out=0; get=0; half_out=0; s=idle;

end

else

case(s)

idle: begin

sell_out=0; get=0; half_out=0;

if(wu_jiao) s=half;

else if(yi_yuan)s=one;

end

half: begin

if(wu_jiao) s=one;

else if(yi_yuan)

s=two;

end

one: begin

if(wu_jiao) s=two;

else if(yi_yuan)s=three;

end

two: begin

if(wu_jiao) s=three;

else if(yi_yuan)

begin

sell_out=1;get=1; s=idle;

end

end

three: begin

if(wu_jiao)

begin

sell_out=1; get=1; s=idle;

end

else if(yi_yuan)

begin

sell_out=1;get=1;half_out=1; s=idle;

end

end

default:begin

sell_out=0; get=0; half_out=0; s=idle;

end

endcase

end

endmodule

测试模块:

`timescale 1ns/1ns

module sell_top;

reg yi_yuan,wu_jiao,reset,CLK;

wire get,half_out,sell_out;

always #50 CLK=~CLK;

initial

begin

CLK =0; reset=1;

#100 reset=0;

yi_yuan=0;

wu_jiao=0;

end

always@(posedge CLK)

begin

wu_jiao={$random}%2;#50 wu_jiao=0;

end

always@(posedge CLK)

begin

if(!wu_jiao)yi_yuan=1;#50 yi_yuan=0;

end

sell m(.yi_yuan(yi_yuan),.wu_jiao(wu_jiao), .get(get),

.half_out(half_out),.sell_out(sell_out),.reset(reset),.clk(CLK));

endmodule

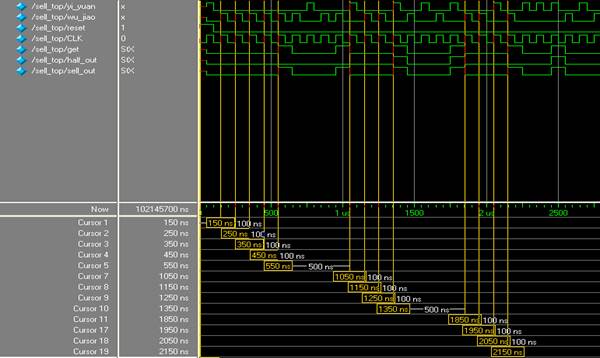

四、 实验结果

五、 实验心得体会

由于老师在实验前已经很详细的为我们讲解了这次实验的要点和要注意的问题,所以这次实验我们完成的还是很成功的。虽然实验中也遇到了一些问题,但通过多次实验积累的经验,我们已经可以很快的解决了。这也是最后一次实验了,通过这学期的学习,我关于这门课有了很大的收获,对我以后的学习和工作将会有巨大的帮助。

-

数字系统设计综合实验报告

数字系统设计综合实验报告实验名称1加法器设计2编码器设计3译码器设计4数据选择器设计5计数器设计6累加器设计7交通灯控制器设计班级…

-

东北大学数字系统设计实验报告

数字系统设计实验报告姓名学号计数器设计实验1实验目的1学习计数器不同设计方法2学习掌握VHDL中不同输出类型在具体应用时的区别OU…

-

复杂数字系统设计实验报告

复杂数字系统设计实验报告光学与光学工程系王启星物理学院SA15038040一实验标题多功能数字种的设计二实验目的任务和要求1数字系…

-

PLD与数字系统设计实验报告

PLD与数字系统设计实验报告A组实验四数字密码锁1实验要求使用Xilinx公司的Spartan3S400AN开发板上的相关模块利用…

-

数字系统设计与Verilog HDL实验报告(一)

数字系统设计与VerilogHDL实验报告一班级自动1003班姓名刘洋学号06101103实验一ModelSim认识及四位比较器一…

-

北航verilog实验报告

北京航空航天大学电子电路设计数字部分实验报告实验一简单组合逻辑设计2实验二简单分频时序逻辑电路的设计3一实验目的1掌握最基本组合逻…

-

Verilog期末实验报告—波形发生器

深圳大学实验报告课程名称:Verilog使用及其应用实验名称:频率可变的任意波形发生器学院:电子科学与技术学院专业:电子科学与技术…

-

verilog四位BCD加法器实验报告

1实验目的进一步熟悉modelsim仿真工具的使用方法学会设计验证的方法和流程编写一个4位BCD加法器并且用modelsim对其仿…

-

Verilog HDL 实验报告

实验一Modelsim仿真软件的使用一实验目的1熟悉Modelsim软件2掌握Modelsim软件的编译仿真方法3熟练运用Mode…

-

verilog电子钟实验报告

深圳大学实验报告课程名称硬件描述语言与逻辑综合实验项目名称电子时钟VerilogHDL的设计与仿真学院电子科学与技术学院专业微电子…

-

南昌大学数字钟设计实验报告

数字电路与逻辑设计实验实验报告题目学院信息工程学院系电子信息工程专业班级学号学生姓名同组同学指导教师递交日期23页第1页共南昌大学…